# DEVICE-CIRCUIT CO-DESIGN EMPLOYING PHASE TRANSITION MATERIALS FOR LOW POWER ELECTRONICS

by

Ahmedullah Aziz

## A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

School of Electrical & Computer Engineering West Lafayette, Indiana August 2019

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Sumeet Kumar Gupta, Chair

School of Electrical and Computer Engineering

Dr. Anand Raghunathan

School of Electrical and Computer Engineering

Dr. Kaushik Roy

School of Electrical and Computer Engineering

Dr. Zhihong Chen

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis Head of the Graduate Program Dedicated to my wife and my parents for their unconditional love and support.

## ACKNOWLEDGMENTS

First, I would like to express my heartfelt gratitude to my Ph.D. advisor, Prof. Sumeet Gupta, whose extraordinary mentorship was crucial in making this dissertation possible. I am greatly indebted to him for his kind support and encouragement throughout my graduate life. I genuinely admire his kind intention to infuse creativity in the minds of his students. His supervision and guidance helped me shape my research aptitude and strengthened my confidence. His cordial and thoughtful suggestions were instrumental in my professional and academic development. I cannot thank him enough for the countless hours he spent to ensure my academic progress and psychological wellbeing. Working under his supervision has been a privilege for me.

Next, I would like to thank the members of my doctoral dissertation committee: Prof. Anand Raghunathan, Prof. Kaushik Roy, and Prof. Zhihong Chen. Their valuable suggestions and constructive feedback helped me shape my doctoral research and refine this dissertation. I am also thankful to Prof. Suman Datta (University of Notre Dame), Prof. Vijaykrishnan Narayanan (Pennsylvania State University), Prof. Nikhil Shukla (University of Virginia), and Prof. Muhammad Ashraful Alam (Purdue University) for helping me with their valuable suggestions, insights and expert opinions on different topics of my research. I am grateful to Dr. Zoran Krivokapic and Dr. Srinivasa Banna for supervising my research during my internship at the GlobalFoundries (Fab 8), USA.

I would also like to thank my valued colleagues at Integrated Circuits and Devices Lab (ICDL), Purdue University, for their relentless encouragement. This work would not have been possible without help and support from my collaborators from Microsystems Design Lab (MDL), Penn State and Nanoelectronic Devices and Circuits Lab (NDCL), University of Notre Dame. I sincerely acknowledge the valuable support from Mr. Srivatsa Rangachar Srinivasa (Penn State), Ms. Sumitha George (Penn State), Ms. Shreya Gupta (Intel), Mr. Nicholas Jao (Penn State), Dr. Xueqing Li (Tsinghua University), Dr. Matthew Jerry (Micron) and Dr. Julien Frougier (GlobalFoundries).

I would like to acknowledge funding support from the following sources:

- Semiconductor Research Corporation (SRC) Global Research Collaboration (GRC) Program

- Center for Low Energy Systems Technology (LEAST), one of the six SRC STARnet Centers, sponsored by MARCO and DARPA

- New Materials for Logic, Memory and Interconnects (NEWLIMITS), a center in nCORE, a Semiconductor Research Corporation (SRC) program sponsored by NIST

- Defense Advanced Research Projects Agency (DARPA) Young Faculty Award (YFA) Grant

Finally, and perhaps most importantly, I would like to express my sincere gratitude to my family and friends for their endless support. My father, Mr. Mohammad Aziz Hossain, and mother, Mrs. Telat Ara Begum, left no stones unturned to support and help me in every stage of my life. I do not have words to thank them enough for their selfless love and lifelong sacrifices. They taught me to dream big and aim high. My mother gave me tremendous emotional support after the sudden death of my father. Without her steadfast support, I might not have had started my graduate studies in the first place. I would also like to thank my loving wife, Mrs. Sadia Binte Sohid, for her sacrifices and encouraging support to help me prosper. She took an equal share of all the hurdles and challenges of life to help me stay focused. I am grateful to Mrs. Shephali Mahajan for treating my wife and me as part of the family. I will never forget her warm and encouraging support.

This dissertation would not have come to reality, without help and contributions from so many people. I could not list all of them here, but I will always remain indebted to all of the well-wishers who helped me pursue my dream.

## TABLE OF CONTENTS

| LIST  | OF TABLES                                             | X     |

|-------|-------------------------------------------------------|-------|

| LIST  | OF FIGURES                                            | xi    |

| ABST  | TRACT                                                 | xxii  |

| 1. II | NTRODUCTION                                           | 1     |

| 1.1   | Device-Circuit Co-design for Exploratory Technologies | 1     |

| 1.2   | Phase Transition Materials (PTM)                      | 3     |

| 1.3   | Contributions of this Dissertation                    | 6     |

| 2. T  | THRESHOLD SWITCH AUGMENTED STT MRAM                   | 8     |

| 2.1   | Introduction                                          | 8     |

| 2.2   | Modeling and Simulation Framework                     | 10    |

| 2.3   | Principle of Operation                                | 11    |

| 2.4   | Design Approach for TSA MRAM                          | 13    |

| 2.    | .4.1 Biasing Constraints                              | 13    |

| 2.    | .4.2 Transient Aspects of TSA MRAM Operation          | 16    |

| 2.    | .4.3 Optimization of Performance Metrics with Biasing |       |

| 2.5   | Tuning Design Space with TS Parameters                | 23    |

| 2.6   | Variation Analysis                                    | 24    |

| 2.    | .6.1 Effect of Variation on Read Performance          | 25    |

| 2.    | .6.2 Effect of Variation on Write Performance         | 27    |

| 2.7   | Effect of Transition Time                             |       |

| 2.8   | Layout Aware Array Design                             | 29    |

| 2.9   | Discussion on Endurance and Thermal Stability         |       |

| 2.10  | O Summary                                             |       |

| 3. P  | PHASE TRANSITION MATERIAL AUGMENTED MRAM WITH SEPA    | ARATE |

| R     | READ-WRITE PATHS                                      |       |

| 3.1   | Introduction                                          |       |

| 3.2   | Cell Structure and Simulation Framework               |       |

| 3.3   | Principle of Operation                                |       |

| 3.4   | Design Methodology                                    | 37    |

| 3.5         | Tra   | insient Response                                      | 39 |

|-------------|-------|-------------------------------------------------------|----|

| 3.6         | Tu    | ning the Region of Operation                          | 40 |

| 3.7         | Eff   | ect of Design Parameters                              | 41 |

| 3.8         | Are   | ea Implications                                       | 43 |

| 3.9         | Su    | nmary                                                 | 43 |

| 4. <i>A</i> | ANAI  | LYSIS OF PHASE TRANSITION MATERIAL BASED SELECTORS FO | )R |

| (           | CROS  | S-POINT ARRAY                                         | 44 |

| 4.1         | Inti  | roduction                                             | 44 |

| 4.2         | Bas   | sic Description of a Cross-Point Array                | 46 |

| 4.3         | Bia   | sing Schemes for Cross-Point Array                    | 48 |

| 4.4         | De    | sign Constraints in a Cross-Point Array               | 51 |

| 4.5         | De    | sign Parameters and Simulation Framework              | 54 |

| 4.6         | Sel   | ector Design and Material Requirements                | 58 |

| Z           | 4.6.1 | Co-design of Selector Length and Read/Write Voltages  | 58 |

| 2           | 4.6.2 | Selector Material Requirements and Figures of Merit   | 64 |

| Z           | 4.6.3 | Non-linearity in Selector Parameters                  | 67 |

| Z           | 4.6.4 | Process Variations                                    | 67 |

| Z           | 4.6.5 | Other Factors                                         | 68 |

| 4.7         | Cas   | se Studies                                            | 69 |

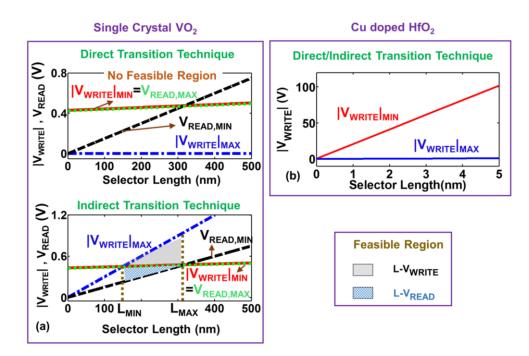

| Z           | 4.7.1 | Single Crystal (SC) VO <sub>2</sub>                   | 70 |

| 2           | 4.7.2 | Copper (Cu)-doped HfO <sub>2</sub>                    | 73 |

| 4.8         | Ma    | terial Space Analysis                                 | 74 |

| 4.9         | Sui   | nmary                                                 | 76 |

| 5. (        | COMI  | PUTATIONALLY EFFICIENT COMPACT MODEL FOR LEAKAGE      |    |

| I           | ANAI  | LYSIS IN CROSS-POINT ARRAY                            | 77 |

| 5.1         | Int   | roduction                                             | 77 |

| 5.2         | Mo    | deling Methodology                                    | 78 |

| 5.3         | De    | scription of Simulation Framework                     | 81 |

| 5.4         | An    | alysis and Verification                               | 81 |

| 4           | 5.4.1 | Impact of OFF State Resistance of Selector            | 83 |

| 4           | 5.4.2 | Impact of Interconnect Resistance                     | 84 |

| 5.4   | 4.3 Impact of Access Voltage                                             | 84       |

|-------|--------------------------------------------------------------------------|----------|

| 5.4   | 4.4 Effect of Size of the Accessed Block                                 | 85       |

| 5.5   | Summary                                                                  | 86       |

| 6. HY | YBRID PHASE TRANSITION FET (HYPER-FET): DEVICE-CIRCUIT C                 | 'O-      |

| DE    | ESIGN                                                                    | 87       |

| 6.1   | Introduction                                                             | 87       |

| 6.2   | Principle of Hyper-FET Operation                                         | 88       |

| 6.3   | Modeling and Simulation Framework for Hyper-FET                          | 90       |

| 6.4   | Constraints for Material Selection and Design                            | 91       |

| 6.5   | Device Characteristics of Hyper-FET                                      | 95       |

| 6.6   | Effect of Material Properties on Device Operation                        | 98       |

| 6.6   | 6.1 Analysis on Transfer Characteristics                                 | 98       |

| 6.6   | 6.2 Analysis on Output Characteristics                                   | 100      |

| 6.7   | Effect of PTM Geometry on Device Operation                               | 101      |

| 6.7   | 7.1 Tailoring Hysteresis                                                 | 101      |

| 6.7   | 7.2 Modulating $I_{ON} / I_{OFF}$                                        | 103      |

| 6.8   | Hyper-FET Inverter: DC Response                                          | 103      |

| 6.8   | 8.1 Voltage Transfer Characteristics                                     | 104      |

| 6.8   | 8.2 PTM Selection: DC Perspective                                        | 106      |

| 6.8   | 8.3 Correspondence between Hysteresis in Device and Circuit Characterist | tics 110 |

| 6.8   | 8.4 Apparent and Achievable Voltage Swing                                | 111      |

| 6.9   | Hyper-FET Inverter: Transient Operation                                  | 113      |

| 6.9   | 9.1 Analysis of Transient Waveforms                                      | 113      |

| 6.9   | 9.2 Ring Oscillator (RO): Energy-Delay Analysis                          | 115      |

| 6.9   | 9.3 PTM Selection: Transient Perspective                                 | 117      |

| 6.10  | Noise Response                                                           | 117      |

| 6.11  | Hyper-FET Based NAND and NOR Gates                                       | 119      |

| 6.12  | Direction for Material Exploration                                       | 120      |

| 6.13  | Summary                                                                  | 121      |

| 7. LC | OW POWER SENSE AMPLIFIER BASED ON PHASE TRANSITION                       |          |

| M     | ATERIAL                                                                  | 123      |

| 7.1   | Intr | oduction                                              | 123 |

|-------|------|-------------------------------------------------------|-----|

| 7.2   | Co   | nventional Sense Amplifier Topologies                 | 124 |

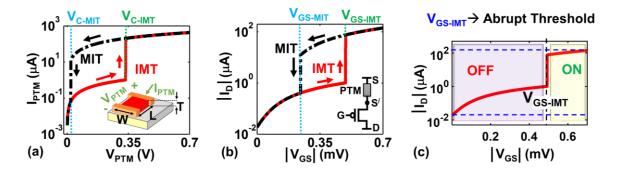

| 7.3   | Abı  | rupt Threshold Point in Hyper-FET                     | 125 |

| 7.4   | Pha  | se Transition Material Based Sense Amplifier          | 126 |

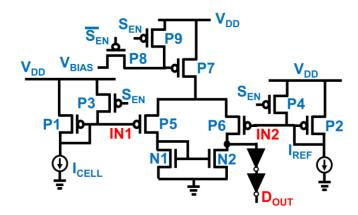

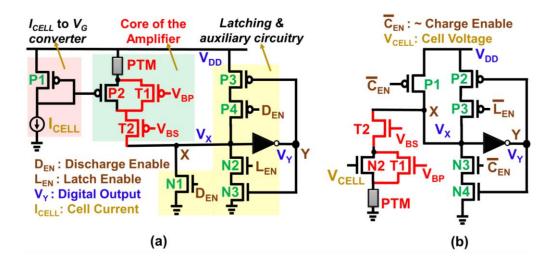

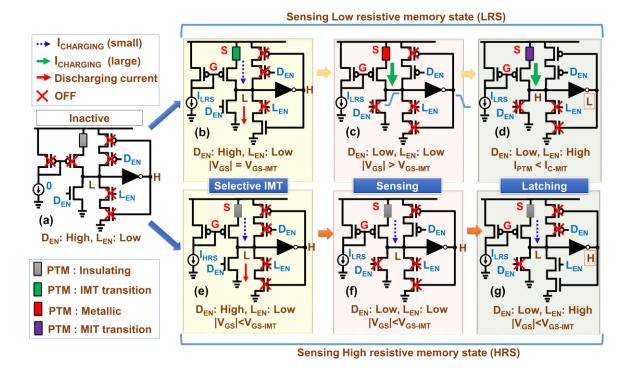

| 7.    | 4.1  | Circuit Description and Principle of Operation        | 127 |

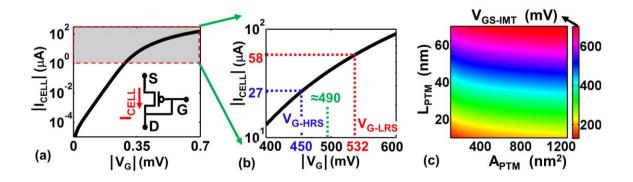

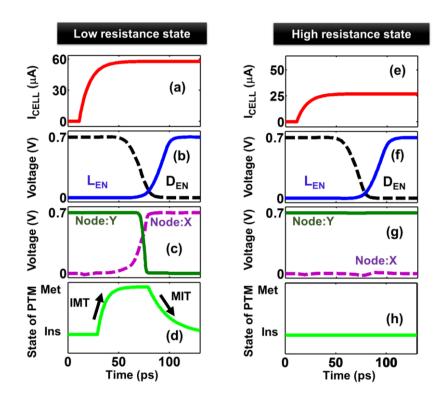

| 7.    | 4.2  | Design Methodology and Simulation Set-up              | 130 |

| 7.    | 4.3  | Dynamic Reference Tuning                              | 133 |

| 7.    | 4.4  | High Performance and Low Power Designs                | 134 |

| 7.5   | Eff  | ect of Variation                                      | 135 |

| 7.6   | Eva  | aluation of Layout and Performance Metrics            | 137 |

| 7.7   | Sur  | nmary                                                 | 138 |

| 8. H  | ARN  | ESSING UNIPOLAR THRESHOLD SWITCHES FOR ENHANCE        | D   |

| R     | ECT  | IFICATION                                             | 139 |

| 8.1   | Intr | oduction                                              | 139 |

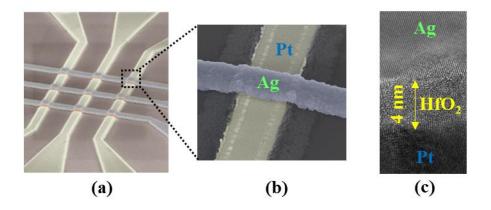

| 8.2   | Fab  | prication and Simulation Set-Up                       | 139 |

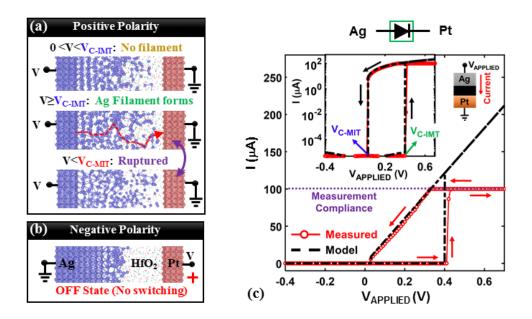

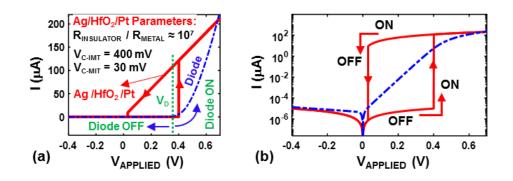

| 8.3   | Uni  | ipolar Ag/HfO2/Pt TS versus Regular Diodes            | 142 |

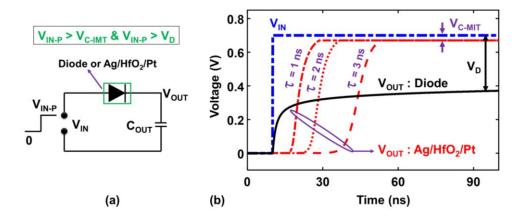

| 8.4   | Coo  | ckcroft-Walton Multiplier (CWM) Design and Comparison | 144 |

| 8.5   | Sur  | nmary                                                 | 148 |

| 9. C  | ONC  | CLUSION                                               | 149 |

| 9.1   | Sur  | nmary                                                 | 149 |

| 9.2   | Out  | tlook and Future Work                                 | 152 |

| 9.    | 2.1  | PTM Augmented Logic-in-Memory                         | 152 |

| 9.    | 2.2  | PTM based Artificial Spiking Neuron                   | 153 |

| 9.    | 2.3  | Hybrid Thermo-Electric Switching for Cryptography     | 153 |

| REFE  | REN  | CES                                                   | 154 |

| VITA. |      |                                                       | 171 |

| PUBL  | ICA  | TIONS                                                 | 172 |

## LIST OF TABLES

| Table 2.1 List of Parameters Used for Simulation of STT and TSA MRAMs          | 11  |

|--------------------------------------------------------------------------------|-----|

| Table 2.2 Design Space Related Terminologies for TSA MRAM                      | 13  |

| Table 2.3 Specifications for Monte-Carlo Analysis                              | 24  |

| Table 3.1 Specification of the Simulation Framework and Material Parameters    | 34  |

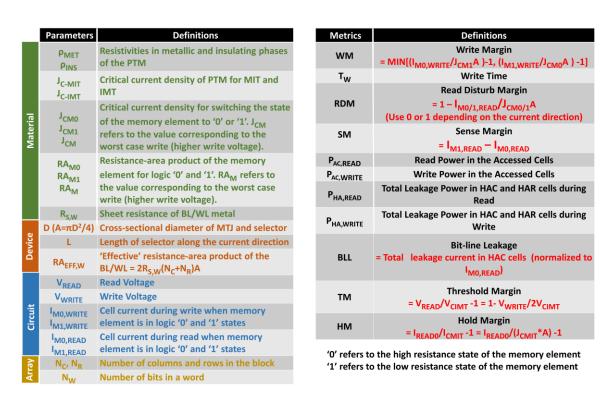

| Table 4.1 List of Design Parameters and Metrics                                | 54  |

| Table 4.2 Simulation Parameters for Case Studies and Material Space Analysis . | 69  |

| Table 5.1 Sample of the Derivation Process                                     | 80  |

| Table 5.2 Default Simulation Parameters and Specifications                     | 82  |

| Table 6.1 Nominal Simulation Parameters                                        | 90  |

| Table 6.2 Assessment of Feasibility of some Currently Available PTMs           | 120 |

| Table 6.3 Summary of Material Requirements Dictated by Design Constraints      | 120 |

| Table 7.1 List of Simulation Parameters and Specifications                     | 131 |

| Table 7.2 Comparison of Performance Metrics                                    | 138 |

## LIST OF FIGURES

| Fig. 1.1 Current-Voltage ( <i>I-V</i> ) Characteristics of a typical phase transition material.                  |

|------------------------------------------------------------------------------------------------------------------|

| The critical voltage/current levels corresponding to phase transitions have                                      |

| been marked3                                                                                                     |

| Fig. 1.2 Compilation of measured current-voltage (I-V) characteristics of a few phase                            |

| transition materials reported in literature. (a) Ag/HfO2/Si (b) Cu-doped                                         |

| HfO <sub>2</sub> (c) VO <sub>2</sub> (d) NbO <sub>2</sub> (e) doped chalcogenide (f) Ag/HfO <sub>2</sub> /Pt5    |

| Fig. 2.1 (a) Schematic diagram of a spin transfer torque (STT) MRAM cell. (b)                                    |

| Schematic and 3D structure for a threshold switch augmented MRAM9                                                |

| Fig. 2.2 Behavioral representation of the phenomenological model for threshold                                   |

| switch / phase transition materials10                                                                            |

| Fig. 2.3 Principle of operation for TSA MRAM12                                                                   |

| Fig. 2.4 Feasible range of bias voltage to ensure desired phase change in the threshold                          |

| switch during (a) read and (b) write operations14                                                                |

| Fig. 2.5 Simulated transient response for (a-c) read and (d-f) write operations16                                |

| Fig. 2.6 Comparison of (a) cell tunneling magneto resistance (b) sense margin (c)                                |

| read disturb margin and (d) average read power of STT and TSA MRAMs                                              |

| at different V <sub>READ</sub> 19                                                                                |

| Fig. 2.7 (a) Illustration of $I_{READ-INIT}$ and (b) the concept of achieving <i>iso-</i> $\Delta I_{READ-INIT}$ |

| between STT and TSA MRAMs20                                                                                      |

| Fig. 2.8 (a) Average write power and (b) write time as functions of $V_{WRITE}$ for STT                          |

| and TSA MRAMs21                                                                                                  |

| Fig. 2.9 The ORO for TSA MRAM can be tuned utilizing (a) $R_{INS}$ (b) $R_{MET}$ (c) $I_{C-IMT}$                 |

| and (d) $I_{C-MIT}$ . (e) Change in $R_{INS}$ has major impact on CTMR and RDM. (f)                              |

| $R_{MET}$ primarily shows impact on CTMR and $T_{WRITE}$                                                         |

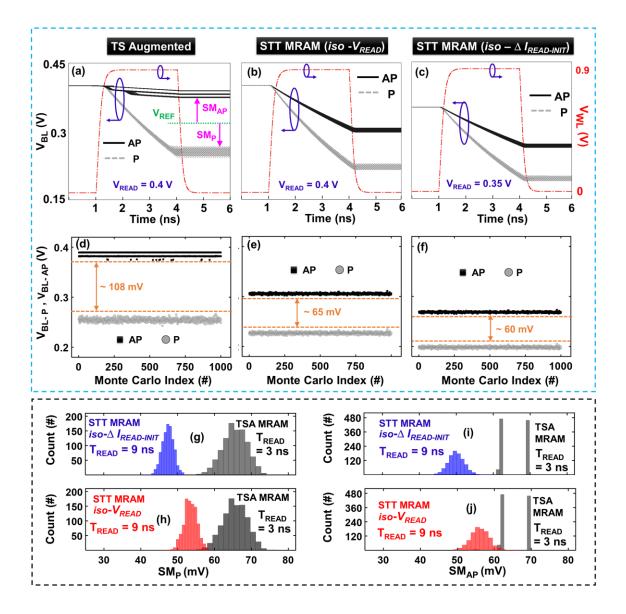

| Fig. 2.10 Monte-Carlo simulation results for read operation. (a)–(c) Discharge of BL                             |

| during read. (d)-(f) Extracted values of $V_{BL-P}$ and $V_{BL-AP}$ . (g)-(j) Distribution                       |

| of SM <sub>P</sub> and SM <sub>AP</sub> for both MRAMs. For (g)-(j), $T_{READ}$ for STT MARM is 9                |

| ns, whereas that for TSA MRAM is 3 ns. The STT MRAM requires                                                     |

| additional time to achieve practical levels of $SM_P$ and $SM_{AP}$ 26                                           |

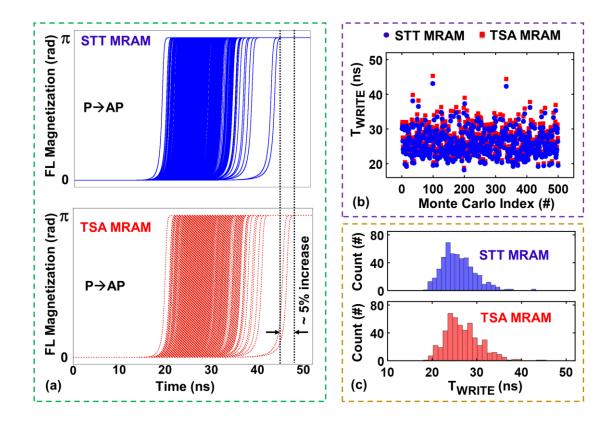

| Fig. 2.11 Monte-Carlo simulation waveforms for write operation. (a) $P \rightarrow AP$ |    |

|----------------------------------------------------------------------------------------|----|

| switching of the FL. (b) Values of $T_{WRITE}$ for different combinations              |    |

| incurred during the simulations. (c) Distributions for T <sub>WRITE</sub>              | 27 |

| Fig. 2.12 Effect of transition time on (a) read and (b) write performance of TSA       |    |

| MRAM. $T_{MIT}$ has been assumed to be ~double of the corresponding $T_{IMT}$          | 28 |

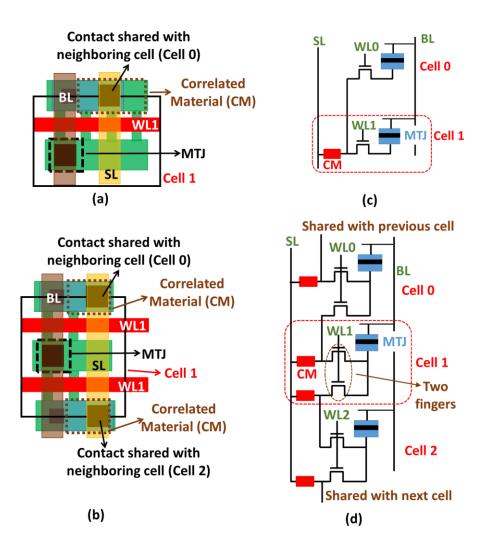

| Fig. 2.13 Layout of memory cell with (a) single-finger and (b) two-finger access       |    |

| transistor showing sharing of the contact and the CM. Corresponding                    |    |

| schematics are shown in (c) and (d).                                                   | 29 |

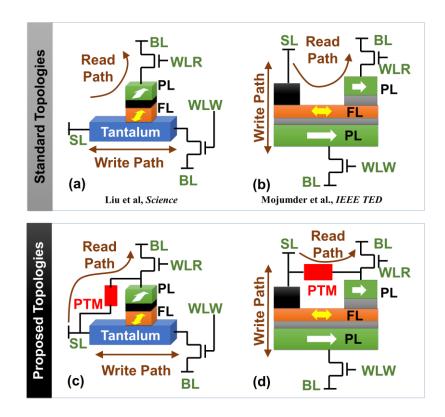

| Fig. 3.1 (a) Multi-port MRAM with GSHE based write operation. (b) Multi-port           |    |

| MRAM with magnetic anisotropy based write operation. $(c - d)$ Modified                |    |

| version of designs shown in (a) and (b) which show incorporation of PTM                |    |

| in the read path only                                                                  | 33 |

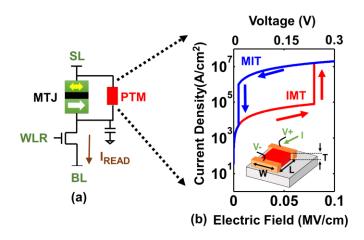

| Fig. 3.2 (a) Read equivalent circuit for the proposed multi-port MRAM topology (b)     |    |

| current-voltage $(I-V)$ characteristics obtained from the compact model using          |    |

| the experimentally extracted material parameters.                                      | 34 |

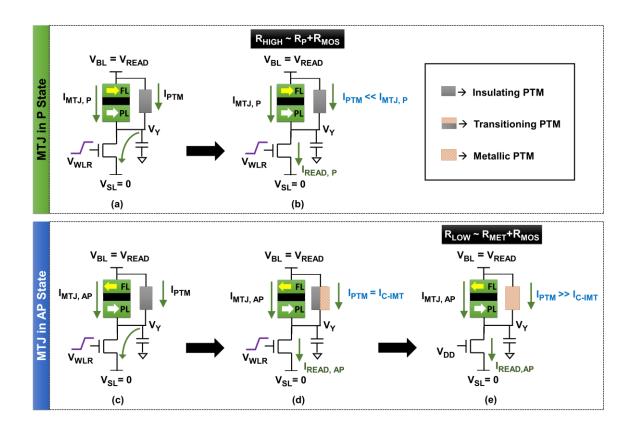

| Fig. 3.3 Principle of the read operation for the proposed MRAM utilizing resistance    |    |

| switching of the PTM. Transient steps of read operation for an MTJ with                |    |

| (a-b) parallel magnetization (c-e) antiparallel magnetization.                         | 35 |

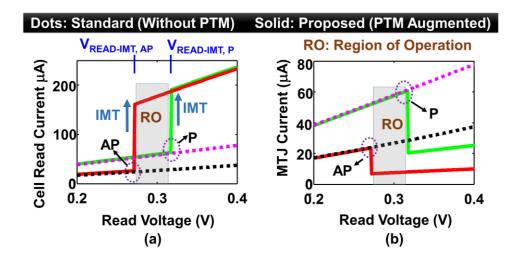

| Fig. 3.4 (a) Read current versus read voltage for the standard and proposed designs    |    |

| of multi-port MRAMs. The valid region of operation has been highlighted.               |    |

| (b) Current flow through the MTJ $(I_{MTJ})$ in the read path. Significant             |    |

| reduction in $I_{MTJ}$ is observed for an MTJ with AP magnetization in the             |    |

| proposed design                                                                        | 37 |

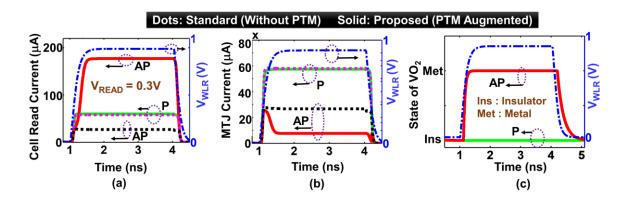

| Fig. 3.5 Simulated transient response for the standard and proposed multi-port         |    |

| MRAMs. (a) Total read current through the cell when the WLR is asserted.               |    |

| (b) Current flowing through the MTJ. (c) Evolution of the resistive state of           |    |

| the PTM in the proposed design                                                         | 38 |

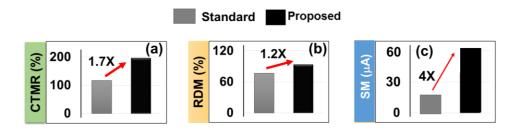

| Fig. 3.6 Comparison of the (a) CTMR and (b) RDM (c) SM for the proposed and            |    |

| standard multi-port MRAM designs                                                       | 39 |

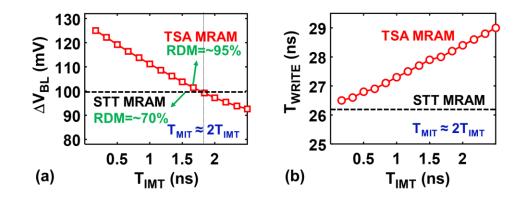

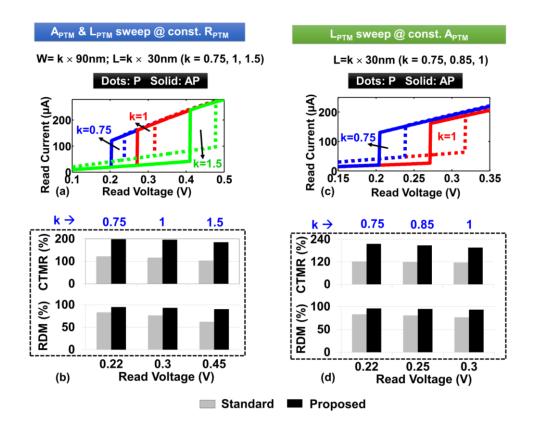

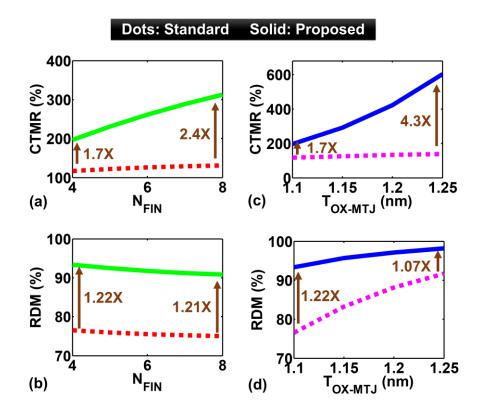

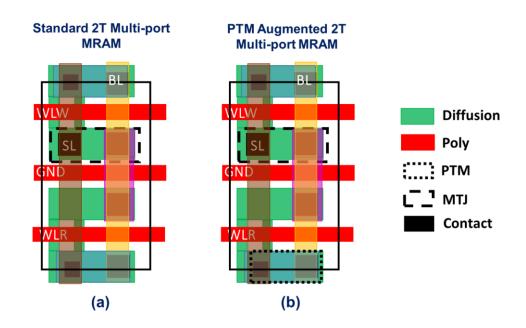

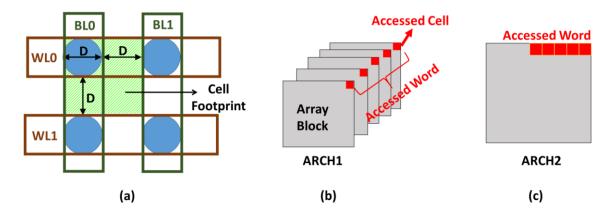

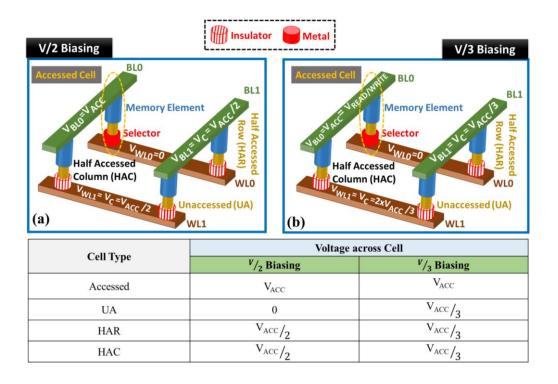

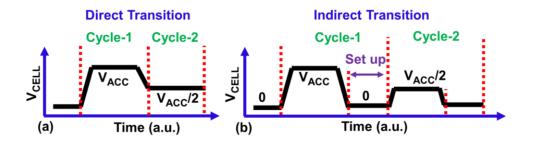

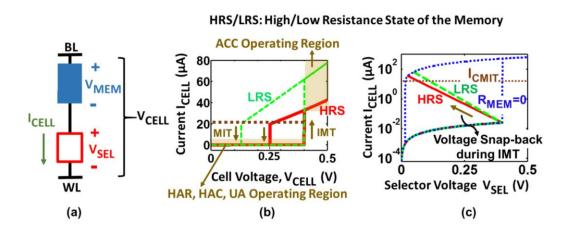

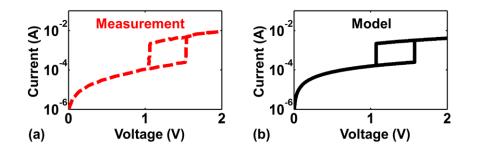

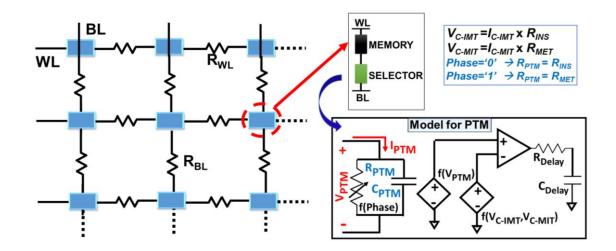

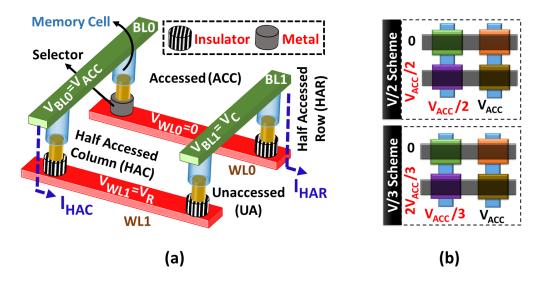

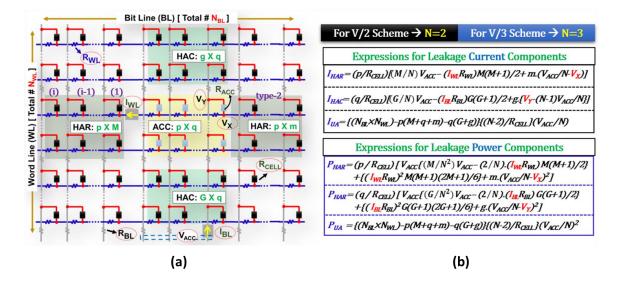

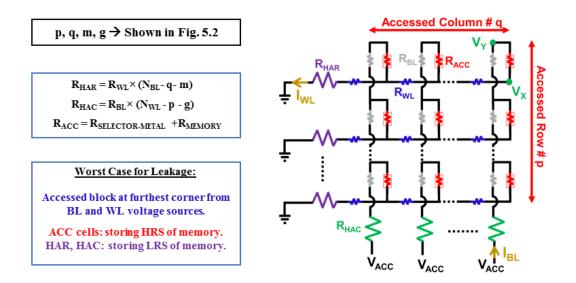

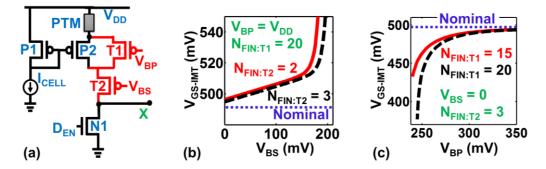

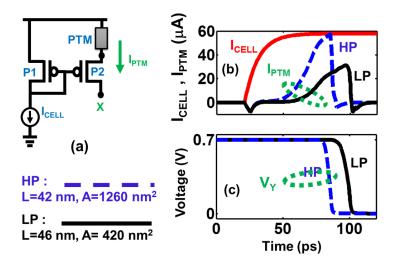

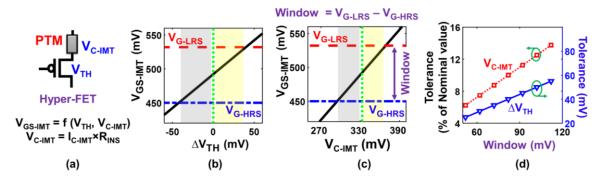

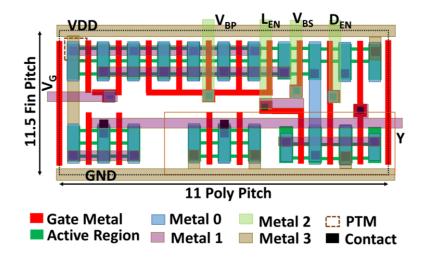

Fig. 3.7 (a) Option A: Tuning the valid region of operation by changing the critical currents of transitions. (b) Performance evaluation for the proposed design for different ROs, set using option A. (c) Option B: Tuning the valid region of operation by changing the resistance of metallic and insulating states. (d) Performance evaluation for the proposed design for different ROs, set using option B......40 Fig. 3.8 CTMR and RDM for (a, b) different fin number of the read access transistor  $(N_{FIN})$  with  $T_{OX-MTJ} = 1.1$  nm and (c, d) for different MgO thickness in the Fig. 3.9 Layout of (a) standard multi-port MRAM and (b) PTM augmented proposed Fig. 4.1 (a) Layout (top view) of a 2×2 cross-point array. Cross-point architectures with bits of the accessed word in (b) separate blocks and (c) in the same Fig. 4.2 (a) A portion  $(2\times 2)$  of cross-point array illustrating (a) V/2 and (b) V/3 biasing schemes. The voltage levels across four types of cells in the array Fig. 4.3 Bit-line voltage of a cell (Cell A) transitioning from the accessed (ACC) mode to the half accessed row (HAR) mode for V/2 biasing showing - (a) direct transitioning scheme and (b) indirect transitioning scheme with a setup period in between the two consecutive access cycles......49 Fig. 4.4 (a) Cell schematic showing voltage drop across the memory element ( $V_{MEM}$ ), selector ( $V_{SEL}$ ) and the cell ( $V_{CELL} = V_{MEM} + V_{SEL}$ ) with current-voltage characteristics of (b) a cell showing operating regions of accessed (ACC), half-accessed (HAR, HAC) and unaccessed (UA) cells and (c) selector (in series with the memory element) showing voltage snap-back due to IMT. ......50 Fig. 4.5 Calibration of the compact model for PTM with the experimental data on Fig. 4.6 Simulation framework based on SPICE model for the PTM. An MTJ has been used as the memory element. Distributed resistance and capacitance of the bit-line (BL) and word-line (WL) are considered......56

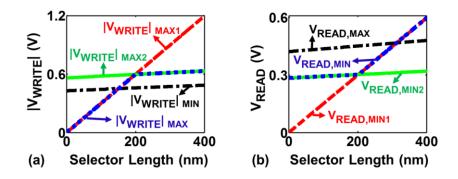

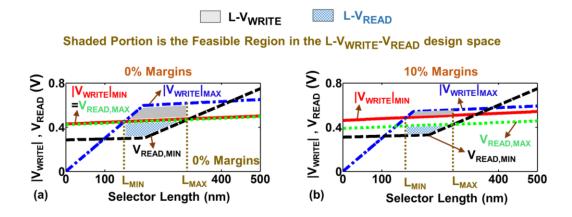

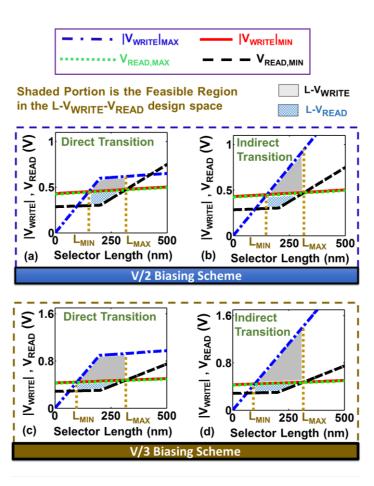

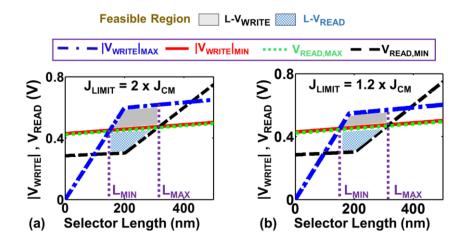

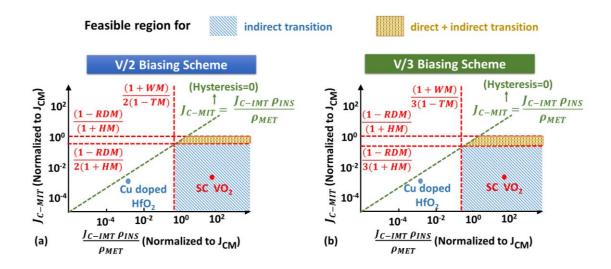

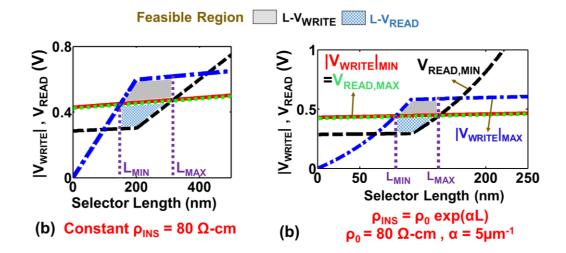

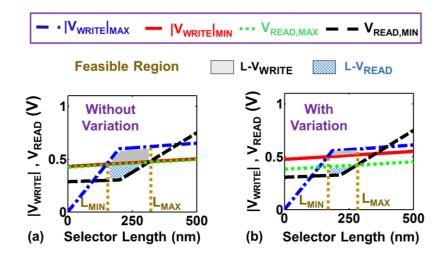

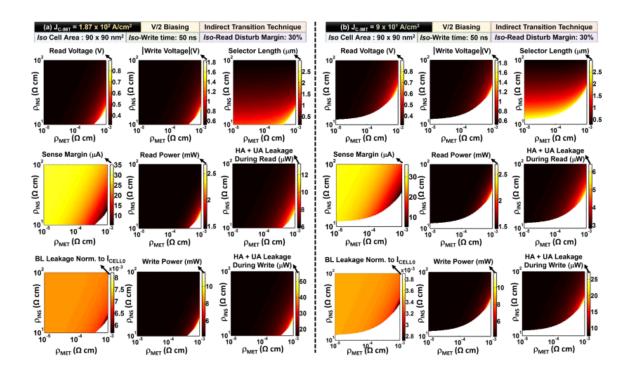

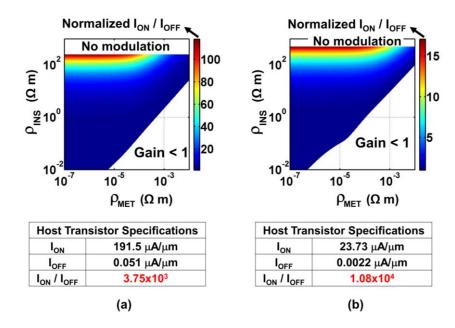

- Fig. 4.9 Comparison of the feasible design space for different biasing schemes (V/2, V/3), and transition methods (direct, indirect) showing larger design space for V/3 scheme compared to V/2; and boost in design space using indirect transition method.

62

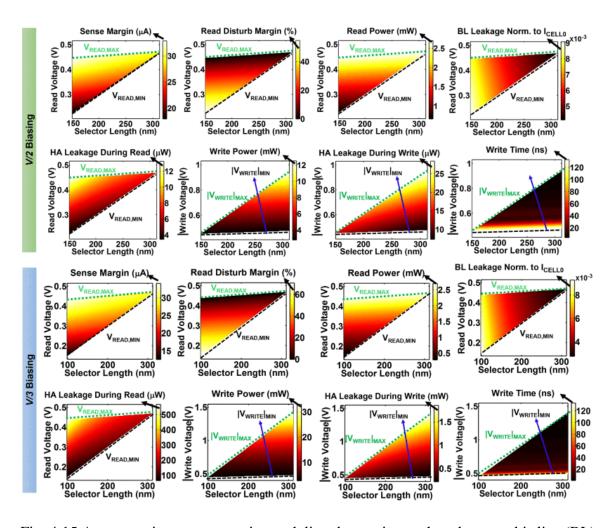

- Fig. 4.15 Array metrics: sense margin; read disturb margin; total read power; bit-line (BL) leakage; total leakage power of the half-accessed/unaccessed (HA+UA) cells during read; total write power; total leakage power of the half-accessed cells during write; write time as a function of the selector length with single crystal VO<sub>2</sub> selector and read/write voltages. The analysis is performed considering 0% margins for V/2 scheme and V/3 scheme employing indirect transition.

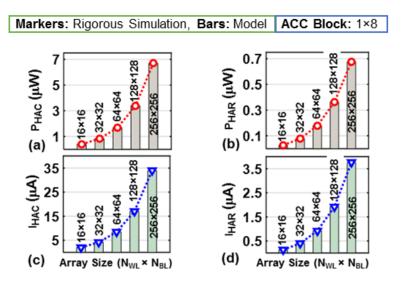

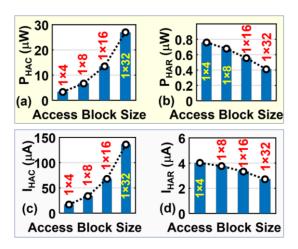

| Fig. 5.4 The leakage power (a, b) and current (c, d) for HAR and HAC in different                  |

|----------------------------------------------------------------------------------------------------|

| sizes of array. The values obtained from the compact model matches                                 |

| accurately with those obtained through rigorous simulation of complete                             |

| array (V/2 biasing scheme)                                                                         |

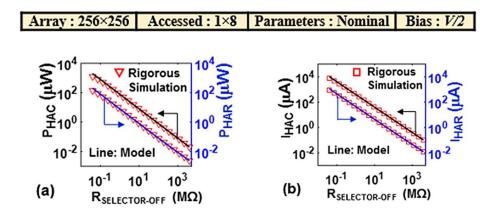

| Fig. 5.5 The compact model precisely captures the effect of $R_{SELECTOR-OFF}$ on (a)              |

| leakage power and (b) leakage current of half accessed (HA) cells                                  |

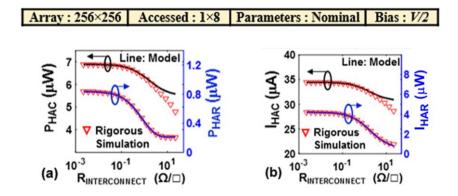

| Fig. 5.6 The distributed interconnect resistance model considered to formulate the                 |

| closed-form equations (in Fig. 5.2) yields accurate results up to                                  |

| $R_{INTERCONNECT} \approx 5 \ \Omega/\Box$                                                         |

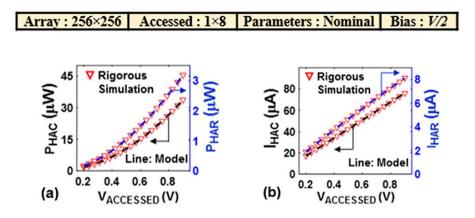

| Fig. 5.7 Leakage (a) power and (b) current of the HA cells increases with access                   |

| voltage ( $V_{ACCESSED}$ ). For all values of $V_{ACCESSED}$ , the compact model                   |

| provides accurate results                                                                          |

| Fig. 5.8 Leakage (a, b) power and (c, d) current of the HA cells is a function of the              |

| size of the accessed block. If the number of rows in an accessed block                             |

| increases with fixed number of column, $P_{HAC}$ and $I_{HAC}$ increase, whereas                   |

| $P_{HAR}$ and $I_{HAR}$ decrease                                                                   |

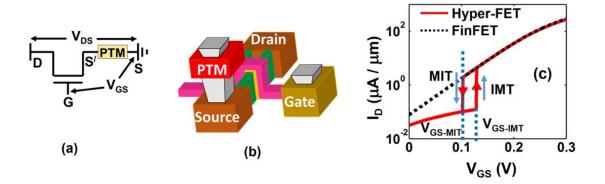

| Fig. 6.1 (a) Schematic and (b) 3D structure of Hyper-FET. (c) Typical transfer                     |

| characteristics Hyper-FET (compared with the standard 14 nm FinFET)                                |

| Fig. 6.2 (a) Behavioral representation of different components of the modeling                     |

| framework for Hyper-FET. (b) Current-voltage ( <i>I-V</i> ) characteristics of the                 |

| model material (PTM-Sim) used for simulations. The <i>I-V</i> characteristics of                   |

| single crystal VO <sub>2</sub> has also been shown for comparison                                  |

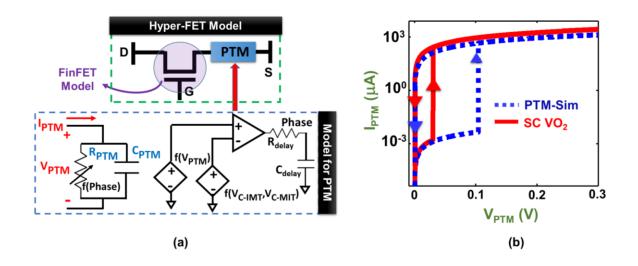

| Fig. 6.3 Mapping of $I_{ON} - I_{OFF}$ ratio of Hyper-FET with a host transistor having (a)        |

|                                                                                                    |

| low and (b) high $I_{ON}/I_{OFF}$ . The values of the $I_{ON}/I_{OFF}$ of the Hyper-FETs           |

| have been normalized to that of their corresponding host transistors                               |

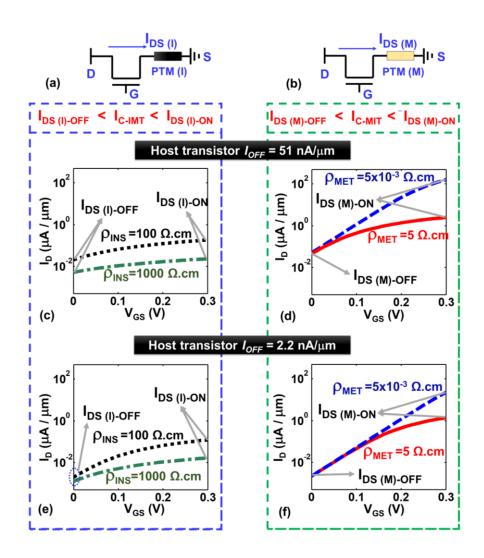

| Fig. 6.4 Constraints on critical current level for (c) IMT and (d) MIT phase switching             |

| corresponding to a host transistor with $I_{OFF} = 0.051 \ \mu\text{A}/\mu\text{m}$ . (e - f) Same |

| metrics for a host transistor with lower inherent $I_{OFF}$ (higher OFF resistance).               |

| The limits have been obtained considering a constant resistor attached to the                      |

| source of a standard MOSFET, with resistance equal to (a) insulating and                           |

| (b) metallic state of PTM94                                                                        |

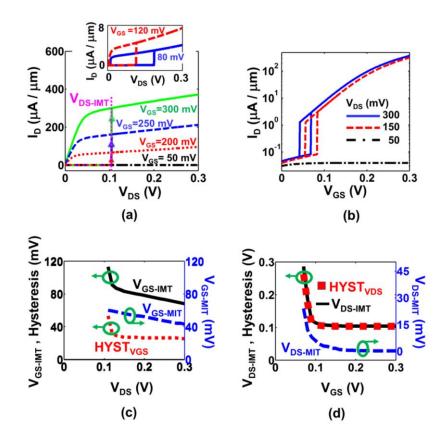

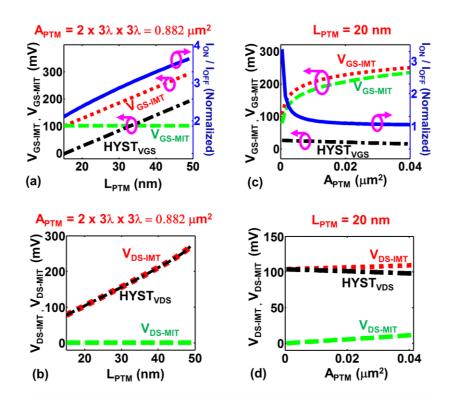

- Fig. 6.9 Effect of the geometry of CM on device metrics. (a)  $V_{GS-IMT}$  changes significantly with  $L_{PTM}$ , whereas  $V_{GS-MIT}$  is almost desensitized to  $L_{PTM}$ . Higher  $L_{PTM}$  also yields high  $I_{ON}$  -  $I_{OFF}$  ratio. (b) Both  $V_{GS-IMT}$  and  $V_{GS-MIT}$ changes significantly with  $A_{PTM}$ . Higher  $A_{PTM}$  reduces  $I_{ON}$  -  $I_{OFF}$  ratio. (c)  $V_{DS-IMT}$  and corresponding  $HYST_{VDS}$  increases with  $L_{PTM}$ . (d)  $V_{DS-IMT}$  remains fixed while  $V_{DS-MIT}$  increases with  $A_{PTM}$ , reducing  $HYST_{VDS}$ ......102

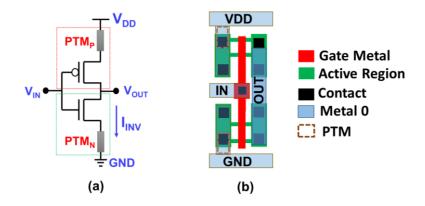

Fig. 6.10 (a) Circuit diagram and (b) layout of Hyper-FET based inverter.....104

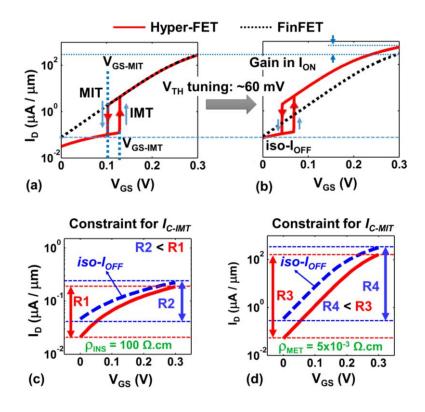

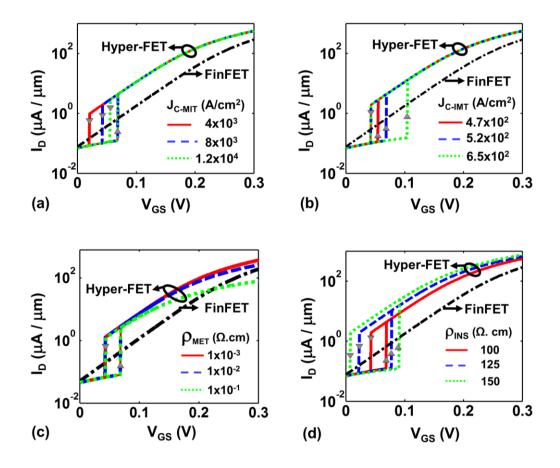

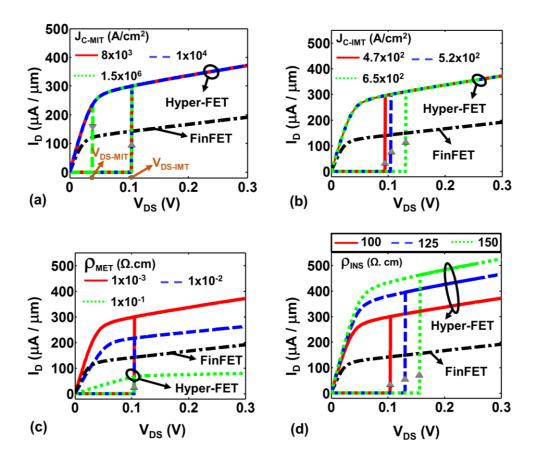

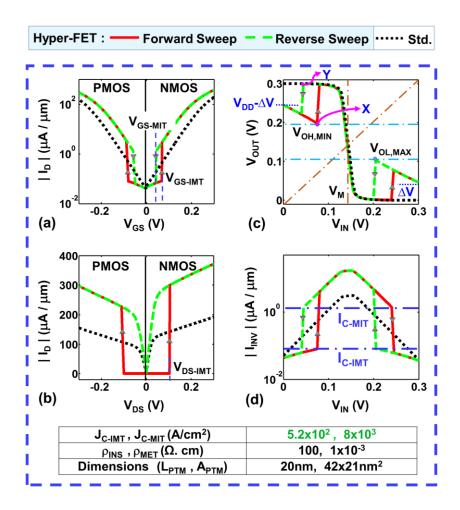

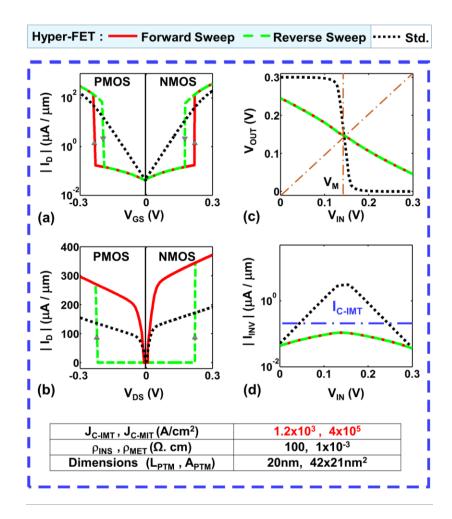

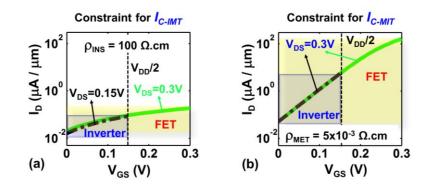

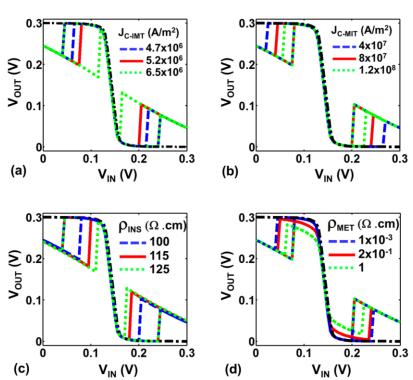

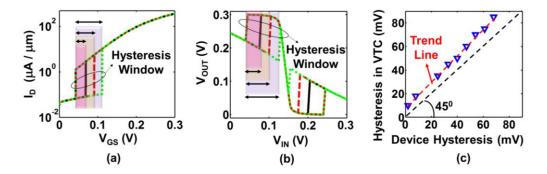

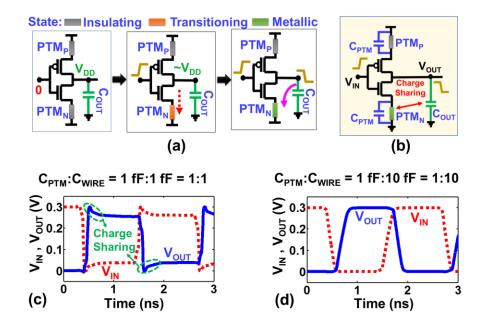

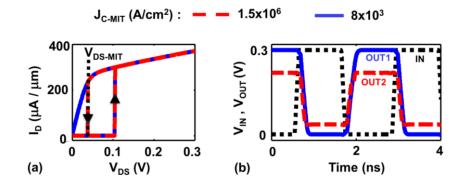

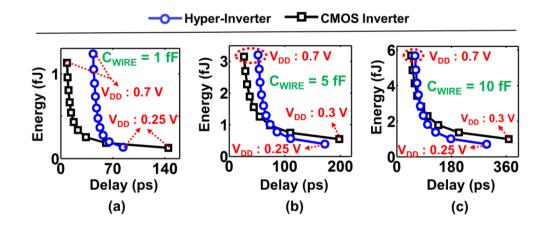

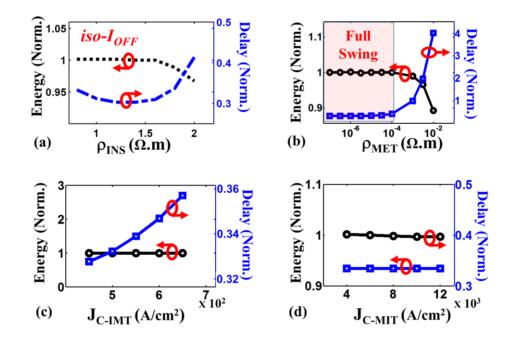

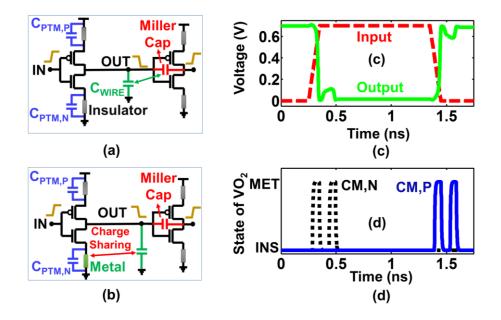

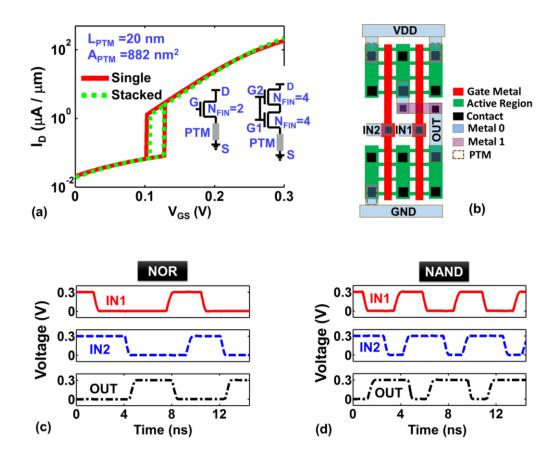

Fig. 6.11 (a) Transfer and (b) output characteristics of complementary n and p Hyper-FETs yielding phase switching at low ( $\langle V_{DD}/2 \rangle$ ) bias voltage. (c) Voltage transfer characteristics (VTC) of the functioning Hyper-FET inverter. (d) Fig. 6.12 (a) Transfer and (b) output characteristics of complementary n and p Hyper-FETs yielding phase switching at higher (> $V_{DD}/2$ ) bias voltage. (c) VTC of the Hyper-FET inverter illustrating |gain| < 1 in the transition region. (d) Current through the non-functioning inverter......107 Fig. 6.13 (a) Feasible ranges of critical current level for (a) IMT and (b) MIT phase switching. The feasible ranges for  $I_{C-IMT}$  and  $I_{C-MIT}$  becomes stringent for a Hyper-FET inverter as compared to those for the Hyper-FET. ......108 Fig. 6.14 Effect of (a)  $J_{C-IMT}$  (b)  $J_{C-MIT}$  (c)  $\rho_{INS}$  and (d)  $\rho_{MET}$  on the VTC of Hyper-Fig. 6.15 (a) Different levels of hysteresis window in transfer characteristics of Hyper-FET. (b) Corresponding hysteresis in VTC. (c) Trend line shows that hysteresis in VTC is linearly dependent on that in transfer characteristics but is always larger in magnitude.....110 Fig. 6.16 (a) Steps of transient operation of a Hyper-FET based inverter. (b) Representation of charge sharing in Hyper-FET inverter. (c) Transient waveforms for Hyper-FET inverter chain illustrating charge sharing between  $C_{PTM}$  and  $C_{OUT}$ . (d) Charge sharing is not pronounced for  $C_{WIRE}$ Fig. 6.17 (a) Output characteristics of two versions of Hyper-FET (with different PTMs), illustrating MIT driven 'dead zone' in one. (b) The 'dead zone' in Fig. 6.18 (a) Energy-delay metrics for Hyper-FET based and standard ring oscillators

- Fig. 6.20 (a) Charge injection at the output node of an inverter stage through miller capacitance effect arising from the next stage. (b) Increase in output voltage triggers IMT in PTM once it crosses critical voltage level. (c) Hyper-FET inverter waveforms showing full rail-to-rail swing with time limited glitches due to floating output node. (d) Short spanned oscillatory phase transition in PTMs eradicating noise contribution from output......118

- Fig. 6.21 (a) Through proper sizing of transistors, stacked Hyper-FET structure can present identical characteristics as a single device. (b) Layout of a Hyper-FET based NAND gate. Transient waveforms for (c) NOR and (d) NAND gates designed with Hyper-FET.

- Fig. 7.1 conventional current based sense amplifier topology......125

- Fig. 7.2 (a) Current –voltage characteristics of a phase transition material-VO<sub>2</sub> illustrating IMT and MIT. Inset shows transport geometry and biasing scenario. (b) Transfer characteristics of a p-type Hyper-FET......127

- Fig. 8.3 *I-V* characteristics of a diode ((a) linear scale (b) semilog scale), designed to exhibit ~similar ON current and turn ON threshold ( $V_D \approx V_{C-IMT}$ ) as those of the unipolar Ag/HfO<sub>2</sub>/Pt. Unlike any diode, the turn ON and turn OFF thresholds for Ag/HfO<sub>2</sub>/Pt is different due to its hysteretic characteristics. .....142

- Fig. 8.4 (a) A simple circuit set-up to illustrate the advantage of a hysteretic rectifier.(b) Simulated step response of the circuit in (a), showing better performance with Ag/HfO<sub>2</sub>/Pt compared with conventional diode......143

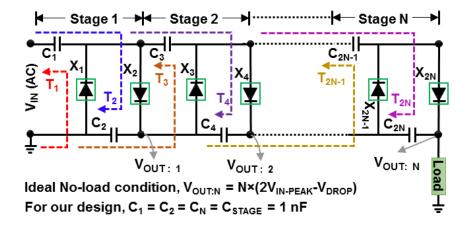

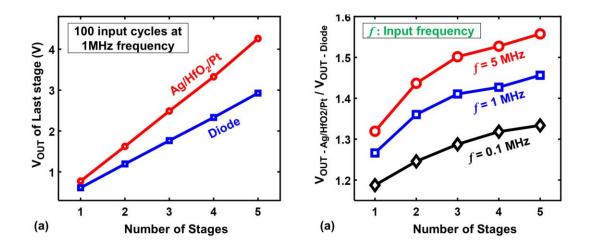

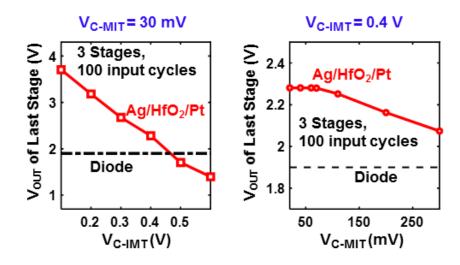

- Fig. 8.5 An *N*-stage *Cockroft-Walton* multiplier (CWM) circuit. Here, X denotes regular diode or Ag/HfO<sub>2</sub>/Pt. *T<sub>N</sub>* represents *N<sup>th</sup>* half-cycle of input......144

- Fig. 8.6 Transient simulation of a 3 stage CWM based on (a) Ag/HfO<sub>2</sub>/Pt and (b) regular diode. The former shows higher output ( $V_{OUT}$ ) at every stage. [Inset: Input voltage used for both of the designs.  $V_{IN-PEAK} > V_{C-IMT} (\approx V_D)$ ]......145

## ABSTRACT

Author: Aziz, Ahmedullah. PhD

Institution: Purdue University

Degree Received: August 2019

Title: Device-Circuit Co-Design Employing Phase Transition Materials for Low Power Electronics

Committee Chair: Sumeet Gupta

Phase transition materials (PTM) have garnered immense interest in concurrent post-CMOS electronics, due to their unique properties such as - electrically driven abrupt resistance switching, hysteresis, and high selectivity. The phase transitions can be attributed to diverse material-specific phenomena, including- correlated electrons, filamentary ion diffusion, and dimerization. In this research, we explore the application space for these materials through extensive device-circuit co-design and propose new ideas harnessing their unique electrical properties. The abrupt transitions and high selectivity of PTMs enable steep (< 60 mV/decade) switching characteristics in Hyper-FET, a promising post-CMOS transistor. We explore device-circuit co-design methodology for Hyper-FET and identify the criterion for material down-selection. We evaluate the achievable voltage swing, energy-delay trade-off, and noise response for this novel device. In addition to the application in low power logic device, PTMs can actively facilitate non-volatile memory design. We propose a PTM augmented Spin Transfer Torque (STT) MRAM that utilizes selective phase transitions to boost the sense margin and stability of stored data, simultaneously. We show that such selective transitions can also be used to improve other MRAM designs with separate read/write paths, avoiding the possibility of read-write conflicts. Further, we analyze the application of PTMs as selectors in cross-point memories. We establish a general simulation framework for cross-point memory array with PTM based *selector*. We explore the biasing constraints, develop detailed design methodology, and deduce figures of merit for PTM selectors. We also develop a computationally efficient compact model to estimate the leakage through the sneak paths in a cross-point array. Subsequently, we present a new sense amplifier design utilizing PTM, which offers builtin tunable reference with low power and area demand. Finally, we show that the hysteretic characteristics of unipolar PTMs can be utilized to achieve highly efficient rectification.

We validate the idea by demonstrating significant design improvements in a *Cockcroft-Walton Multiplier*, implemented with TS based rectifiers. We emphasize the need to explore other PTMs with high endurance, thermal stability, and faster switching to enable many more innovative applications in the future.

## **1. INTRODUCTION**

#### 1.1 Device-Circuit Co-design for Exploratory Technologies

Relentless evolution of modern electronics has motivated diverse exploratory research on computing and date storage. For decades, periodic downscaling of transistors, dictated by Moore's law [1]–[4], has fueled progress of electronic technologies. To cope with the stupendous growth of the computation complexity in digital systems, it is necessary to keep shrinking the transistors to enhance integration density. However, concerns about the end of the golden age of scaling is building up as the transistor sizes are approaching atomic dimensions. Shorter channel length invokes quantum effects, short channel effects and fabrication challenges [4]. In addition, the fundamental *Boltzmann limit* [4]–[6] (stemming from statistical distribution of free carriers) has become a major hindrance against continued improvement of device and circuit performance [4], [5]. Hence, the quest for alternative device structures, physical phenomena and novel circuit topologies is garnering interest. To satiate the need for superior performance and throughput, design of high-speed transistors has been a perpetual research field. However, due to the surge in interest for portable, wearable and implantable electronic systems, the design of ultra-low power devices/circuits/architectures has also received a major impetus in the recent decades.

Several device structures are being explored to harness sub-kT/q (sub-60 mV/decade) switching to enable ultra-low power circuit operation [5]–[14]. These novel exploratory devices offer unique opportunities and challenges, which need to be thoroughly examined before striding towards industrial realization. Tunnel FET (TFET) [11], [15]–[17], Negative Capacitance FET (NCFET) [14], [18]–[20] and Hyper-FET [6], [21]–[24] are few such examples of steep switching devices. TFETs use modulation of quantum tunneling through a barrier [15] to achieve sharper switching characteristics. However, the design of p-type TFETs with ON currents comparable to the n-type TFETs is still a challenge [8], [16]. In contrast to the TFET, an NCFET achieves steep switching by utilizing the negative capacitance exhibited by the ferroelectric material introduced as an extra layer in the gate stack [14], [19]. A voltage-step-up action is achieved due to the

negative capacitance of the ferroelectric, which yields lower sub-threshold swing and higher ON current ( $I_{ON}$ ) [25], [26]. However, the voltage step-up action is accompanied by an increase in the gate capacitance, which may offset the benefits of higher  $I_{ON}$  [18], [25]–[27]. Hyper-FET utilizes the insulator-metal transitions of an augmented phase transition material (PTM) [22], [28]–[30] to achieve steep switching. The PTM, by virtue of its current driven abrupt switching from the insulating state to the metallic state and vice versa, assists in transistor switching. However, being a hysteretic device, it leads to a complex design space for digital applications. All these examples hint at the necessity to co-design devices and circuits, while dealing with exploratory technologies.

In addition to the devices that make up the logic and computational components of a system, storage elements also mandate rapid reformation. The humungous boost in creation of digital data across the world has led to an unprecedented need for storage. Rapid growth of social networks, large-scale scientific experiments and the internet-of-things (IoT) are some of the major contributors to this overwhelming trend. Design and development of memory technology has become more vital than ever before. There is need for memory devices and architectures that allow faster access. In addition, there is huge demand for non-volatile memory systems, which are appropriate for energy-constrained systems such as portable electronics and energy harvesting platforms. Several non-volatile memory devices have been developed over the past few decades. Resistive RAM [31]-[34], Phase Change Memory [35]–[38], Ferroelectric RAM [39]–[43], NAND/NOR Flash [44]–[48] and Magnetic RAM [49]-[54] are some of the major variants. However, each of these devices have their own limitations and overheads [32], [40], [55]–[58] and there is a strong need to continue the exploration of innovative design approaches to complement or replace the existing design methodologies. Similar to the innovations in the device and circuit level, incorporation of novel architectures is also vital to harness greatest benefit out of the emerging technologies.

Electronics, as we know it, is going through a major paradigm shift. This revolutionary transformation to the post-CMOS era necessitates exploration of unique materials, devices, circuits and systems to cater to the growing demands. Silicon based technology has served

its purpose successfully for decades and has attained maturity. However, even with welldeveloped process technologies, Si based transistors are under-equipped for next generation challenges. A strong need to search for post-CMOS technologies is being echoed across the semiconductor industry. By dint of the research thrust provided by this buzzing interest, new materials and device structures are being proposed and studied. 'Phase transition material' is one of the most promising families of emerging post-Si materials. The unique electrical properties of these materials can be utilized to design novel logic/memory devices and circuits, to facilitate next-generation electronics. This thesis presents some exclusive ideas and techniques regarding potential uses for phase transition materials in designing low-power logic and memory. Comprehensive device-circuit codesign has been carried out for each of these ideas and techniques to analyze the possible implications and feasibility.

#### **1.2** Phase Transition Materials (PTM)

Phase transition materials (PTM) are entities that exhibit abrupt change in resistance due to insulator-metal and metal-insulator transitions triggered by electrical [59][60], thermal [61], mechanical (pressure, strain) [62], [63] or optical stimuli [64]. The phase transitions can be attributed to diverse physical mechanisms (electron-electron correlation [65], [66], filamentary ion diffusion [21], [67], dimerization [68] etc.) in different materials. The

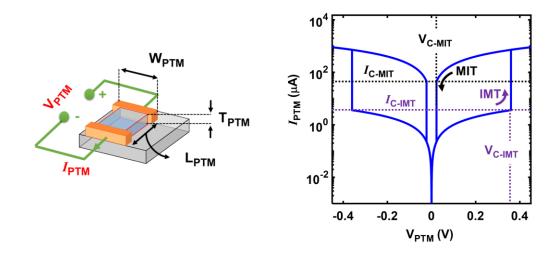

Fig. 1.1 Current-Voltage (*I-V*) Characteristics of a typical phase transition material. The critical voltage/current levels corresponding to phase transitions have been marked.

family of PTMs is quite rich with materials (e.g. VO<sub>2</sub>, V<sub>2</sub>O<sub>3</sub>, V<sub>2</sub>O<sub>4</sub>, TiO, Ti<sub>2</sub>O<sub>3</sub>, SmNiO<sub>3</sub>, Cu-doped HfO<sub>2</sub>, doped chalcogenide etc. [22], [67], [69]–[74]), exhibiting a wide range of resistivity, hysteresis and thermal stability. Moreover, new PTMs are being extensively explored and novel approaches, such as using strain, have been reported to tailor their properties [75]. Such techniques and a wide spectrum of PTMs show promise to down select and optimize the PTMs, as per the needs of specific applications. Note, the materials that undergo such transitions due to having strongly correlated electrons are known as 'Correlated Materials (CM)' [76], [77]. The high and low resistance states of all these transitioning materials are abruptly separated by transition threshold levels. Therefore, they are often referred to as 'Threshold Switches (TS)' [21], [78], [79]. In literature, they are also mentioned as- 'Insulator-Metal Transitioning (IMT) Material' [80]–[83]. Depending on the application, most appropriate acronym will be used for these materials in different chapters of this thesis. However, irrespective of the underlying physical phenomenon, the electrical characteristics of these materials can be behaviorally generalized as follows.

PTMs exist in two phases - metal and insulator, with the resistance of the insulating phase ( $R_{INS}$ ) usually being orders of magnitude higher than the resistance of the metallic phase ( $R_{INS}$ ) usually being orders of magnitude higher than the resistance of the metallic phase ( $R_{MET}$ ). Fig. 1.1 shows the current-voltage (I-V) response and device geometry for a typical PTM.  $W_{PTM}$ ,  $L_{PTM}$  and  $T_{PTM}$  are the width, length and thickness (respectively) of the PTM. In absence of the electrical stimuli, PTMs remain in the insulating phase. In response to a sufficiently high current ( $I_{C-IMT}$ ) (or voltage  $V_{C-IMT}$ ) flowing through (applied across) the material, insulator-to-metal transition (IMT) occurs. Conversely, reduction of current/voltage below a critical level ( $I_{C-MIT}$  or  $V_{C-MIT}$ ) triggers metal-to-insulator transition (MIT). Such transitions lead to an inherently hysteretic behavior in these materials. The IMT and MIT have been shown to be abrupt (but not instantaneous) [84]–[86]. The critical current density for IMT and MIT transitions ( $J_{C-IMT}$  and  $J_{C-MIT}$ ) and the resistivity of metallic and insulating states ( $\rho_{MET}$  and  $\rho_{INS}$ ) are device/geometry independent material parameters. The device specific parameters ( $I_{C-IMT}$ ,  $I_{C-MIT}$ ,  $R_{MET}$  and  $R_{INS}$ ) can be expressed in terms of material level parameters (and geometric dimensions) as shown below.

$$I_{C-IMT} = J_{C-IMT} \times W_{PTM} \times T_{PTM}$$

$$I_{C-MIT} = J_{C-MIT} \times W_{PTM} \times T_{PTM}$$

(1.2)

$R_{MET} = \rho_{MET} \times L_{PTM} / (W_{PTM} \times T_{PTM})$ (1.3)

$$R_{INS} = \rho_{INS} \times L_{PTM} / (W_{PTM} \times T_{PTM})$$

(1.4)

An important point to note is that some materials, especially those that exhibit filamentary conduction [21], [67], may not exhibit linear dependence of resistance on area ( $A_{PTM} = W_{PTM} \times T_{PTM}$ ). Similarly, the relationship between resistance and length ( $L_{PTM}$ ) may be nonlinear. For such materials with a complex dependence of the resistance on the geometry, the effective resistivities,  $\rho_{MET}$  and  $\rho_{INS}$  are defined as  $R_{INS}$  ( $A_{PTM}$ ,  $L_{PTM}$ ) × $A_{PTM}/L_{PTM}$  and  $R_{MET}$  ( $A_{PTM}$ ,  $L_{PTM}$ ) × $A_{PTM}$  / $L_{PTM}$ , respectively. Here,  $R_{INS}$  / MET ( $A_{PTM}$ ,  $L_{PTM}$ ) are insulating/metallic resistances of the selector with non-linear dependence on  $A_{PTM}$  and  $L_{PTM}$ . It can be observed that, the effective resistivities, in general, can be functions of geometry and may not be just a constant parameter. The effective resistivities can also be functions of the voltage across the selector. In addition, by virtue of similar effects,  $J_{C-IMT}$  and  $J_{C-MIT}$

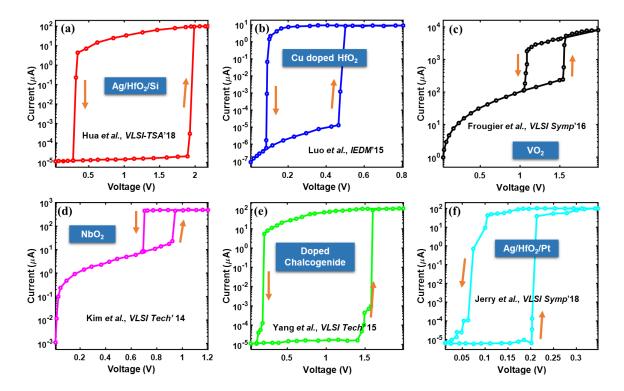

Fig. 1.2 Compilation of measured current-voltage (*I-V*) characteristics of a few phase transition materials reported in literature. (a) Ag/HfO<sub>2</sub>/Si (b) Cu-doped HfO<sub>2</sub> (c) VO<sub>2</sub> (d) NbO<sub>2</sub> (e) doped chalcogenide (f) Ag/HfO<sub>2</sub>/Pt.

may also be functions of area. Furthermore, some PTMs can exhibit unipolar (responding to only positive/negative polarity of voltage) electrical characteristics. To summarize, the prime features of the electrical characteristics of PTMs are: (a) abrupt transitions (b) high resistance ratio and (c) hysteresis. Fig. 1.2 presents the *I-V* characteristics of a few PTMs reported in literature ([21], [22], [67], [73], [78], [87]). Noticeably, all these materials have the signatures of the three major features of PTM, even though the transition mechanisms may be different.

#### **1.3** Contributions of this Dissertation

The prime target of this dissertation is to analyze the unique properties of phase transition materials and explore their applications at the device and circuit levels. We utilize a simulation-based approach to propose and verify several unique techniques to improve logic and memory designs. We establish compact models and frameworks to perform device, circuit and array level simulations. A brief overview of the major contributions and the contents of the subsequent chapters is as follows

- (a) We first explore PTM-augmented MRAM, which utilizes selective transitions of PTMs to enhance the read performance of Spin Transfer Torque (STT) MRAMs. Chapter 2 covers the details of this proposed technique.

- (b) In chapter 3, we propose a different variant of PTM augmented multi-port MRAM that utilizes separate read/write paths and provides a unique set of advantages including high sense margin and better read stability.

- (c) Chapter 4 presents a comprehensive analysis and establishes the design methodology, biasing constraints and optimization procedure for cross-point memory array with PTM based selectors.

- (d) Chapter 5 complements our extensive work on cross-point array design by directing special focus on sneak path leakage analysis. We present a computationally efficient compact modeling approach to estimate leakage in a cross-point array with PTM based threshold-switching selectors.

- (e) Chapter 6 analyzes the device-circuit co-design space for the PTM augmented steep switching transistor, called Hyper-FET. We investigate the impact of its unique device level characteristics on circuit level performance and provide directions for material down selection.

- (f) In chapter 7, we present a novel sense amplifier design with built-in reference, utilizing unique properties of phase transition materials. In addition to analyzing the performance benefits, we discuss the process to tune the reference dynamically to counter the effect of variation.

- (g) In chapter 8, we explore a unique design of using the inherent hysteresis and unipolar phase transitions in Ag/HfO<sub>2</sub>/Pt threshold switch for efficient rectification. We implement a Cockcroft-Walton voltage multiplier using Ag/HfO<sub>2</sub>/Pt based rectifiers to validate the idea and illustrate the benefits.

- (h) Chapter 9 concludes this dissertation and provides a brief discussion on some possible future directions for PTM based designs.

### 2. THRESHOLD SWITCH AUGMENTED STT MRAM

#### 2.1 Introduction

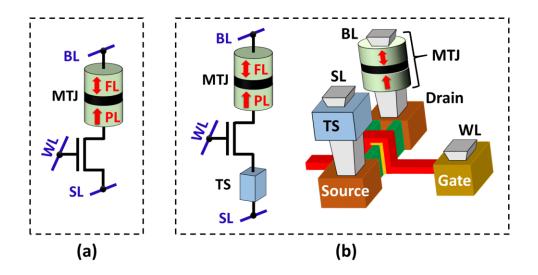

Spin Transfer Torque (STT) MRAM has drawn immense attention as a non-volatile memory device due to several promising features including high retention time, thermal stability, impressive reliability and CMOS compatibility [51], [58], [88], [89]. STT MRAM comprises of a magnetic tunnel junction (MTJ) and an access transistor (Fig. 2.1 (a)). The MTJ stores data in the form of relative magnetization between its two magnetic layers called pinned layer (PL) and free layer (FL). These two layers are separated by an oxide (usually MgO) layer, which acts as a tunnel barrier. If the FL possesses a magnetization parallel to the PL, the MTJ exhibits low resistance state (LRS) which is also referred to as parallel (P) state. On the contrary, if the magnetization of the FL is opposite to that of the PL, the MTJ presents high resistance state (HRS) or anti-parallel (AP) state.

The relative difference between resistances of P and AP states of the MTJ ( $R_P$  and  $R_{AP}$ ) respectively) is called tunneling magneto resistance (TMR). The TMR, defined as  $(R_{AP}$ - $R_P$  / $R_P$  is a direct measure of the distinguishability of the stored data in an MTJ. Despite having several favorable characteristics, a big challenge for STT MRAMs is the low inherent TMR ( $\sim < 200$  %) of the MTJ [58]. In addition, the resistance of the access transistor  $(R_{FET})$  sullies the TMR of the overall memory cell. Hence, the overall distinguishability of stored data in a STT MRAM is represented by its cell TMR (CTMR), defined as  $(R_{AP} - R_P) / (R_P + R_{FET})$ . Low CTMR of the STT MRAM yields low sense margin (SM) making it challenging to design sensing circuits [90], [91]. Thus, improving the CTMR and SM is amongst the most important needs for STT MRAM design. In addition to high distinguishability, robust read operation demands high stability of the stored data, which is measured by read disturb margin (RDM). It is necessary to ensure sufficiently high RDM and SM (or CTMR) in a memory cell [79], [92], [93]. However, the SM and RDM in a STT MRAM typically have conflicting requirements [93], [94]. In addition, the write operation shares the current path with read which results in read-write conflict and aggravates the design challenges. This is because in STT MRAMs, the MTJ undergoes

Fig. 2.1 (a) Schematic diagram of a spin transfer torque (STT) MRAM cell. (b) Schematic and 3D structure for a threshold switch augmented MRAM.

P→AP and AP→P transitions driven by *spin transfer torque* [95], [96] induced through bidirectional current flow. Write current ( $I_{WRITE}$ ) in STT MRAM needs to be larger than critical values ( $I_{CRIT: AP \rightarrow P}$  and  $I_{CRIT: P \rightarrow AP}$ ) to achieve desired switching in MTJ. The read stability and write speed have conflicting current requirements, making it challenging to improve the read performance without degrading the write performance (and *vice versa*).

Various efforts have been directed towards mitigating the design conflicts of STT MRAM [97]–[99]. Conjoining MTJ with physical phenomena like *Spin Hall effect* [97], [100], *Seebeck effect* [98] and *Rashba effect* [99] have been explored as means to overcome limitations of standard STT MRAMs. While useful in several aspects, these approaches have their own challenges in terms of fabrication complexity, variability and area impact [89]. With the emergence of new materials with unique properties, it becomes important to explore novel opportunities of designing spin-memories by employing such materials in conjunction with the MTJs. In this chapter, we present a unique approach to optimize the read operation of STT MRAM. The idea is to employ correlated material, such as  $VO_2$  [22], [30] with the STT MRAM cell (Fig. 2.1 (b)) and obtain selective phase transition in  $VO_2$  to boost the SM as well as RDM. This approach shows promise to significantly improve the read operation and moderately reduce write power with no area penalty and minimal

Fig. 2.2 Behavioral representation of the phenomenological model for threshold switch / phase transition materials.

adverse effect on write speed [79], [93]. With such advantages, it is crucial to also explore the proper design space of this novel approach and establish a proper optimization methodology. Besides, analysis to assess impact of variations is also vital. Here, we provide a comprehensive evaluation of the design space and degree of variation tolerance for this technique. Note, we first evaluated this technique using VO<sub>2</sub>, which has strong electronelectron correlation (hence, the name correlated material). But there are other physical processes like filamentary ion diffusion or dimerization [21], [67] that yield similar insulator  $\leftrightarrow$  metal switching behavior. This family of materials is often referred to as *Threshold Switch (TS)*. Any of such bi-directional TS can be used to realize the technique proposed in [93]. To ensure generality of discussion, we will henceforth use the name-Threshold Switch Augmented STT MRAM (TSA MRAM) to refer to the proposed technique.

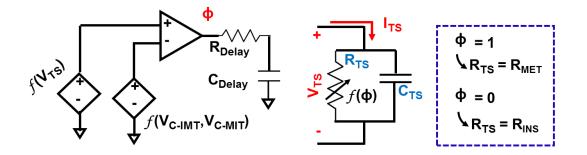

#### 2.2 Modeling and Simulation Framework

We use a phenomenological circuit-compatible SPICE model [28], [79] to simulate characteristics of TS. The model assumes constant resistance of the TS in the insulating and metallic states. The voltage across the TS ( $V_{TS}$ ) is compared to the critical levels ( $V_{C-IMT}$  and  $V_{C-MIT}$ ) to decide on the *phase* (and thereby its resistance,  $R_{TS}$ ). Hence, the resistance switching behavior of the TS is invoked self-consistently in correlation with the biasing scenario. Fig. 2.2 shows the behavioral representation of this model. We calibrate this model with *I-V* characteristics of epitaxial VO<sub>2</sub> films reported in [6]. In addition to the

TS model, we use a physical model for the MTJ from [101]. We choose an MTJ with perpendicular magnetic anisotropy [102]. We use 20 nm predictive technology model [103] for the access transistor. The relevant parameters have been summarized in Table 2.1.

|      |                                          | Parameters                    | Value                             |  |

|------|------------------------------------------|-------------------------------|-----------------------------------|--|

|      |                                          | $R_{MET}$ , $R_{INS}$         | 0.5 ΚΩ, 100 ΚΩ                    |  |

| ST   | I <sub>C-IMT</sub> , I <sub>C-MIT</sub>  |                               | 3.6 µA, 45 µA                     |  |

| E    | $T_{IMT}$ , $T_{MIT}$                    |                               | 500 ps, 1 ns                      |  |

|      | L, Area, Intrinsic capacitance           |                               | 45 nm, 4500 nm <sup>2</sup> , 1fF |  |

|      | Diameter, Oxide thickness $(T_{OX-MTJ})$ |                               | 40 nm, 1.1 nm                     |  |

| LJ   | Thickness of free layer                  |                               | 1.5 nm                            |  |

| MTJ  |                                          | Saturation magnetization      | 700 KA/V                          |  |

|      | En                                       | ergy barrier, Gilbert Damping | 56 K <sub>B</sub> T, 0.028        |  |

| Tron | ransistor Technology node, # of Fins     |                               | 20 nm, 4                          |  |

| Iran | 515101                                   | Fin height and Fin width      | 28 nm, 15 nm                      |  |

Table 2.1 List of Parameters Used for Simulation of STT and TSA MRAMs

### 2.3 **Principle of Operation**

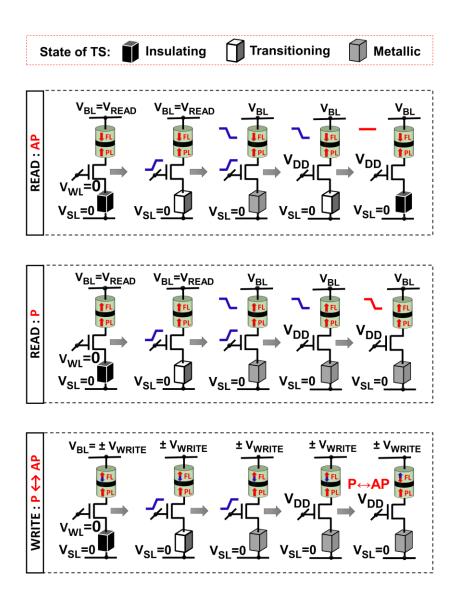

TSA MRAM has a TS connected in series with the standard STT MRAM structure (Fig. 2.1). The TS and the MTJ are connected to opposite terminals (*source* and *drain*) of the access transistor (reason discussed later). Fig. 2.3 illustrates the principle of operation for the TSA MRAM. The target is to trigger selective phase transitions in the TS during read, depending on the stored data in MTJ. The bit line (BL) is pre-charged to read voltage ( $V_{READ}$ ) and kept floating during read. After this, word line (WL) is asserted. The resulting increase in current through the cell ( $I_{CELL}$ ) triggers IMT and drives the TS to metallic state (irrespective of the stored data in MTJ). The BL voltage ( $V_{BL}$ ) starts to discharge through the memory cell. With the TS in the metallic state, the resistance of the cell is mainly governed by the MTJ. An MTJ storing P state presents less resistance in discharge path and allows larger current flow compared to an AP MTJ. Hence, the TS can remain in metallic state with an MTJ in P state throughout the entire read time span ( $T_{READ}$ ). Conversely, the MTJ with AP state produces much lower  $I_{CELL}$ . Hence,  $I_{CELL}$  in AP state can quickly fall below  $I_{C.MIT}$ , triggering MIT in the TS (by design). Eventually, throughout

Fig. 2.3 Principle of operation for TSA MRAM.

most part of the read operation, TS exhibits its metallic state with a P MTJ and insulating state with AP MTJ. As a result, effective resistance in HRS of the cell becomes,  $R_{HRS-TS} \approx$  $(R_{AP}+R_{FET}+R_{INS})$  and in LRS of the cell becomes,  $R_{LRS-TS} \approx (R_P+R_{FET}+R_{MET})$ . In a standard STT MRAM,  $R_{HRS-STD} \approx (R_{AP}+R_{FET})$  and  $R_{LRS-STD} \approx (R_P+R_{FET})$ . Since,  $R_{INS} >> \max[R_{MET}, R_P, R_{AP}]$  the TSA MRAM exhibits significantly high (quantified later) relative resistance difference compared to standard STT MRAM, yielding high CTMR and SM. In addition, an immense increase in cell resistance during AP read leads to reduction in corresponding read current ( $I_{READ-AP}$ ). This reduction in read current ( $I_{READ}$ ) can be utilized to reduce accidental data flipping. We choose a biasing polarity for read, which restricts  $P \rightarrow AP$ switching [93][104]. Hence, only  $AP \rightarrow P$  flipping is possible and the RDM can be defined by: 1-( $I_{READ-AP}/I_{CRIT: AP \rightarrow P}$ ). As,  $I_{READ-AP}$  is significantly less, TSA MRAM can achieve much higher RDM compared to STT MRAM. For the write operations, the TS needs to be triggered and maintained in metallic state throughout  $AP \rightarrow P$  and  $P \rightarrow AP$  write to avoid incurring much write penalty due to TS resistance. As  $|I_{WRITE}| > I_{READ}$ , this can be ensured by designing the cell to achieve  $|I_{WRITE}| > I_{C-MIT}$ . During write, the TS undergoes IMT on assertion of the WL (as during read) and then remains in metallic state with a sufficiently high write voltage ( $V_{WRITE}$ ).

#### 2.4 Design Approach for TSA MRAM

The above description conceptually conveys the idea behind TSA MRAM. However, to achieve the desired selective phase transitions in TS, a meticulous design approach needs to be followed, which we discuss next.

|                 | Term               | Significance                                      | Figure                   |

|-----------------|--------------------|---------------------------------------------------|--------------------------|

| V               | IZ.                | The $V_{CELL}$ at which the metallic TS in a TSA  | 3 (a): (V <sub>1</sub> ) |

| V CE            | ELL-MIT-(AP) / (P) | MRAM with AP / P MTJ undergoes MIT.               | 3 (a): (V <sub>2</sub> ) |

|                 |                    | The $V_{CRU}$ at which the insulating TS in a TSA | 3 (b): (V <sub>3</sub> ) |

| V <sub>CE</sub> |                    | MRAM with AP / P MTJ undergoes IMT.               | 3 (a): (V <sub>4</sub> ) |

Table 2.2 Design Space Related Terminologies for TSA MRAM

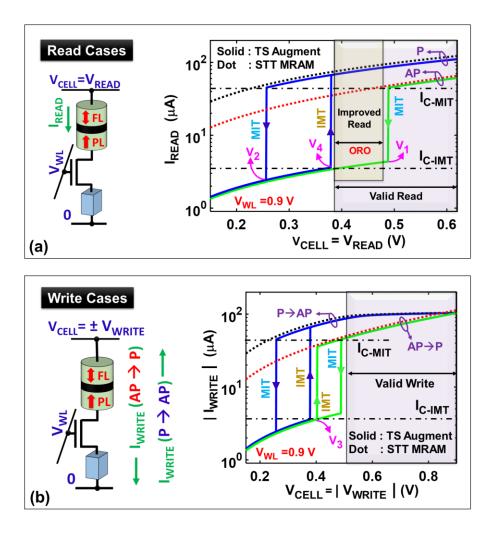

#### 2.4.1 Biasing Constraints

An important step to design a TSA MRAM is to deduce appropriate ranges for  $V_{READ}$  and  $V_{WRITE}$ , which enable the aforementioned phase transitions in TS. In Table 2.2, we define important threshold points of the cell voltage ( $V_{CELL}$ ). Let us consider the read operation first. Fig. 2.4 (a) shows the  $I_{READ}$  versus  $V_{READ}$  plot for TSA and STT MRAM. Recall, after the initial IMT (due to assertion of WL), the TS should remain in metallic state for P MTJ and revert to insulating state for AP MTJ. Hence,  $V_{READ}$  needs to be less than  $V_{CELL-MIT-(AP)}$  and greater than  $V_{CELL-MIT-(P)}$ . Therefore, the first condition to fulfil is,

14

On a different note, the TSA MRAM needs to be able to trigger IMT in TS (after assertion of the WL) at the chosen  $V_{READ}$ . So, another condition for  $V_{READ}$  is-

$$V_{READ} > V_{CELL-IMT-(P)}$$

(2.2)

Note, the above condition is defined for P MTJ since triggering the WL driven initial IMT is not a requirement for AP MTJ (as the TS will eventually revert to insulating state). For the case of P MTJ, the TS needs to be stable (non-oscillatory [30]) in metallic state throughout the read operation. Such stable operation demands,

Fig. 2.4 Feasible range of bias voltage to ensure desired phase change in the threshold switch during (a) read and (b) write operations.

On the contrary, oscillatory mode may arise while reading AP MTJ. In such a scenario, voltage distribution among the series connected AP MTJ, transistor and TS yields  $V_{CELL-IMT-(AP)} < V_{CELL-MIT-(AP)}$  (Fig. 2.4 (b)) and thereby results in oscillations [82], [105]. It is important to mention, this oscillatory mode is not mandatory for the TSA MRAM design and it may or may not occur depending on the relative resistance of the TS, MTJ and the access transistor. In fact, the discharging BL suppresses the oscillation in TS (if present) due to  $I_{CELL}$  reduction, which drives and keeps TS into the insulating state. Hence,  $V_{CELL-IMT-(AP)}$  can be greater or less than  $V_{CELL-MIT-(AP)}$ . Combining, (2.1), (2.2) and (2.3) we get the condition that yields the desired operation as –

$$V_{CELL-IMT-(P)} < V_{READ} < V_{CELL-MIT-(AP)}$$

$$(2.4)$$

The range of  $V_{READ}$  that complies with (2.4), will be referred to as the optimum range of operation (ORO) hereafter (marked in Fig. 2.4 (a)). This represents the region in which TSA MRAM exhibits improved read over STT MRAM. Another point to mention is that, for  $V_{READ} > \max \left[ V_{CELL-MIT-(AP)}, V_{CELL-IMT-(AP)} \right]$ , the TS will be in metallic state for both P and AP states of MTJ. Since metallic TS incurs only a small increase in the resistance, the TSA MRAM will still be able to achieve read functionality with mildly degraded performance compared to STT MRAM. Since, in this scenario the read functionality is maintained, this range has been marked as region for valid read in Fig. 2.4 (a). Note, the DC response (Fig. 2.4 (a)) shows an abrupt boundary between ORO and valid read regions. But due to transient effects (discussed later), TSA MRAM may exhibit benefits over the STT MRAM even when it is biased within valid region close to the ORO boundary. However, to ensure the desired benefit from the TSA MRAM, it is necessary to choose the  $V_{READ}$  from within the ORO (complying with (2.4)). Similarly, it is also necessary to establish a range for  $V_{WRITE}$  Fig. 2.4 (b) shows  $I_{WRITE}$  versus  $V_{WRITE}$  characteristics for TSA and STT MRAMS. Clearly, if the TS can be maintained in metallic state with AP MTJ, it will be metallic with P MTJ. Hence, the following constraint is enough to enforce the TS to be in metallic state during write-

(2.3)

The constraints described so far are based on DC considerations. We next evaluate the transient operation of the TSA MRAM and present additional design insights.

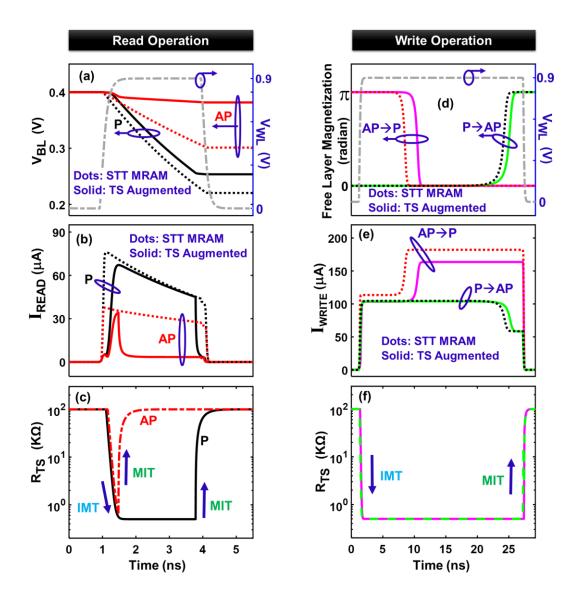

# 2.4.2 Transient Aspects of TSA MRAM Operation

Simulated transient waveforms for the read/write operation of STT and TSA MRAM have been illustrated in Fig. 2.5. Note, standard STT MRAMs may employ sensing mechanisms other than the one depicted here [57], [106], [107]. But, to understand the impact of TS on

Fig. 2.5 Simulated transient response for (a-c) read and (d-f) write operations.

the read operation of the TSA MRAM, we compare STT and TSA MRAMs considering a similar sensing scheme.  $V_{BL}$  starts discharging after assertion of the WL (Fig. 2.5 (a)). For STT MRAM, a difference in the extents of BL discharge occurs solely due to the difference between  $R_P$  and  $R_{AP}$ . However, for TSA MRAM, the discharge for AP MTJ drastically reduces after TS undergoes MIT (as R<sub>INS</sub> is large). Fig. 2.5 (b) shows the discharge current during the read operation. The TSA MRAM initially shows almost similar levels of discharge current as in a STT MRAM for both P and AP cases. That occurs due to the TS being in metallic state for both cases in the beginning of the read cycle. Note,  $V_{READ}$  has been chosen based on constraint (2.4). Therefore, after the initial IMT, the TS undergoes MIT for AP case (Fig. 2.5 (c)). During the major part of the read operation, the AP MTJ is accompanied with an insulating TS and the discharge becomes very low. But, the TS with P MTJ supports almost as high discharge current as in a standard STT MRAM storing P. Thus, for TSA MRAM, a larger voltage differential ( $\Delta V_{BL}$ ) is developed between BLs for P and AP cases. Note, due to the discharging BL, the voltage across the TS with P MTJ will also reduce below  $V_{C-MIT}$ , if the WL is kept asserted for sufficiently long period. In that scenario, the TS with P MTJ will also exhibit MIT and  $\Delta V_{BL}$  will get saturated (Fig. 2.5 (a)). Hence, ideally, the WL can be de-asserted prior to reaching this saturation condition.

The write operation of TSA MRAM does not impose any additional design constraints in terms of the transient response. The write time ( $T_{WRITE}$ ) for the TSA MRAM is slightly (~3%) larger than that of the STT MRAM (Fig. 2.5 (d)). The reason is the slight reduction of  $I_{WRITE}$  due to the resistance of the metallic TS (Fig. 2.5 (e, f)). Such minute write penalty is observed for low  $R_{MET}$  (< 1 K $\Omega$ ). Also note, the reduction in  $I_{WRITE}$  is more prominent in AP→P switching, whereas the P→AP switching experiences only mild reduction in  $I_{WRITE}$  (Fig. 2.5 (e)). This is related to the source degeneration of the access transistor. For AP→P transition, the TS contributes to reducing  $I_{WRITE}$  by presenting a series resistance ( $R_{MET}$ ) and simultaneously source degenerating the access transistor. As a result, the effect of  $R_{MET}$  on AP→P write is large and leads to ~30% slower switching than standard STT MRAM. Note, lower  $I_{WRITE}$  also translates to significantly reduced (~10%) power for AP→P switching. But, for P→AP transition, the TS only provides a series resistance ( $R_{MET}$ ). The access transistor in this case is source degenerated by the MTJ, as in standard STT MRAMs [51],

[58]. Hence, the effect of  $R_{MET}$  is very low leading to only 3% write time increase with similar P→AP switching power. Note, for MRAM write, P→AP transition is the bottleneck (due to MTJ induced source degeneration) [93], [108] and hence,  $T_{WRITE}$  is determined by the P→AP transition time ( $T_{P \rightarrow AP}$ ). Note, augmenting the TS on the same side as the MTJ will cause stronger source degeneration during P→AP switching and therefore will lead to much longer  $T_{WRITE}$ . We avoid that by connecting the MTJ and TS to opposite terminals of the access transistor.

Interestingly, the connection of the TS and the MTJ to the opposite end of the transistor, leads to a mild mitigation of asymmetry in the write operation [79], [93]. Standard STT MRAMs typically exhibit a large difference in the switching time for  $P \rightarrow AP$  and  $AP \rightarrow P$ transitions. This is due to the bi-directional write current, which leads to the source degeneration of the access transistor for just one of the state transitions. As a result, the write time is determined by the switching time for the case when current flows from source line (SL) to BL (i.e. when the access transistor is source-degenerated) [93], [108]. Consequently, significant energy is wasted unnecessarily when current flows from BL to SL. In TSA MRAM, the access transistor gets source degenerated for both the directions of the current flow. When current flows from SL to BL, the MTJ resistance leads to the source-degeneration, as in the standard STT MRAMs. When the current flows from BL to SL, the metallic resistance of the CM results in source degeneration (albeit the effect is mild). This moderately reduces the excessive write current in the cell, leading to write power savings. Eventually, the TSA MRAM suffers from a mild increase (~3%) in write time, but consumes ~10% less power compared to STT MRAM.

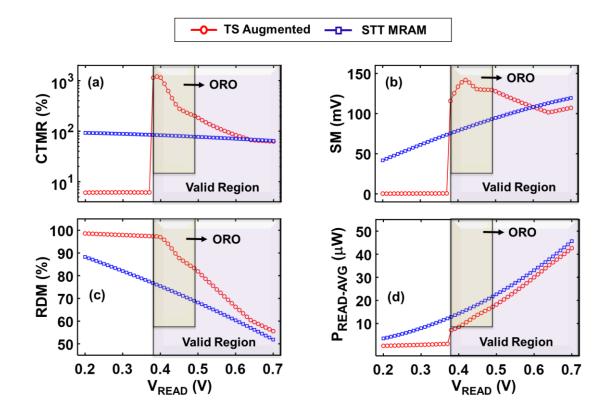

### 2.4.3 Optimization of Performance Metrics with Biasing

So far, we have directed our attention towards ensuring the desired transitions in TSA MRAM. In this sub-section, we quantify the performance metrics. Let us start with the read operation. The transient interplay between the phase transitioning TS and the remainder of the memory cell leads to non-monotonous trends in performance metrics with respect to  $V_{READ}$ . Fig. 2.6 (a-d) show comparative trends for some important read performance metrics. These metrics have been calculated by simulating the transient read operation of the STT

and TSA MRAM for different  $V_{READ}$ . Hence, the trends seen in these results carry signature of the transient correlation between different components of TSA MRAM.

The TSA MRAM shows up to ~ 15X boost in CTMR (Fig. 2.6 (a)) for  $V_{READ}$  chosen from within the ORO (marked in Fig. 2.4 (a)). The improvement in CTMR is prominent for lower  $V_{READ}$  (< 0.45 V) within the ORO because of two reasons. Firstly, the inherent TMR of the MTJ is larger for lower  $V_{READ}$ . Secondly, the TS with AP state MTJ can quickly go back to insulating state if the BL is pre-charged with lower  $V_{READ}$ . Hence, the CTMR is maximized for lower  $V_{READ}$  (within ORO). Similar explanation applies for RDM and the average read power ( $P_{READ-AVG}$ ) (Fig. 2.6 (c, d)). Lower  $I_{READ-AP}$  results in reduction of the read power. For lower  $V_{READ}$  (< 0.45 V) within the ORO, we get ~27% enhancement in RDM and ~40% reduction in  $P_{READ-AVG}$ . The SM, however shows slightly complex and nonmonotonic trend with  $V_{READ}$ . Note, the SM is defined as ( $V_{BL-AP} - V_{BL-P}$ )/2. Here,  $V_{BL-P}$  and

Fig. 2.6 Comparison of (a) cell tunneling magneto resistance (b) sense margin (c) read disturb margin and (d) average read power of STT and TSA MRAMs at different  $V_{READ}$ .

$V_{BL-AP}$  represent the values of  $V_{BL}$  at  $t = T_{READ}$  for P and AP cases (respectively). As shown in Fig. 2.6 (b), the SM for the TSA MRAM increases with  $V_{READ}$  (within the ORO) up to  $V_{READ} \approx 0.45$ V. If a larger  $V_{READ}$  is chosen, the TS with AP MTJ, stays in metallic state longer, as the BL voltage takes more time to discharge below  $V_{CELL-MIT-(AP)}$ . Therefore, the initial discharge rates for both P and AP cases are high. By the time the TS undergoes MIT, the difference between  $V_{BL-AP}$  and  $V_{BL-P}$  gets slightly reduced and hence, the SM tends to decrease as  $V_{READ}$  increases beyond 0.45 V. Note, in all of these cases, the SM of the TSA MRAM is always much greater (~1.5X to 1.7X) than that of STT MRAM. Considering all these, it is optimal to choose  $V_{READ}$  for the TSA MRAM from within the lower portion (0.4-0.45V) of the ORO. Note, Fig. 2.6 (a-d) show performance improvements in TSA MRAM even beyond the ORO. This is a manifestation of the transient dynamics of the TS.

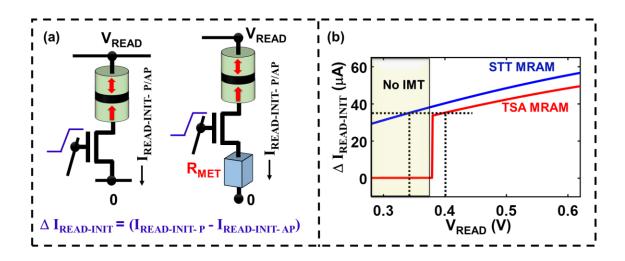

In addition to these trends, another important aspect needs to be considered to choose  $V_{READ}$  for TSA MRAM. Recall, the TSA MRAM initially (on assertion of WL) triggers IMT in the TS irrespective of the state of the MTJ. Then, based on the relative values of  $I_{READ}$ , the TS can either remain metallic or undergo MIT. This critical decision to trigger selective transition in TS is dependent on the difference of the initial  $I_{READ}$  with P and AP MTJ. We denote this quantity as  $\Delta I_{READ-INIT}$ . Compared to a STT MRAM at *iso-V<sub>READ</sub>*, the TSA MRAM exhibits less  $I_{READ-INIT}$  due to having an additional resistance ( $R_{MET}$ ) in series (Fig.

Fig. 2.7 (a) Illustration of  $I_{READ-INIT}$  and (b) the concept of achieving *iso*- $\Delta I_{READ-INIT}$  between STT and TSA MRAMs.

2.7 (a, b)). To make sure that the robustness of the selective phase transition is not compromised due to the additional resistance, we choose a higher  $V_{READ}$ , for TSA MRAM operation. To maintain same levels of  $\Delta I_{READ-INIT}$  (Fig. 2.7 (b)), we use  $V_{READ} = 0.35$  and 0.4 V for STT and TSA MRAM respectively (for subsequent analyses). Note, the TSA MRAM permits use of higher  $V_{READ}$  without hurting the read stability, as it has significantly higher RDM compared to STT MRAM (Fig. 2.6 (c)).

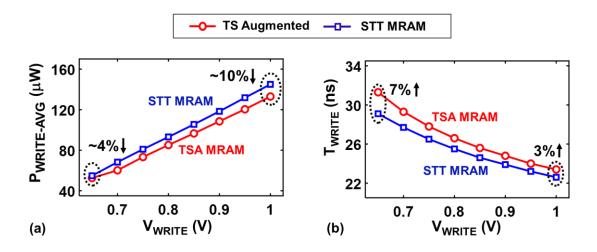

Fig. 2.8 (a, b) show the comparison for the write metrics.  $|I_{WRITE}|$  for TSA MRAM is less than that of STT MRAM due to  $R_{MET}$ . That translates to lower average write power ( $P_{WRITE-AVG}$ ) as shown in Fig. 2.8 (a). Actually, the power for AP $\rightarrow$ P transition in TSA MRAM is much less than that in STT MRAM. But, P $\rightarrow$ AP transition consumes almost same power for both cases. This difference is attributed to the source degeneration of the access transistor due to  $R_{MET}$  in the former case, as discussed before (in section 2.4.2). Recall, in the latter case, MTJ induced source degeneration determines  $I_{WRITE}$ , which reduces the effect of  $R_{MET}$ . On average, the TSA MRAM shows ~4-10% reduction in  $P_{WRITE}$  within the acceptable range of  $V_{WRITE}$ . Fig. 2.8 (b) shows that the TSA MRAM incurs slight increase (~3 to 7%) in  $T_{WRITE}$ , the reasons for which have been discussed in previous sub-section. In summary, it is important to choose a  $V_{READ}$  from within an appropriate range to ensure desired selective phase transitions. TSA MRAM can achieve significant boost in CTMR

Fig. 2.8 (a) Average write power and (b) write time as functions of  $V_{WRITE}$  for STT and TSA MRAMs.

(and hence SM) and RDM without much degradation in write performance. The design technique discussed in this section provides insights on bias selection for a given set of parameters of the TS (Table 2.1). However, the resistance and transition thresholds of the TS can be chosen/tailored to alter the optimum biasing range, which we discuss next.

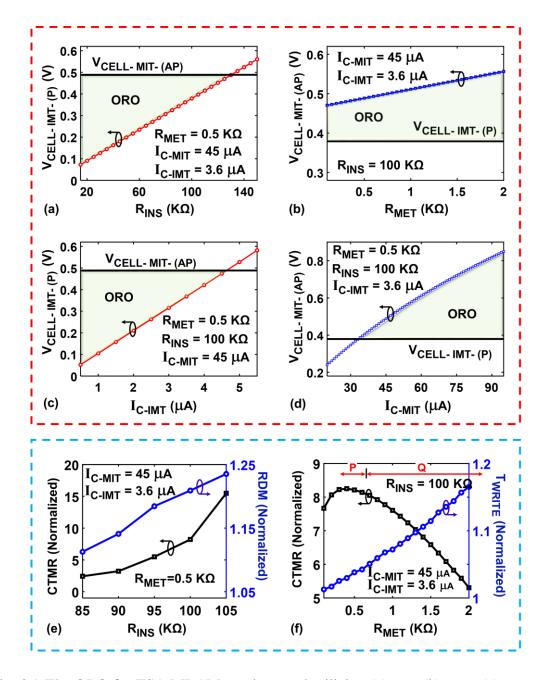

Fig. 2.9 The ORO for TSA MRAM can be tuned utilizing (a)  $R_{INS}$  (b)  $R_{MET}$  (c)  $I_{C-IMT}$  and (d)  $I_{C-MIT}$ . (e) Change in  $R_{INS}$  has major impact on CTMR and RDM. (f)  $R_{MET}$  primarily shows impact on CTMR and  $T_{WRITE}$ .

#### 2.5 Tuning Design Space with TS Parameters