## BUILDING FAST, SCALABLE, LOW-COST, AND SAFE RDMA SYSTEMS IN

### DATACENTERS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Shin-Yeh Tsai

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2019

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Yiying Zhang, Chair

School of Electrical and Computer Engineering

Dr. Mathias Payer

Department of Computer Science

Dr. Tiark Rompf

Department of Computer Science

Dr. He Wang

Department of Computer Science

## Approved by:

Dr. Voicu S. Popescu

Department of Computer Science

Dedicated to my family for their love and support

#### ACKNOWLEDGMENTS

This dissertation would not have been possible without the support from many people in my life. First of all, I would like to express my sincerest gratitude to my advisor Professor Yiying Zhang for her support, patience, and listening. I really appreciate that she gave me a chance to do research with her. By working with her, I have learned how to discover a research problem, how to build a system to verify ideas, and how to take broad, high-level ideas and to be able to focus on those ideas in a more nuanced, focused way.

I still remember the time that Professor Zhang and I worked together for my first research project, and the impressive moment that we were notified the project is accepted to be published. In the early stage of the project, she gave me tremendous suggestions to improve the designs. When we were consolidating our ideas and writing the paper, she taught me how to write in a technical style and helped me to polish and improve the contents. After the paper is accepted, she taught me how to prepare an excellent presentation and how to illustrate our ideas in the presentation clearly. I have learned so much from Professor Zhang, and I would not be able to complete this work without her gratuitous support.

I would also like to thank the members of my committee: Professor Mathias Payer, Professor Tiark Rompf, and Professor He Wang. Their feedback about my dissertation and research has made my work significantly stronger. I would particularly like to thank Professor Payer for his insightful comments and suggestions. It was an enjoyable experience to collaborate with him to discover exciting research ideas.

It was also a pleasure to be a member of an awesome research group, WukLab. I thank them for their input and support of my work. Their feedback about my ideas has made my work better. Finally, I am immensely grateful to my family, especially my parents, who encouraged me to pursue this work and provide their unconditional love through the whole process. I acknowledge my mom for her endless patience and understanding. I miss my maternal grandfather and my paternal grandmother so much. The life lessons they taught me and what I have learned during my Ph.D. journey will be in my heart forever. I dedicate this dissertation to my family.

## TABLE OF CONTENTS

|    |              |                 |                                                                                                    | Р   | age           |

|----|--------------|-----------------|----------------------------------------------------------------------------------------------------|-----|---------------|

| LI | ST O         | F TAB           | LES                                                                                                |     | ix            |

| LI | ST O         | F FIGU          | JRES                                                                                               |     | x             |

| AI | BSTR         | ACT             |                                                                                                    |     | xiii          |

|    |              |                 |                                                                                                    |     |               |

| 1  | 1NT<br>1.1   | RODU(           |                                                                                                    |     | $\frac{1}{3}$ |

|    | $1.1 \\ 1.2$ |                 | ction Layer on RDMA for Better Datacenter Support A-Based Data Store with Remote Persistent Memory |     | 3<br>4        |

|    | $1.2 \\ 1.3$ |                 | ty Implications of One-Sided Communication and RDMA                                                |     | 4             |

|    | 1.4          |                 | er Overview                                                                                        |     | 5             |

| 0  |              | -               |                                                                                                    |     |               |

| 2  | ВАС<br>2.1   | KGRO            | UND                                                                                                |     |               |

|    | 2.1          | 2.1.1           | Architecture and Abstraction                                                                       |     |               |

|    |              | 2.1.1<br>2.1.2  | RDMA NICs                                                                                          |     | 10            |

|    |              | 2.1.3           | RDMA Microbenchmarks                                                                               |     |               |

|    |              | 2.1.4           | RDMA in Datacenter Applications                                                                    |     | 13            |

|    | 2.2          | Datace          | enter In-Memory Data Stores                                                                        |     | 14            |

|    |              | 2.2.1           | Distributed and Remote DRAM-Based Data Stores                                                      |     | 14            |

|    |              | 2.2.2           | Distributed Persistent Memory Data Stores                                                          |     |               |

|    |              | 2.2.3           | RDMA Data Stores                                                                                   |     | 16            |

|    | 2.3          | Side-C          | Channel Attacks                                                                                    | • • | 16            |

| 3  | IND          |                 | ION LAYER ON RDMA FOR BETTER DATACENTER SUP-                                                       |     |               |

|    | POF          |                 | • • • • • • • • • • • • • • • • • • • •                                                            |     | 18            |

|    | 3.1          |                 | of RDMA                                                                                            |     |               |

|    |              | 3.1.1           | Issue 1: Mismatch in Abstractions                                                                  |     |               |

|    |              | 3.1.2           | Issue 2: Unscalable Performance                                                                    |     |               |

|    | 3.2          | 3.1.3<br>Vintus | Issue 3: Lack of Resource Sharing, Isolation, and Protection                                       |     |               |

|    | 3.2          | 3.2.1           | lizing RDMA in Kernel: a Design Overview                                                           |     |               |

|    |              | 3.2.1<br>3.2.2  | Challenges                                                                                         |     |               |

|    |              | 3.2.3           | LITE Overall Architecture                                                                          |     | $20 \\ 27$    |

|    |              | 3.2.4           | LITE Design Principles                                                                             |     |               |

|    | 3.3          |                 | Memory Abstraction and RDMA                                                                        |     |               |

|    |              | 3.3.1           | LITE Memory Abstraction and Management                                                             |     |               |

|    |              | 3.3.2           | LITE RDMA Benefits and Performance                                                                 |     |               |

|   |     |        |                                             | -  | Page |

|---|-----|--------|---------------------------------------------|----|------|

|   | 3.4 | LITE   | RPC                                         |    | . 38 |

|   |     | 3.4.1  | LITE RPC Mechanism                          | •  | . 39 |

|   |     | 3.4.2  | Optimizations between User-Space and Kernel |    |      |

|   |     | 3.4.3  | LITE RPC Performance and CPU Utilization    | •  | . 44 |

|   | 3.5 | Resour | rce Sharing and QoS                         | •  | . 47 |

|   |     | 3.5.1  | Resource Sharing                            |    |      |

|   |     | 3.5.2  | Resource Isolation and QoS                  | •  | . 49 |

|   | 3.6 | Extend | ded Functionalities                         |    |      |

|   |     | 3.6.1  | Memory-Like Operations                      |    |      |

|   |     | 3.6.2  | Synchronization and Atomic Primitives       | •  | . 51 |

|   | 3.7 | LITE   | Applications                                | •  | . 52 |

|   |     | 3.7.1  | Distributed Atomic Logging                  |    |      |

|   |     | 3.7.2  | MapReduce                                   |    | . 53 |

|   |     | 3.7.3  | Graph Engine                                |    | . 55 |

|   |     | 3.7.4  | Kernel-Level DSM                            |    | . 56 |

|   |     | 3.7.5  | Programming Experience                      |    |      |

|   | 3.8 | Movin  | g LITE to User Space                        |    | . 59 |

|   | 3.9 | Conclu | usion                                       |    | . 59 |

| 4 | RDN | ЛА-ВА  | SED DATA STORE WITH REMOTE PERSISTENT MEMOI | RY | 60   |

|   | 4.1 |        | Overview                                    |    |      |

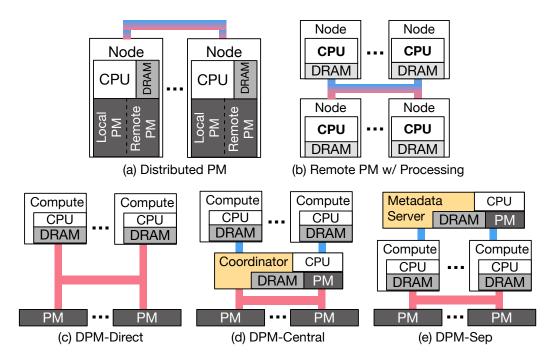

|   |     | 4.1.1  | DPM Deployment and Architectures            |    |      |

|   |     | 4.1.2  | DPM Benefits and Challenges                 |    |      |

|   |     | 4.1.3  | Design DPM for Read-Most Data Stores        |    |      |

|   | 4.2 | DPM    | Data Stores                                 |    |      |

|   |     | 4.2.1  | System Interface and Overview               |    |      |

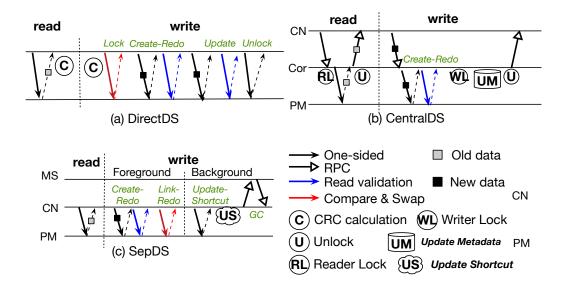

|   |     | 4.2.2  | Direct Connection                           |    |      |

|   |     | 4.2.3  | Connecting Through Coordinator              |    | . 72 |

|   |     | 4.2.4  | Separating Data and Control                 |    |      |

|   |     | 4.2.5  | Failure Handling                            |    | . 81 |

|   |     | 4.2.6  | Load Balancing                              |    |      |

|   | 4.3 | Evalua | ation Results                               |    | . 84 |

|   |     | 4.3.1  | Micro-Benchmark Results                     |    | . 86 |

|   |     | 4.3.2  | YCSB Results                                |    | . 87 |

|   | 4.4 | Conclu | usion                                       |    | . 94 |

| 5 | SEC | URITY  | IMPLICATIONS OF ONE-SIDED COMMUNICATION ANI | )  |      |

| 0 |     | ла     |                                             |    | . 95 |

|   | 5.1 | Vulner | rabilities in One-Sided Communication       |    |      |

|   | 5.2 |        | a: Remote Oracles for the Masses            |    | 101  |

|   |     | 5.2.1  | Threat Model                                |    | 103  |

|   |     | 5.2.2  | Side-Channel Attacks on RDMA                |    | 104  |

|   |     | 5.2.3  | Attacking Real RDMA-Based Systems           |    |      |

|   |     |        |                                             |    |      |

|    |     |                                                                                                            | Page |

|----|-----|------------------------------------------------------------------------------------------------------------|------|

|    |     | 5.2.4 Mitigation Techniques                                                                                | 131  |

|    |     | 5.2.5 Discussion $\ldots$ | 133  |

|    | 5.3 | Opportunity of One-Sided Communication                                                                     | 135  |

|    | 5.4 | Conclusion                                                                                                 | 138  |

| 6  | REL | ATED WORK                                                                                                  | 139  |

|    | 6.1 | User-Level TCP/IP Implementation                                                                           | 139  |

|    | 6.2 | RDMA-Based Libraries                                                                                       | 140  |

|    | 6.3 | RDMA-Based Key-Value Stores                                                                                | 140  |

|    | 6.4 | One-Sided and Two-Sided Primitives in RDMA-Based Systems                                                   | 141  |

|    | 6.5 | Distributed PM Systems                                                                                     | 142  |

|    | 6.6 | Remote Side-Channel Attacks                                                                                | 143  |

| 7  | CON | NCLUSION                                                                                                   | 144  |

|    | 7.1 | Lessons Learned and Discussion                                                                             | 145  |

|    |     | 7.1.1 Moving from HPC to Datacenters                                                                       | 145  |

|    |     | 7.1.2 Hardware Offloading                                                                                  | 146  |

|    |     | 7.1.3 One-Sided vs. Two-Sided Communication                                                                | 147  |

|    | 7.2 | Concluding Remarks                                                                                         | 148  |

| RE | FER | RENCES                                                                                                     | 150  |

| VĽ | ГА  |                                                                                                            | 174  |

## LIST OF TABLES

| Table |                                        |   | age |

|-------|----------------------------------------|---|-----|

| 3.1   | Major LITE APIs.                       |   | 28  |

| 3.2   | LITE Application Implementation Effort |   | 58  |

| 4.1   | Design Comparison of DPM Data Stores   | • | 67  |

| 4.2   | Cost Comparison of DPM Data Stores     |   | 68  |

## LIST OF FIGURES

| Figu | re P                                                     | age |

|------|----------------------------------------------------------|-----|

| 2.1  | Latency of RDMA Requests                                 | 11  |

| 2.2  | Throughput of RDMA Requests.                             | 12  |

| 3.1  | Traditional RDMA Stack.                                  | 19  |

| 3.2  | LITE Architecture.                                       | 20  |

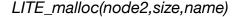

| 3.3  | LITE $lh$ Example                                        | 32  |

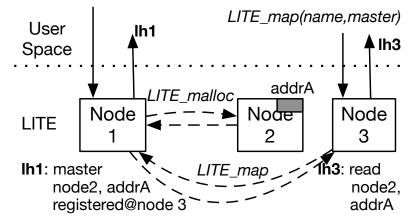

| 3.4  | RDMA Write Latency against Num of (L)MRs                 | 33  |

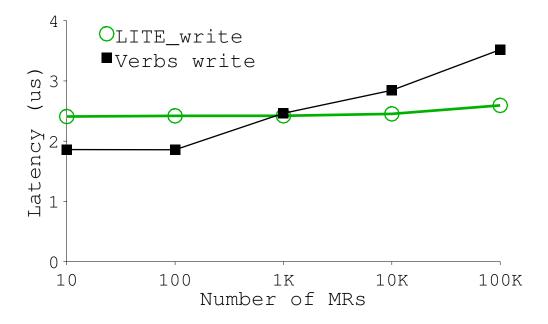

| 3.5  | RDMA Write Throughput against (L)MR Size                 | 34  |

| 3.6  | LITE and Native RDMA Write Latency.                      | 35  |

| 3.7  | LITE RDMA Throughput                                     | 37  |

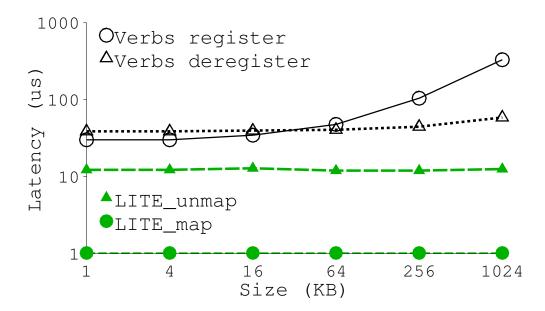

| 3.8  | (De)Registering (L)MR Latency under LITE and native RDMA | 38  |

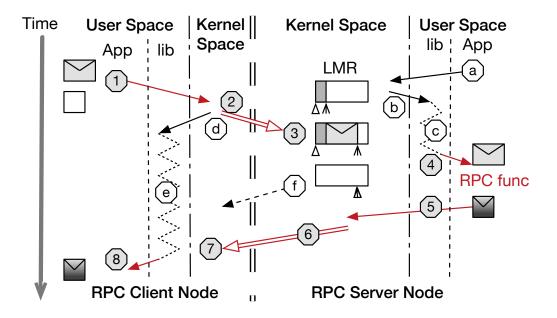

| 3.9  | LITE RPC Mechanism.                                      | 39  |

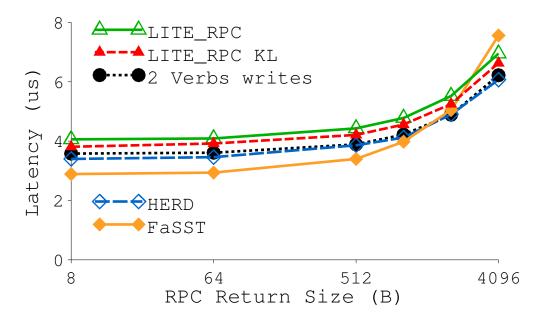

| 3.10 | RPC Latency Comparison                                   | 40  |

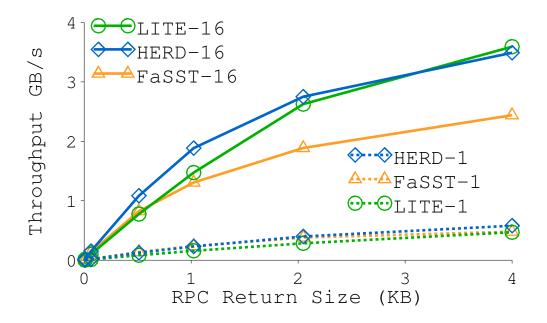

| 3.11 | RPC Throughput.                                          | 42  |

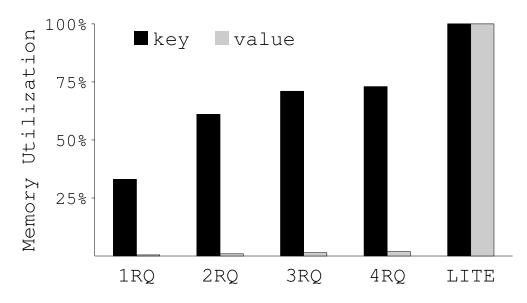

| 3.12 | LITE RPC Memory Utilization                              | 43  |

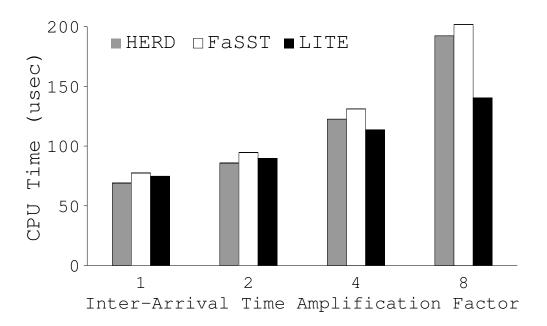

| 3.13 | CPU Usage with Facebook Distribution.                    | 45  |

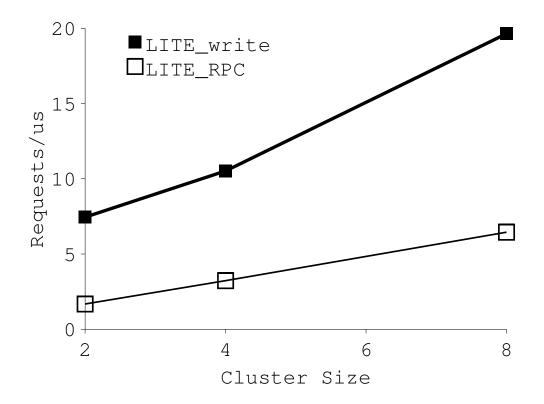

| 3.14 | Scalability of LITE RDMA and RPC                         | 46  |

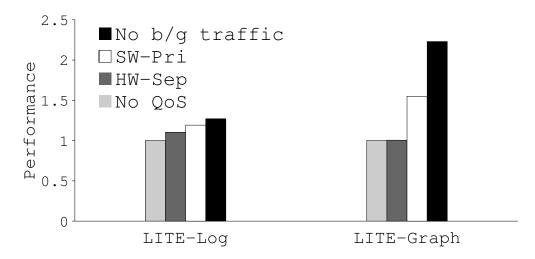

| 3.15 | LITE QoS with Real Applications.                         | 47  |

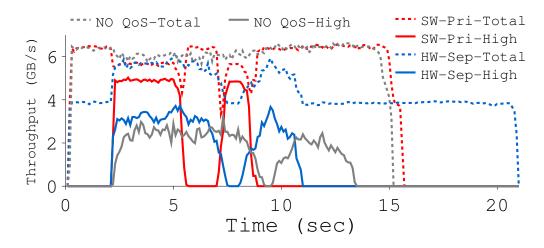

| 3.16 | LITE QoS under Synthetic Workload.                       | 48  |

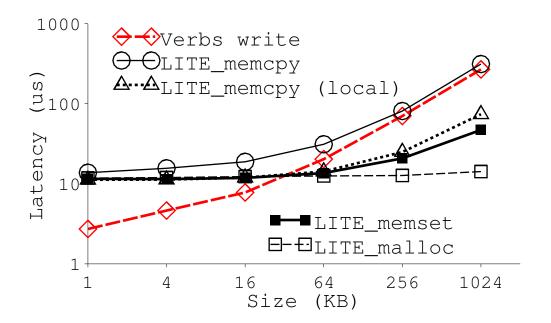

| 3.17 | LITE Memory Operations Latency                           | 49  |

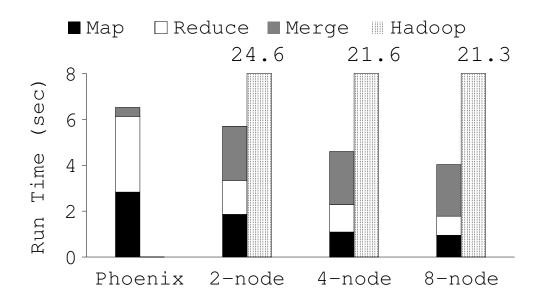

| 3.18 | MapReduce Performance.                                   | 53  |

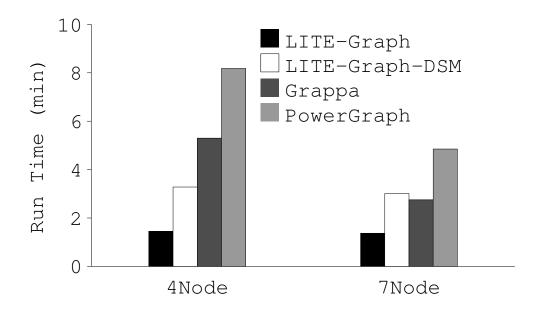

| 3.19 | PageRank Performance.                                    | 54  |

| 4.1  | PM Organization Comparison                               | 62  |

| 4.2  | Read/Write Protocols of DPM Systems                      | 70  |

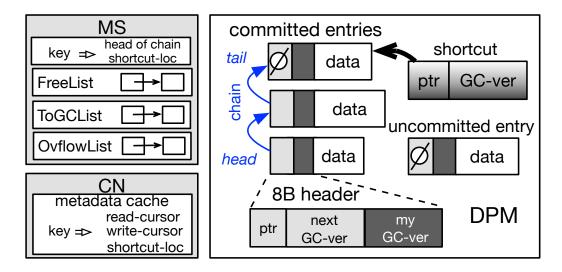

| 4.3  | SepDS System Design.                                     | 74  |

| Figu | Pa Pa                                     | ge |

|------|-------------------------------------------|----|

| 4.4  | Replicated Data Entity.                   | 80 |

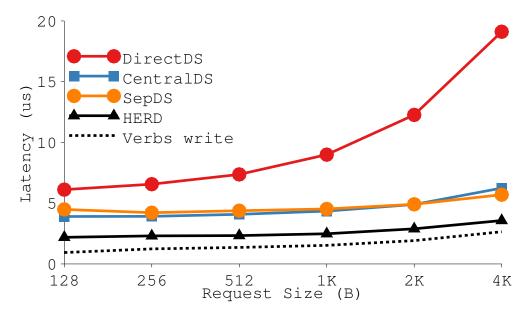

| 4.5  | Write Latency                             | 84 |

| 4.6  | Read Latency                              | 85 |

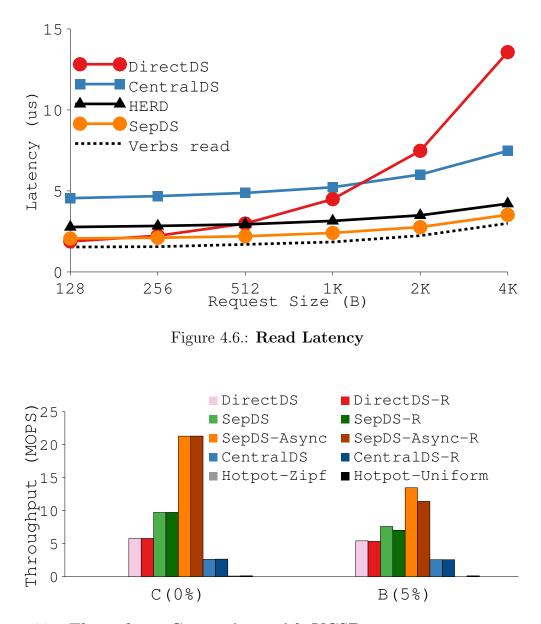

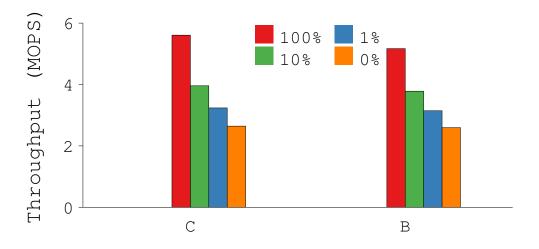

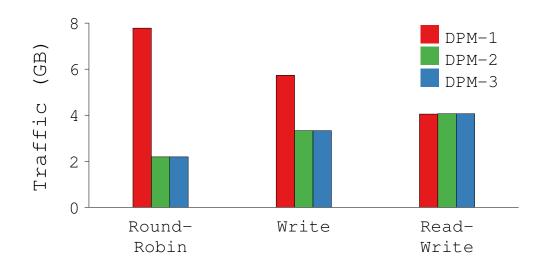

| 4.7  | Throughput Comparison with YCSB           | 85 |

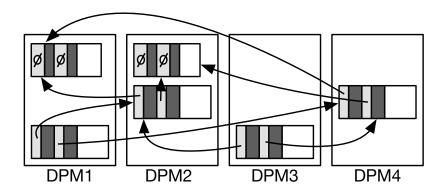

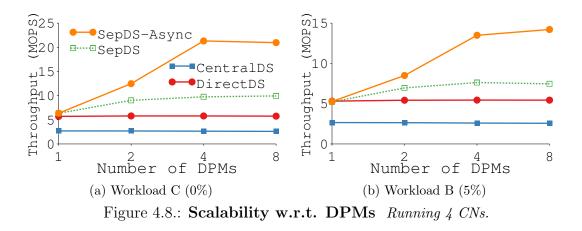

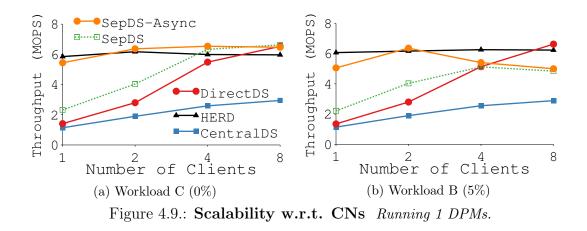

| 4.8  | Scalability w.r.t. DPMs                   | 87 |

| 4.9  | Scalability w.r.t. CNs                    | 87 |

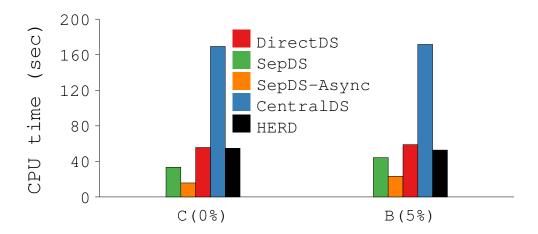

| 4.10 | CPU Utilization                           | 90 |

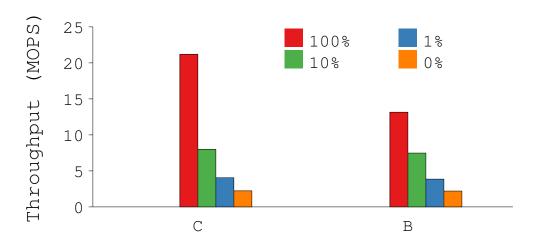

| 4.11 | Effect of Metadata Cache in SepDS         | 90 |

| 4.12 | Effect of Data Cache in CentralDS         | 91 |

| 4.13 | Load Balancing in SepDS                   | 91 |

| 5.1  | MR Key Value                              | 99 |

| 5.2  | Attack Environment and RNIC Architecture  | 03 |

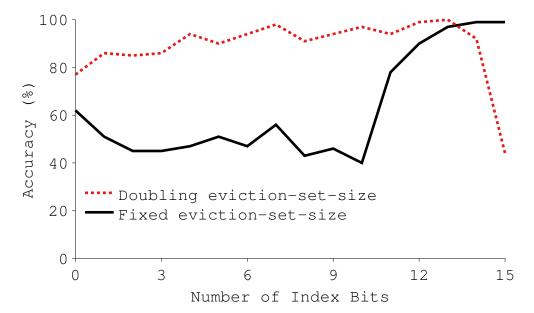

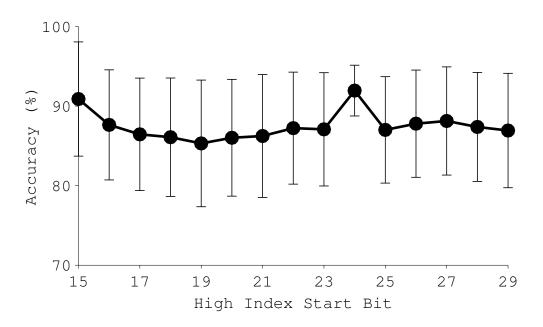

| 5.3  | Effect of Number of Index Bits            | 10 |

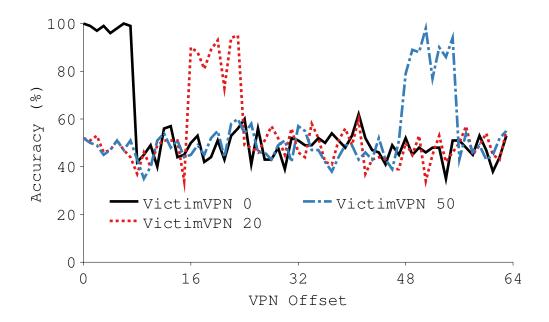

| 5.4  | Effect of Eviction Set Offset             | 11 |

| 5.5  | Effect of Secondary Index                 | 12 |

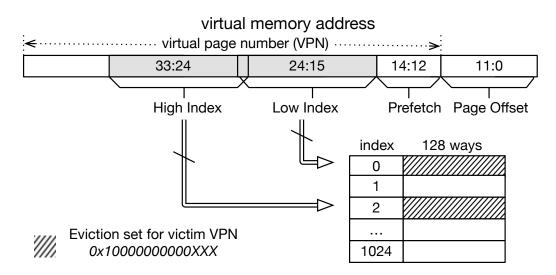

| 5.6  | Reverse-Engineered PTE Cache Organization | 15 |

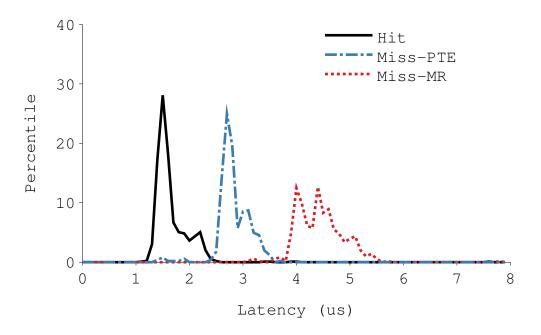

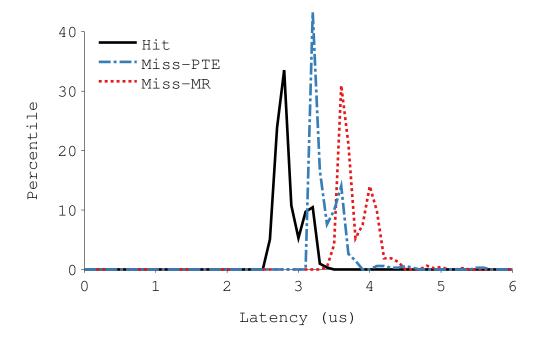

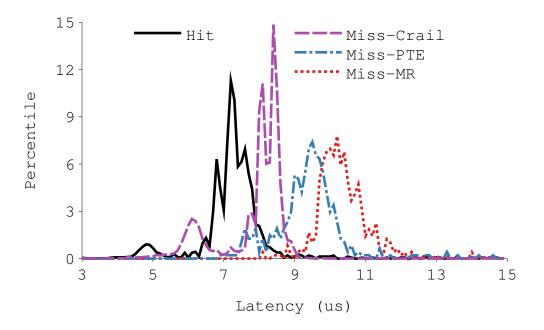

| 5.7  | Timing Differences                        | 17 |

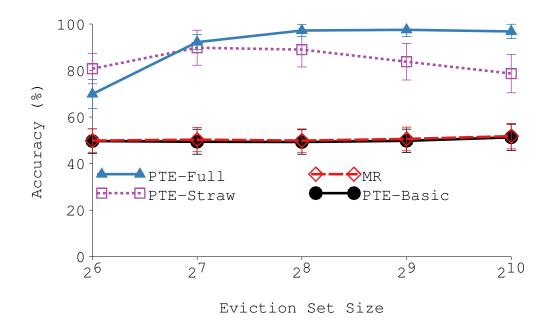

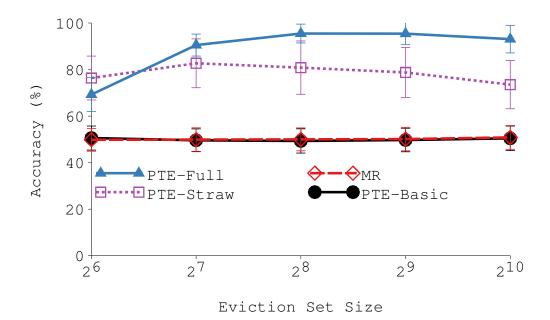

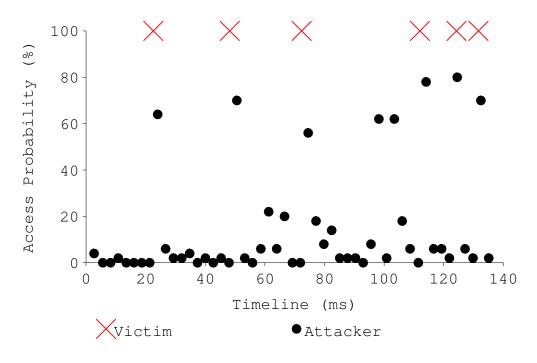

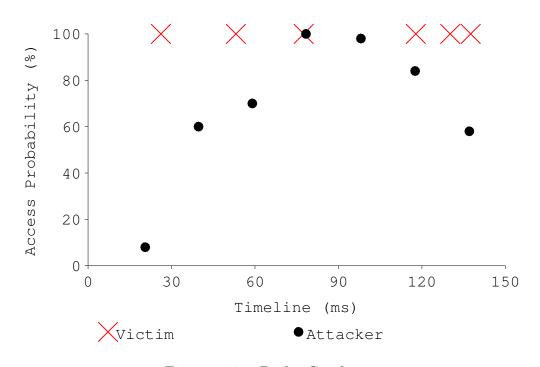

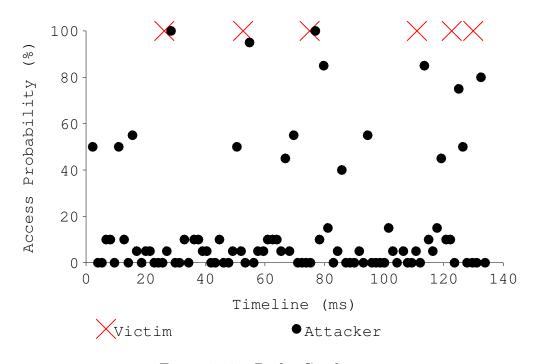

| 5.8  | Accuracy of Attacks                       | 18 |

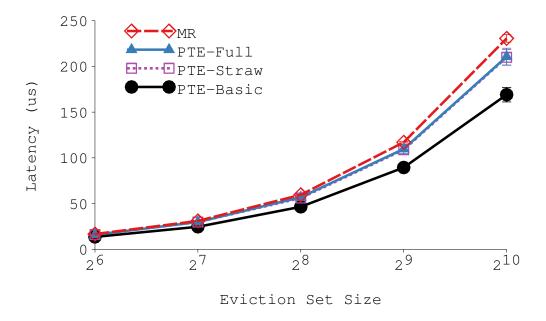

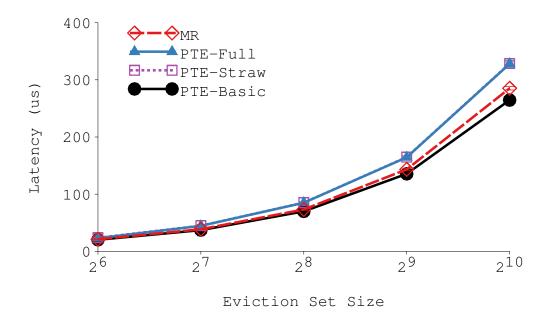

| 5.9  | Latency of Attacks                        | 19 |

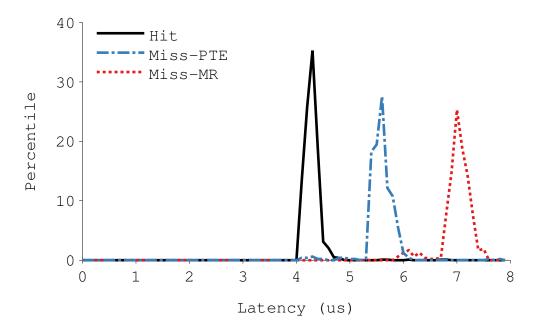

| 5.10 | Timing Differences in ConnectX-5          | 20 |

| 5.11 | Accuracy of Attacks in ConnectX-5         | 21 |

| 5.12 | Timing Differences in ConnectX-3          | 22 |

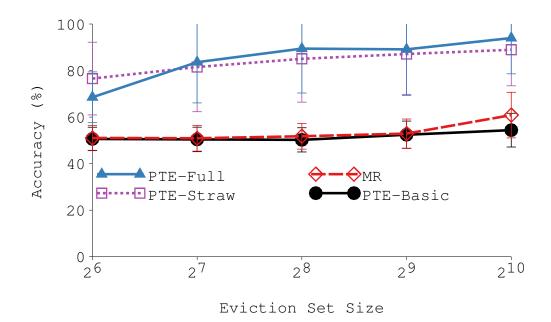

| 5.13 | Timing Differences in CloudLab            | 23 |

| 5.14 | Accuracy of Attacks in CloudLab           | 24 |

| 5.15 | Latency of Attacks in CloudLab            | 25 |

| 5.16 | $PythiaCrail_{MR}$                        | 27 |

| 5.17 | $PythiaCrail_{PTE}$                       | 28 |

| 5.18 | $PythiaCrail_{Client}$                    | 29 |

| Figure                                  | Page |

|-----------------------------------------|------|

| 5.19 Timing Difference in Crail         | 130  |

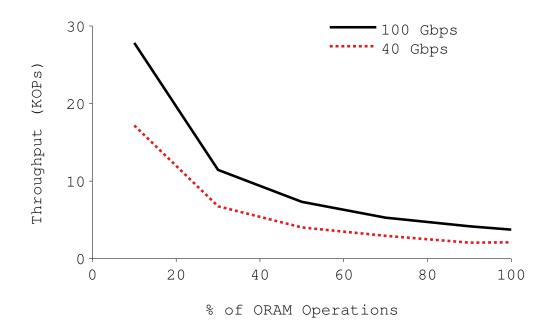

| 5.20 Read Performance of One-Sided ORAM | 137  |

#### ABSTRACT

Tsai, Shin-Yeh Ph.D., Purdue University, August 2019. Building Fast, Scalable, Low-Cost, and Safe RDMA Systems in Datacenters. Major Professor: Yiying Zhang.

Remote Direct Memory Access, or RDMA, is a technology that allows one computer server to direct access the memory of another server without involving its CPU. Compared with traditional network technologies, RDMA offers several benefits including low latency, high throughput, and low CPU utilization. These features are especially attractive to datacenters, and because of this, datacenters have started to adopt RDMA in production scale in recent years.

However, RDMA was designed for confined, single-tenant, High-Performance-Computing (HPC) environments. Many of its design choices do not fit datacenters well, and it cannot be readily used by datacenter applications. To use RDMA, current datacenter applications have to build customized software stacks and fine-tune their performance. In addition, RDMA offers limited scalability and does not have good support for resource sharing or protection across different applications.

This dissertation sets out to seek solutions that can solve issues of RDMA in a systematic way and makes it more suitable for a wide range of datacenter applications.

Our first task is to make RDMA more scalable, easier to use, and have better support for safe resource sharing in datacenters. For this purpose, we propose to add an *indirection layer* on top of native RDMA to virtualize its low-level abstraction into a high-level one. This indirection layer safely manages RDMA resources for different datacenter applications and also provide a means for better scalability.

After making RDMA more suitable for datacenter environments, our next task is to build applications that can exploit all the benefits from (our improved) RDMA. We designed a set of systems that store data in remote persistent memory and let client machines access these data through pure one-sided RDMA communication. These systems lower monetary and energy cost compared to traditional datacenter data stores (because no processor is needed at remote persistent memory), while achieving good performance and reliability.

Our final task focuses on a completely different and so far largely overlooked one — security implications of RDMA. We discovered several key vulnerabilities in the one-sided communication pattern and in RDMA hardware. We exploited one of them to create a novel set of remote side-channel attacks, which we are able to launch on a widely used RDMA system with real RDMA hardware.

This dissertation is one of the initial efforts in making RDMA more suitable for datacenter environments from scalability, usability, cost, and security aspects. We hope that the systems we built as well as the lessons we learned can be helpful to future networking and systems researchers and practitioners.

#### 1 INTRODUCTION

Remote Direct Memory Access, or RDMA, is a technology that lets a computer server directly access the memory of another server without involving the CPU of this other server. Apart from this access pattern (commonly called *one-sided communication*), RDMA also allows applications to issue requests directly from the user space to the NIC, bypassing the OS kernel, and in doing so RDMA avoids any memory copying. With one-sided communication, kernel bypassing, and memory zero copy, the RDMA technology enables network communication with high throughput, low latency, and low CPU utilization.

The RDMA technology was originally designed for the high-performance computing (HPC) environments and has been widely adopted in these environments over the past two decades. In recent years, there has been a dramatically increasing interest in adopting RDMA in datacenters. Major cloud vendors like Microsoft Azure [1] and Alibaba Cloud [2] have all deployed RDMA in production scale. RDMA is especially attractive in datacenter environments for three reasons.

First, datacenter applications are becoming more distributed [3–8] and disaggregated [9–16]. Network communication is a key factor in almost all modern datacenter applications' performance. While most of today's datacenters run on 40 Gbps Ethernet-based network with ~100  $\mu s$  round-trip time (RTT) [17, 18], the latest RDMA technology can reach 200 Gbps throughput and sub-0.6  $\mu s$  RTT [19], thanks to its kernel bypassing and memory zero-copy features. Both throughput-oriented and latency-bound datacenter applications can benefit from the network performance improvements offered by RDMA.

Second, big data gives rise to a host of applications that access large amounts of (in-memory) data during their computation: data analytics, graph computation, deep learning, and in-memory databases, to name just a few. Their memory capacity needs often exceed what a single machine can offer in today's datacenters [20–25]. For example, computation on a big social-network graph can take more than 5 TB memory [22]. Unfortunately, memory in a single computer is facing a capacity wall and a bandwidth wall, and it's hard to meet the requirements of many memory-hunger applications. At the same time, memory (and CPU) utilization across different machines is imbalanced, causing resource wastes in datacenters. Both these two problems can be solved by allowing applications to go beyond a single machine's memory and access *remote memory*, the key feature RDMA provides.

Third, certain tasks and applications in datacenters only need locations to store data without the need to perform any computation on them at these locations. For example, storage systems and databases in datacenters often keep multiple copies of data for better reliability and availability. With a primary-backup model, only a primary server performs application computation of data, and other servers (passively) receives copies of the data. RDMA's one-sided communication pattern benefits these datacenter systems by largely reducing the CPU utilization of the backup servers, which in turn saves energy consumption of the whole datacenter.

Despite of these promising usage cases of RDMA, moving RDMA into datacenters faces key challenges. RDMA was designed for HPC environments that are often single-purposed, single-tenant, and have small scales. RDMA in its native form (*i.e.*, unmodified RDMA hardware, driver, and default libraries) is not a good fit for the more general-purpose, multi-tenant, and large-scale datacenter environments.

Native RDMA is hard to use and inflexible; it does not scale well; it only offers limited options in sharing resources, performance isolation, and resource protection; and it has various security vulnerabilities. Because of these issues, datacenter applications cannot and should not use RDMA as is. A common practice currently is to build customized RDMA-based software stacks for each datacenter application and fine-tune its performance [26–38].

This dissertation aims to make RDMA more suitable for datacenter applications in a systematic way. We revisited many design decisions in native RDMA and built a generic layer on top of native RDMA to make it more scalable and easier to use, with better support for resource sharing, performance isolation, and resource protection. We further built a set of remote-memory systems on top of this improved RDMA abstraction and ported several applications to it. Finally, we explored security vulnerabilities in both hardware that implements RDMA and the more generic one-sided communication pattern.

This dissertation significantly advances state of the art in RDMA software, transforming RDMA from a technology designed for restricted, HPC environments to one that is readily useful for a wide range of datacenter applications, all without changing any of RDMA-based hardware or the RDMA network protocol. Below, we give a brief overview of the three main projects in this dissertation.

#### 1.1 Indirection Layer on RDMA for Better Datacenter Support

For RDMA to be successful in datacenters, it first needs to be scalable, easy-touse, and safe to share across different applications. The first part of this dissertation focuses on improving the usability and scalability of RDMA for datacenter environments.

The design of native RDMA offloads the whole network stack and complex metadata to NIC hardware. While this approach minimizes software overhead, it inevitably limits the flexibility of RDMA and makes RDMA NICs the scalability bottleneck.

We propose to add a software indirection layer on top of RDMA hardware to *virtu-alize* the low-level, inflexible native RDMA abstraction into a flexible and easy-to-use one that can better support datacenter applications. We build such an indirection layer in the kernel space, which manages and safely shares RDMA resources across applications. This system not only makes RDMA a better fit for datacenter applications but also preserves most of native RDMA's superior performance and significantly improve its scalability.

#### 1.2 RDMA-Based Data Store with Remote Persistent Memory

The indirection layer we built (as the first part of this dissertation) makes RDMA more flexible, scalable, easy-to-use, and suit datacenter environments better. The next question we seek to answer is *how to build applications on top of the (improved) RDMA stack*.

Our major efforts here is on building distributed RDMA-based data stores, an important class of systems that datacenter applications leverage for storing and accessing their data. Our focus here is to not only seek solutions that have good performance and scalability, but also ones that have low monetary and energy cost and can sustain system crashes.

To achieve these goals, we push the one-sided communication idea to an extreme by proposing to completely remove the CPU at where data is stored, making these data accessible only from one-sided RDMA. We further propose to store these data in *persistent memory*, which are denser than DRAM and can sustain power loss. With these ideas, we designed a set of novel RDMA-based data store systems with remote persistent memory. These systems offer great performance, low cost, reliability, and high availability.

#### 1.3 Security Implications of One-Sided Communication and RDMA

The first two parts of this dissertation and most of existing RDMA research and production systems focus on the performance, scalability, and programmability of RDMA, leaving one important aspect yet to be explored — security. The third part of this dissertation explores various security implications of RDMA systems and onesided communication in datacenter and cloud settings.

Among these security implications, the most notable one is vulnerabilities related to RDMA's hardware design. RDMA NICs caches various metadata in a limited-size on-NIC SRAM. We discovered new timing side channels that exploit this mechanism of RDMA NICs and built real side-channel attacks on a widely used RDMA data store system with three generations of RDMA NICs. With these attacks, an attacker can steal the access information of a victim without accessing either the victim's machine or the machine that stores the data. As the first work to explore vulnerabilities in RDMA hardware, we raise awareness of the security aspects of RDMA and provide several promising directions of mitigation techniques.

#### 1.4 Chapter Overview

The rest of this dissertation is organized as follows.

- **Background:** Chapter 2 provides a background on one-sided communication, RDMA architecture and applications, persistent memory, and side-channel attacks.

- Indirection Layer on RDMA for Better Datacenter Support: Chapter 3 presents LITE, the indirection layer we built in the Linux kernel which virtualizes native RDMA into a flexible, high-level, easy-to-use abstraction and allows applications to safely share resources.

- **RDMA-Based Data Store with Remote Persistent Memory:** Chapter 4 describes DPM, a set of systems that treat remote persistent memory as "dumb" (*i.e.*, with no processing power) and access these remote persistent memory devices via one-sided communication.

- Security Implications of One-Sided Communication and RDMA: Chapter 5 discusses various security implication of RDMA and the one-sided communication pattern. The focus of this chapter is a set of RDMA-based remote side-channel attacks. We also discuss potential mitigation techniques and the opportunities of leveraging RDMA to enhance security.

- **Related Work:** Chapter 6 briefly introduces other research efforts in datacenter RDMA systems and applications. We also present related research work in persistent memory data store systems and remote side-channel attacks.

• **Conclusion:** Chapter 7 concludes this dissertation with a summary of all the chapters and the lessons we have learned.

#### 2 BACKGROUND

This chapter provides the background of various aspects of this dissertation. We first provide an overview of RDMA and its current usages in datacenters ( $\S2.1$ ), then introduce various distributed in-memory data store systems in datacenters ( $\S2.2$ ), and finally discusses side-channel attacks and its countermeasures ( $\S2.3$ ).

#### 2.1 Remote Direct Memory Access

This section provides a background of RDMA. We first give an overview of the RDMA technology and introduce the abstraction of native RDMA. We then discuss RDMA NICs where most RDMA functionalities are implemented and provide our performance benchmark results of four different RDMA NICs. Finally, we describe RDMA-based applications in datacenter and the deployment of RDMA in datacenter.

#### 2.1.1 Architecture and Abstraction

Remote Direct Memory Access, or *RDMA*, is a network technology designed to offer low-latency, high-throughput, and low-CPU-utilization network communication. Its main idea is to allow one machine to directly access the memory of another machine without involving the CPU of this other machine, a communication pattern called *one-sided communication*. RDMA offers superior performance compared with traditional network technologies because of three main technologies. First, one-sided RDMA requests bypass the CPU of the receiver. Second, applications issue RDMA requests directly from user space, bypassing kernel and avoiding kernel trap cost on the data path. Third, RDMA avoids memory copying when performing network communication (a technique called *zero-copy*). There are three implementations of RDMA: InfiniBand (IB) [39, 40], Internet Wide Area RDMA Protocol (iWARP) [41], and RDMA over Converged Ethernet (RoCE) [42,43]. All implementations follow the standard RDMA protocol [44]. IB is a switched network that is specifically designed for RDMA. iWARP and RoCE are two Ethernet-based technologies. iWARP is defined based on four IETF-standards and it relies on congestion-aware protocols such as TCP and STCP to deliver reliable RDMA services. iWARP typically requires implementing the whole TCP network stack in RDMA NICs, because the kernel implementation of the TCP network stack is a performance bottleneck in a high-speed network. RoCE implements the RDMA protocol over standard Ethernet (RoCEv1) and UDP (RoCEv2), and is the preferred technology in existing datacenters [18]. Because of its performance and cost benefits [18, 45, 46], RDMA has been deployed in large scale in datacenters like Microsoft Azure [1] and Alibaba Cloud [2].

To find out the owning cost of RDMA networks in datacenters, we study the market prices of RDMA NICs and RDMA switches. We use RoCE as an example since most of the datacenter networks already adopt Ethernet-based network, and RoCE offers better performance than iWARP [46,47]. Lots of the existing commodity Ethernet switches [48–50] already support Priority Flow Control (PFC) which enables lossless Ethernet for RoCE. Thus, it does not need to replace existing Ethernet switches to adopt RoCE network. On the other hand, RoCE NICs are price competitive to regular Ethernet NICs [51,52] especially in 40 Gbps — the most popular network bandwidth in datacenters [18]. Therefore, in datacenters, the owning cost of RoCE network is similar to the owning cost of existing Ethernet-based network because the price of RoCE NICs is similar to the price of regular Ethernet NICs and datacenters do not need to purchase a set of new Ethernet switches.

The standard interface of native RDMA is a set of operations collectively called *Verbs*. Native RDMA allows accesses from both user space and kernel space using Verbs. *libibverbs* is an open-source low-level library which defines a set of required APIs. Developers build RDMA-based applications through Verbs and libibverbs, and

both Verbs and libibverbs can support different RDMA implementations (*e.g.*, RoCE, iWARP, and RDMA) which facilitates the development of RDMA-based applications.

RDMA supports both one-sided and two-sided communication. One-sided RDMA operations directly access memory at a remote node without involving the remote node's CPU, similar to DMA on a single machine. Two-sided RDMA operations inform the remote node of a delivered message and involve both sender and receiver processing either through signaling or polling, similar to send/recv in traditional network messaging.

RDMA communication is implemented using various types of *queues* including send, receive, and completion queues, and applications use these queues to post requests and to learn when a request has completed or been received.

To perform a one-sided RDMA operation, an application process at a receiver node needs to first allocate a consecutive virtual memory space and then use the virtual memory address range to register a *memory region*, or *MR*, with the RDMA NICs. An application can register multiple MRs over the same or different memory spaces. The RDMA NIC will assign a pair of local and remote protection keys (called *lkey*) and rkey) to each MR. This application then conveys the virtual address of the MR and its *rkey* to processes running on other nodes. After building connections between these other nodes (senders) and the node that the MR-registering application runs on (receiver), these processes can use 1) a virtual memory address that falls in the MR's virtual memory address range, 2) a size, and 3) the rkey of the MR to perform one-sided RDMA read and write. In RDMA's term, a connection is called a Queue *Pair*, or *QP*. The local host also needs to register a local MR for the read/write buffer and can then perform RDMA operations by posting requests on a send queue (SQ). The RDMA read/write operation returns as soon as the request is sent to RDMA NIC. Applications have to separately poll a send completion queue (CQ) to know when the remote data has been read or written.

To perform a two-sided RDMA operation, the remote host needs to pre-post receive buffers to a receive queue (RQ) before the local host can send a message. The remote host polls the receive CQ to identify a received message coming.

RDMA supports reliable and unreliable connections (RC and UC) and unreliable datagram (UD). UD mode has the best scalability because UD mode supports the communication between one UD QP to multiple UD QPs, but UD mode only supports send/recv operations. UC mode supports send/recv and write operations, but the connection semantic limits the scalability to the communication between one UC QP to one UC QP. RC mode supports all RDMA operations including send/recv, read/write, and atomic operations, and RC mode has the same scalability as UC mode although RC mode has more processing overhead on RDMA NICs [33].

#### 2.1.2 RDMA NICs

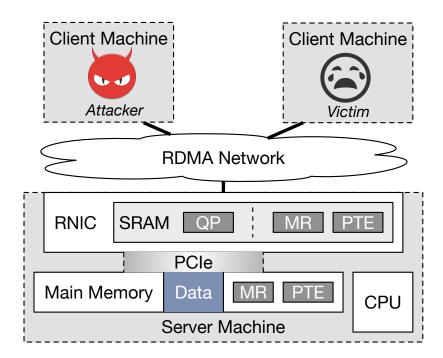

RDMA NICs, or *RNIC*s, are where most RDMA functionalities are implemented. They usually contain complex hardware logic that implements the RDMA protocol and some SRAM to store metadata, and they are often connected to the host's PCIe bus (allowing RNICs access to main memory through DMA). Because of the need to bypass the kernel and receiver's CPU, most RDMA functionalities and data structures have to be offloaded to the RNIC hardware.

An RNIC's on-board SRAM stores three types of metadata. First, it stores metadata for each QP in its memory. Second, it stores *lkeys*, *rkeys*, and virtual memory addresses for all registered MRs. Third, it caches page table entries (PTEs) for MRs to obtain the DMA address of an RDMA request from its virtual memory address. RNICs have a limited amount of on-board SRAM which can only hold metadata for hot data. When the SRAM is full, an RNIC will evict its cached metadata to the main memory on the host machine, and on a future access, fetch the evicted metadata from the host main memory back through the PCIe bus. The SRAM architecture is

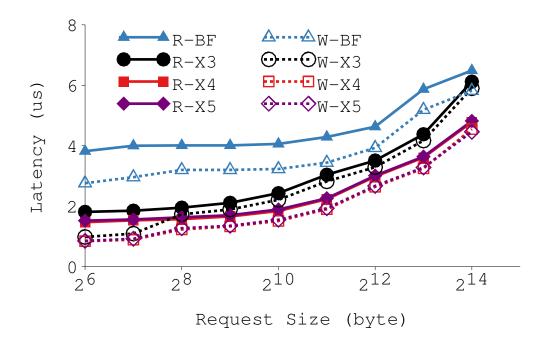

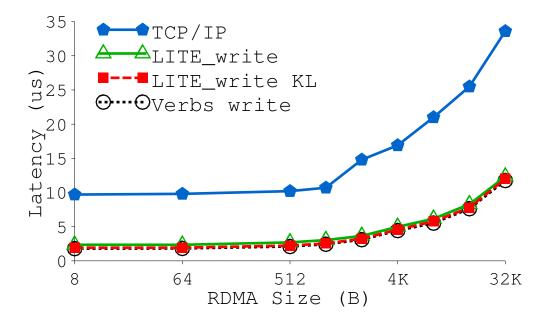

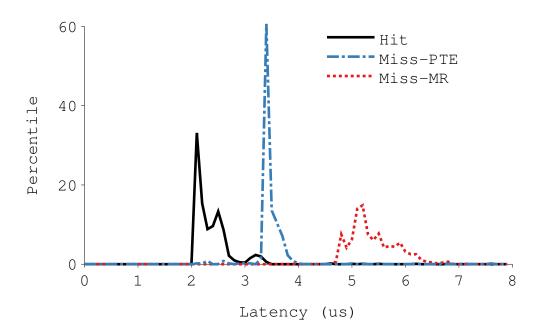

Figure 2.1.: Latency of RDMA Requests. *R- and W- represent READ and WRITE request respectively. X3, X4, and X5 represent ConnectX series RNICs, and BF represents BlueField. All of them are connected with a 100 Gbps InfiniBand switch.*

vendor-specific and not disclosed or specified in the RDMA standard. We benchmark the performance of the state-of-the-art RNICs in Section 2.1.3.

#### 2.1.3 RDMA Microbenchmarks

To better understand the performance of RDMA and to provide a baseline for evaluations in this dissertation, we show the microbenchmarks of the native RDMA among four different Mellanox RNICs: ConnectX-3 (40 Gbps) [53], ConnectX-4 (100 Gbps) [54], ConnectX-5 (100 Gbps) [55], and BlueField (100 Gbps) [56]. We connect all the RNICs with a 100 Gbps InfiniBand switch. ConnectX-3, ConnectX-4, and ConnectX-5 are ASIC-based NICs, and BlueField is a SoC-based SmartNIC which has on-board programmable processors. SmartNICs are more expensive than ASIC-based NICs, but SmartNICs can accelerate several applications (*e.g.*, encryption, decryption, firewall, etc) and reduce host CPU utilization.

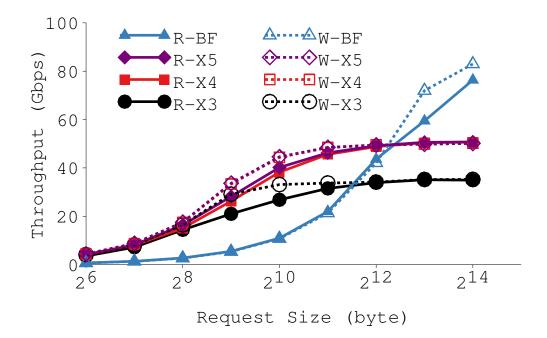

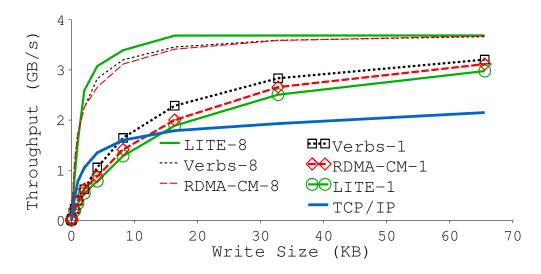

Figure 2.2.: Throughput of RDMA Requests. *R- and W- represent READ and WRITE request respectively. X3, X4, and X5 represent ConnectX series RNICs, and BF represents BlueField. All of them are connected with a 100 Gbps InfiniBand switch.*

We use OpenFabrics *perftest* software to measure the latency and the throughput of the above four RNICs. Limited by the type of machines we have in our lab cluster, all RNICs can only connect to these machines via a PCIe  $3.0 \times 8$  bus. However, ConnectX-4 and ConnectX-5 require at least PCIe  $3.0 \times 16$  bus to sustain the 100 Gbps bandwidth. Therefore, the throughput of these two RNICs are capped by the PCIe bandwidth of the host machines. For BlueField, we use the on-board SoCs to issue and process the requests. Thus, the RDMA requests access on-board memory through on-board PCIe  $4.0 \times 16$  bus without being capped by the PCIe bandwidth of the host

Figure 2.1 shows the latency of RDMA requests as request size increases. For all different RNICs, read request has higher latency than write request because of the implementation of RDMA transmission protocol [33]. ConnectX-4 and ConnectX-5 are the new generation RNICs which outperform ConnectX-3 in latency especially

when the request size is big. Although BlueField uses the same chip as ConnectX-5, BlueField has a higher latency because the processing speed of BlueField is slower than the regular ASIC-based RNICs.

Figure 2.2 takes a closer look at the throughput of RNICs against request size. BlueField has the highest throughput because BlueField supports the highest maximum bandwidth and the on-board PCIe bandwidth can sustain the bandwidth. Although ConnectX-4 and ConnectX-5 have the same maximum bandwidth as Blue-Field, the throughput of ConnectX-4 and ConnectX-5 is capped by the PCIe bandwidth of the host machines. ConnectX-3 has the lowest throughput because the maximum bandwidth of ConnectX-3 is only 40 Gbps. Read and Write requests have similar throughput. When the request size is small (*e.g.*, smaller than 4096), the throughput of BlueField is lower than ConnectX-4 and ConnectX-5 because of the limited processing speed of BlueField. When the request size increases, BlueField has the highest throughput because the bandwidth is not capped by the on-board PCIe bandwidth, but the throughputs of ConnectX-4 and ConnectX-5 are capped by the attached PCIe 3.0  $\times$ 8 bus. There is no significant difference between read and write request in the throughput test because the parallel processing within the throughput benchmark amortizes the difference between two protocols.

#### 2.1.4 RDMA in Datacenter Applications

The past two decades have seen a growing usage of RDMA in HPC environments [57–59]. In recent years, there is an emerging trend in using RDMA in datacenter environments from both industry and academia [60–63]. Recent RDMA-based applications include in-memory key-value stores [29–35,64–66], in-memory databases and transactional systems [26,67,68], graph processing systems [28,69], distributed machine learning systems [70], consensus implementations [71,72], distributed nonvolatile memory systems [36,37,73], and remote swap systems [63,74]. Most of these applications use both one-sided and two-sided RDMA operations, with some being pure one-sided [26,27].

We believe that the use of RDMA in datacenters will continue increasing in the future because of application needs support from hardware and network. Many modern datacenter applications demand fast access to a vast amount of data, most conveniently and efficiently as in-memory data. With memory on a single machine facing its wall [75], these applications can largely benefit from fast, direct access to remote memory [25, 63, 76]. At the same time, more hardware in datacenters is adding the support for direct RDMA accesses, such as NVMe over Fabrics [77, 78] and GPU Direct [79–82]. Thus, there will be both high demand and more support for the low-latency, RDMA-equipped technologies in datacenters, and we believe that the trend of using RDMA to build datacenter systems will only increase in incoming years.

#### 2.2 Datacenter In-Memory Data Stores

This section presents background on different types of data stores including inmemory data stores, in-PM data stores, and RDMA data stores in the datacenter settings.

#### 2.2.1 Distributed and Remote DRAM-Based Data Stores

Existing in-memory data store systems can be categorized into two types of models. The first model is *distributed memory*, which combines the memory of nodes in a cluster into a virtual memory pool [25, 37, 83–89]. Processes running on any node in the cluster can allocate and access memory in this global pool. However, usage of these distributed memory systems has been limited, mainly because their high network and software overheads are not acceptable for most memory-based applications. Distributed memory/PM allows a process to use memory larger than local main memory and greatly improves resource utilization. However, it requires a significant amount of CPU time on each machine to participate in a distributed data access protocol.

The second model is a *remote memory* model which separates servers in a cluster into two groups, compute nodes and memory nodes [26,27,90–92]. Data is stored and managed at the memory nodes and compute nodes issue network requests to fetch or store data at memory nodes. This model requires CPUs at memory nodes to process memory requests and perform various metadata and control tasks. Every memory has a local CPU which performs memory management.

#### 2.2.2 Distributed Persistent Memory Data Stores

Non-volatile memory technologies such as 3DXpoint [93], phase change memory (PCM), spin-transfer torque magnetic memories (STTMs), and the memristor provide byte addressability, persistence, and latency that is within an order of magnitude of DRAM [94–101]. In addition, NVM consumes significantly lower energy compared to DRAM [102–104]. NVMs can attach directly to the main memory bus and we call such DIMM-based NVMs Persistent Memory or PM in this dissertation. PM has attracted extensive research efforts in the past decade, most of which were designed for single-node environments [29, 105–113].

Recently, because of the need to deploy PM in datacenter environments [114], new research interests arise in the distributed PM area [36, 37, 73, 115]. Mojim [36] uses asynchronous primary-backup replication to provide reliability and availability to PM. Hotpot [37] and Octopus [73] have all taken a model where each node in a cluster includes some amount of PM used to store data that can be accessed both locally and by other nodes. This distributed PM model not only increases CPU utilization but also makes PM deployment hard. To deploy PM in datacenters, one has to find empty DIMM slots in existing servers there or purchase new servers to host PM. In addition to the general discussion of RDMA applications in Section 2.1, this section focuses on RDMA data stores specifically. Recently, with the increasing popularity of low-latency RDMA networks in datacenters [29, 33, 116], several recent in-memory data stores such as key-value stores [29–31, 34, 35, 64, 65], in-memory databases and transactional systems [26, 27, 67, 68], and remote swap systems [63, 74] use RDMA to perform their network communication. Most of them use one-sided RDMA for reads and two-sided RDMA for writes. To achieve low-latency performance, they usually use busy-polling threads to receive incoming two-sided RDMA requests. Wei *et al.* summarize the design tradeoffs of one-sided vs. two-sided RDMA for transaction systems [68].

Existing RDMA-based distributed data stores perform management tasks such as memory allocation, garbage collection, and load balancing at CPUs in data-hosting nodes [26, 29]. Consequently, even when one-sided RDMA operations help reduce CPU utilization, practical RDMA-based data stores still require a CPU and a significant amount of energy at each data-hosting machine. For example, FaRM [29], an RDMA-based distributed memory system that tries to use as much one-sided communication as possible, still requires processing power to perform metadata operations and certain steps in its write replication protocol.

#### 2.3 Side-Channel Attacks

Traditional computer security attacks target the weakness in a computer system itself. In contrast, side-channel attacks exploit information leakages in aspects beyond the targeted system itself (thus the name "side channel"). Such side channels include power usage, electromagnetic emissions, timing difference, and acoustic emissions [117, 118].

In recent years, a host of attacks that exploit various hardware features to establish side channels have been proposed. CPU-cache-based side-channel attacks such as PRIME+PROBE [119–127], EVICT+RELOAD [128], FLUSH+RELOAD [129], and FLUSH+FLUSH [127, 128] can leak victim's memory access patterns at fine granularity. CPU-cache-based side channels are also the key enabling factors in attacks like Meltdown [130], Spectre [131], and Foreshadow [132]. Other than CPU caches, TLB [133] or port contention [134] also expose hardware-based side channels.

Side-channel attacks raised key concerns in cloud environments where one tenant can steal information from other tenants when they share the same physical resource [122, 135–137] or the same service [138]. Most notable and impactful sidechannel related attacks are Spectre [131] and Meltdown [130], which exploit vulnerabilities in most modern processors to steal data that attackers otherwise do not have access to. They resulted in patching Linux machines running in almost all major datacenters and causing application performance slowdown of as high as 30% [139].

There are two major ways to mitigate side-channel attacks in system design. The first way is to hide leaked information (*e.g.*, re-implement critical components or change cryptographic primitives). The second way is to remove the correlation between each execution cycle (*e.g.*, randomization or introducing noise). System developers frequently use noise, randomization, and resource isolation to hide information and eliminate the correlation [118, 129, 140, 141]. However, these countermeasures mostly come with latency and throughput overhead, which is critical to datacenter applications. Datacenter environments share physical resources for better resource utilization, and this colocation makes datacenter applications even more vulnerable to side-channel attacks.

## 3 INDIRECTION LAYER ON RDMA FOR BETTER DATACENTER SUPPORT

RDMA was originally designed for HPC environments. Many design choices in RDMA suit a confined, single-purpose environment like HPC well, but native RDMA is not a good fit for the more general-purposed, heterogeneous, and large-scale datacenter environments because of the following three reasons.

First, there is a fundamental mismatch between the abstraction native RDMA provides and what datacenter applications desire. Datacenter applications usually build on high-level abstractions, but native RDMA provides a low-level abstraction that is close to hardware primitives. As a result, it is not easy for datacenter applications to use RDMA and even more difficult for them to exploit all the performance benefits of RDMA. Most RDMA-based datacenter applications require customized RDMA software stacks [29–33, 66], significant amounts of application adaptation [26–28], or changes in RDMA drivers [29, 66].

Second, RDMA manages and protects resources at the hardware level, and it lets user-level applications directly issue requests to RDMA NICs (called RNICs) bypassing kernel. This design causes at least three drawbacks for datacenter applications: lack of resource sharing, insufficient performance isolation, and inflexible protection.

The third issue of native RDMA is that the current architecture of RDMA cannot provide performance that scales with datacenter applications' memory usage. When bypassing kernel, RDMA inevitably adds burden to RNICs by moving privileged operations and metadata to hardware. For example, RNICs store protection keys and cache page table entries for user memory regions in its SRAM. It is essentially difficult for this architecture to meet datacenter applications' memory usage demand since the increase of on-RNIC memory capacity is slow and is cost- and energy-inefficient.

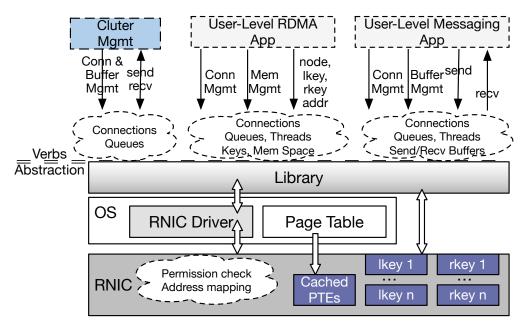

Figure 3.1.: Traditional RDMA Stack.

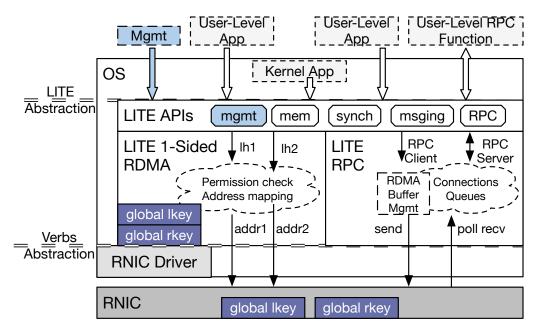

This chapter presents *LITE*, a *Local Indirection TiEr* in the kernel space to virtualize and manage RDMA for datacenter applications. LITE organizes memory as virtualized memory regions and supports a rich set of APIs including various memory operations, RPC, messaging, and synchronization primitives. Being in the kernel space, LITE safely manages privileged resources, provides flexible protection, and guarantees performance isolation across applications. Figures 3.1 and 3.2 illustrate the architecture of native RDMA and LITE.

Our approach of *onloading* [142] functionalities into kernel is the opposite to RDMA and many other networking systems' approach of offloading functionalities into hardware [143–145]. It is widely held that RDMA achieves its low-latency performance by directly accessing remote memory, bypassing kernel, and zero memory copy. We revisited these three techniques and found that with a good design, using a kernel-level indirection layer can preserve RDMA's performance benefits *and* avoid the drawbacks of native RDMA caused by kernel bypassing.

First, we add a level of indirection only at the local node and still ensure that onesided RDMA operations directly access remote memory. Second, we onload only the

Figure 3.2.: LITE Architecture.

management of privileged resources from hardware to kernel and leave the rest of the network stack at hardware. Doing so not only preserves native RDMA's performance but also solves the performance scalability issues caused by limited on-RNIC SRAM. Third, we avoid memory copy between user and kernel spaces by addressing user memory directly with physical addresses. Finally, we designed several optimization techniques to minimize system call overhead.

Internally, LITE consists of an RDMA stack and an RPC stack. The RDMA stack manages LITE's memory abstraction by performing its own address mapping and permission checking. With this level of indirection, we safely remove these two functionalities and the resulting scalability bottlenecks from RNICs without any modification on RNICs or drivers. LITE implements RPC with a new mechanism based on two-sided RDMA and it achieves flexibility, good performance, low CPU utilization, and efficient memory space usage at the same time. On top of these two stacks, we implement a set of extended higher-level functionalities and QoS mechanisms.

Our evaluation shows that compared to native RDMA and existing solutions that are customized to certain applications [32, 66], LITE delivers similar latency and throughput, while improving flexibility, performance scalability, CPU utilization, resource sharing, and quality of service.

We further demonstrate the ease-of-use, flexibility, and performance benefits of LITE by building four distributed applications on LITE: an atomic logging system, a MapReduce system, a graph engine, and a kernel-level Distributed Shared Memory (DSM) system. These systems are easy to build and perform well. For example, our implementation of graph engine has only 20 lines of LITE code, which encapsulate all the network communication functionalities. While using the same design as PowerGraph [6], this LITE-based graph engine outperforms PowerGraph by  $3.5 \times$  to  $5.6 \times$ . Our LITE-based MapReduce is ported from a single-node MapReduce implementation [146] with 49 lines of LITE code, and it outperforms Hadoop [4] by  $4.3 \times$  to  $5.3 \times$ .

In summary, we propose to build a new abstraction, LITE, which *virtualizes* the low-level, inflexible native RDMA abstraction into a flexible and easy-to-use one that can better support datacenter applications, and to build this virtualization layer in the kernel space to manage and safely share RDMA resources across applications.

Overall, LITE offers the following three key functionalities:

- Virtualizes RDMA with a generic kernel-level indirection layer for datacenter RDMA applications.

- Provides a set of mechanisms to minimize the performance overhead of kernellevel indirection and demonstrated the possibility of virtualizing RDMA while preserving (or even improving) its performance.

- Solves all the three issues of native RDMA for datacenter applications. Datacenter applications can easily use the abstraction layer to perform low-latency network communication and distributed operations.

#### 3.1 Issues of RDMA

This section introduces the limitations of using RDMA in datacenter applications. Many design choices of RDMA work well in a controlled, specialized environment like HPC. However, datacenter environments are different in that they need to support heterogeneous, large-scale, fast-evolving applications. There are several issues in using native RDMA for datacenter applications as we will introduce in Section 3.1.1, Section 3.1.2, and Section 3.1.3.

#### 3.1.1 Issue 1: Mismatch in Abstractions

A major reason why RDMA is not easy to use is the mismatch between its abstraction and what datacenter applications desire. Unlike the HPC environment where developers can carefully tune one or very few applications to dedicated hardware, datacenter application developers desire a high-level, easy-to-use, flexible abstraction for network communication so that they can focus on application-specific development. Originally designed for the HPC environment, native RDMA uses a low-level abstraction that is close to hardware primitives and is difficult to use [32]. Applications have to explicitly manage various types of resources and go through several non-intuitive steps to perform an RDMA operation, as explained in Section 2.1. It is even more difficult to optimize RDMA performance. Users need to properly choose from different RDMA operation options and tune various configurations, sometimes even to adopt low-level optimization techniques [29, 32, 66].

An API wrapper on top of the native RDMA interface such as Rsocket [147] can translate certain RDMA APIs into high-level ones. However, such a simple wrapper is far from enough for datacenter applications. For example, RDMA memory regions are created and accessed using virtual memory addresses in application process address spaces. The use of virtual memory addresses requires RNICs to store page table entries (PTEs) for address mapping (Section 3.1.2), makes it hard to share resources across processes (Section 3.1.3), and does not sustain process crashes. API wrappers cannot solve any of these issues since they do not change the way RNICs use virtual memory addresses.

## 3.1.2 Issue 2: Unscalable Performance

When bypassing kernel, privileged operations and data structures are offloaded to the hardware RNIC. With limited on-RNIC SRAM, it is fundamentally hard for RDMA performance to scale with respect to three factors: the amount of MRs, the total size of MRs, and the total number of QPs.

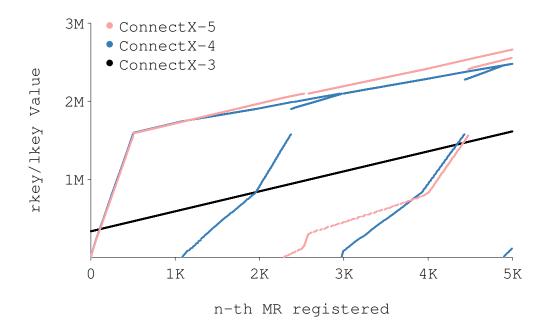

First, RNICs store *lkeys*, *rkeys*, and virtual memory addresses for all registered MRs. As the number of MRs increases, RNICs will soon (above 100 MRs in our experiments) face memory pressure (Figure 3.4). Since each MR is a consecutive virtual memory range and supports only one permission, not being able to use many MRs largely limits the flexibility of RDMA. For example, many key-value store systems use non-consecutive memory regions to store data. Memcached [90] performs on-demand memory allocation in 1 MB units and optimizes memory allocation using 64 MB pre-allocated memory blocks. It would require at least 1000 MRs for 64 GB data even with pre-allocation. Masstree [148] uses a separate memory region for each value and can take up to 140 million memory regions. These scenarios use MRs far more than what an RNIC can handle without losing performance. Using bigger MRs can reduce the total number of MRs, but requires substantial application changes and can cause memory space waste [149].

Second, RNIC caches PTEs for MRs to obtain the DMA address of an RDMA request from its virtual memory address. When there is a PTE miss in the RNIC, the RNIC will fetch the PTE from the host OS. When the total size of registered MRs exceeds what an RNIC can handle (above 4 MB in our experiments in Figure 3.5), thrashing will happen and degrade performance. Unfortunately, most datacenter applications use large amount of memory. For example, performing PageRank [150] on a 1.3 GB dataset using GraphX [151] and Spark [3] will need 12 GB and 16 GB memory

heaps respectively [63]. FaRM [29] uses 2 GB huge pages to mitigate the scalability issue of MR size. However, using huge pages will result in increased memory footprints, physical memory fragmentation, false memory sharing, and degraded NUMA performance [152–154].

Finally, RNIC stores metadata for each QP in its memory. RDMA performance drops when the number of QPs increases [29], largely limiting the total number of nodes that can be connected through RC in an RDMA cluster. FaSST [66] used UD to reduce the number of QPs. But UD is unreliable and does not support one-sided RDMA.

Datacenter applications often require the above three types of scalability. Even if a single application's scale is small, the combination of multiple applications will likely cause scalability issues. The speed of on-RNIC memory increase falls behind the increasing scalability of datacenter applications. Moreover, large on-RNIC memory is cost- and energy-inefficient [142]. We believe that offloading all priviledged functionalities and metadata to hardware is not and will not be a viable way to use RDMA for datacenter applications. Rather, the RDMA software and hardware stacks need to be restructured.

## 3.1.3 Issue 3: Lack of Resource Sharing, Isolation, and Protection

Native RDMA does not provide any mechanisms to safely share resources such as QPs, CQs, memory buffers, polling threads across different applications; it only provides a mechanism to share receive queues (called SRQ) within a process. Each application process has to build and manage its own set of resources.

The lack of resource sharing makes the performance scalability issue described above even worse. For example, each pair of processes on two nodes need to build at least one QP to perform RC operations. To perform polling for two-sided RDMA, each node needs at least one thread per process to busy poll separate receive CQs. Sharing resources within a process [29] improves scalability, but has limited scope. Without global management of resources, it is also hard to isolate performance and deliver quality of service (QoS) to different applications. For example, an application can simply register a huge amount of MRs to fill RNIC's internal memory and impact the performance of all other applications using the RNIC.

RDMA protects MR with *lkeys* and *rkeys*. However, such protection is not flexible. Each MR can only be registered with one permission, which is used by all applications to access the MR. To change the permission of an MR, it needs to be de-registered and registered again. Moreover, native RDMA relies on user applications to pass *rkeys* and memory addresses of MRs between nodes. Unencrypted *rkeys* and addresses can cause security vulnerability [155].

## 3.2 Virtualizing RDMA in Kernel: a Design Overview

"All problems in computer science can be solved by another level of indirection" — often attributed to Butler Lampson, who attributes it to David Wheeler

The issues of native RDMA outlined in the previous section, namely 1) no highlevel abstraction, 2) unscalable performance due to easily-overloaded on-RNIC memory, and 3) lack of resource management, are orthogonal to each other. However, they all point to the same solution: a virtualization and management layer for RDMA. Such a layer is crucial to make RDMA practical for datacenter applications. This section discusses why and how we add a kernel-level indirection, the challenges of adding such an indirection layer, and an overview of the design and architecture of LITE.

## 3.2.1 Kernel-Level Indirection

Many of RDMA's issues discussed in Section 3.1 have been explored decades ago, with different types of hardware resources. Hardware devices such as DRAM and disks expose low-level hardware primitives that are difficult and unsafe to use directly by applications. Virtual memory systems and file systems solve these issues by virtualize, protect, and manage these hardware resources in the kernel space. We believe that we can use the same classic wisdom of *indirection* and *virtualization* to make native RDMA ready for datacenter application usage.

We propose to virtualize RDMA using a level of indirection in the kernel space. An indirection layer can transform native RDMA's low-level abstraction into a high-level, easy-to-use abstraction for datacenter applications. A kernel-level indirection layer can safely manage all privileged resources. It can thus move metadata and operations from hardware to software. Doing so largely reduces the memory pressure of RNICs and improves the scalability of RDMA-based datacenter applications that is currently bottlenecked by on-RNIC SRAM size. Moreover, a kernel indirection layer can serve both kernel-level applications and user-level applications.

# 3.2.2 Challenges

Building an efficient, flexible kernel-level RDMA indirection layer for datacenter applications is not easy. There are at least three unique challenges.

The biggest challenge is how to preserve the performance benefits of RDMA while adding the indirection needed to support datacenter applications?

Next, how can we make LITE generic and flexible while delivering good performance? Both LITE's abstraction and its implementation need to support a wide range of datacenter applications. LITE also needs to let applications safely and efficiently share resources. Unlike previous works [29, 30, 32, 33, 66], we cannot use abstractions or optimization techniques that are tailored towards a specific type of application.

Finally, can we add kernel-level indirection without changing existing hardware, driver, or OS? To make it easier to adopt LITE, LITE should not require changes to existing system software or hardware. Ideally, it should be contained in a stand-alone kernel loadable module.

### 3.2.3 LITE Overall Architecture

LITE uses a level of indirection in the kernel space to virtualize RDMA. It manages and virtualizes RDMA resources for all applications that use LITE (applications that do not want to use LITE can still access native RDMA directly on the same machine). LITE talks to RDMA drivers and RNICs using the standard Verbs abstraction. Figure 3.2 presents LITE's overall architecture. We implemented LITE as a loadable kernel module in the 3.11.1 Linux kernel with around 15K lines of code.

Overall, LITE achieves the following design goals.

- LITE provides a flexible and easy-to-use abstraction to a wide range of datacenter applications.

- LITE preserves RDMA's three performance benefits: low latency, high bandwidth, and low CPU utilization.

- LITE's performance scales better than native RDMA.

- LITE offers fine-grained and flexible protection.

- It is efficient to share RDMA resources and easy to isolate performance with LITE.

- LITE needs no hardware, driver, or OS changes.

LITE supports three types of interfaces: memory-like operations, RPC and messaging, and synchronization primitives, and it supports both kernel-level and userlevel applications. We selected these semantics because they are familiar to datacenter application programmers. Most of LITE APIs have their counterparts in existing memory, distributed, and networking systems. Table 1 lists LITE's major APIs.

Internally, LITE consists of two main software stacks: a customized implementation of one-sided RDMA operations (Section 3.3), and a stack for RPC functions and messaging based on two-sided RDMA operations (Section 3.4). These parts share many resources, such as QPs, CQs, and LITE internal threads (Section 3.5).

|         | API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Explanation                             | Analogy         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|

|         | $LT_{-join}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Start LITE and join cluster             |                 |