# ELECTRICAL CHARACTERIZATION OF EMERGING ELECTRONIC DEVICES IN LOW AND HIGH POWER APPLICATIONS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Sami Alghamdi

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2019

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Peide Ye, Chair

School of Electrical and Computer Engineering

- Dr. Muhammad Ashraful Alam School of Electrical and Computer Engineering

- Dr. Babak Ziaie School of Electrical and Computer Engineering

- Dr. Arif Ghafoor School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

Head of the School Graduate Program

To my supportive Parents, my life partner and lovely wife, and to my kids

#### ACKNOWLEDGMENTS

I would like to express my sincere gratitude and great appreciation toward my advisor Prof. Ye for his tremendous and unbounded support of my PhD study at Purdue, for being my Masters and PhD mentor for a 7-years journey, for his guidance, and for helping me to finally make it this far. I would like to thank my advisory committee members: Prof. Muhammad A. Alam, Prof. Babak Ziaie, and Prof. Arif Ghafoor for their valuable discussions, feedback and suggestions. I would also like to express my appreciation to my colleagues in Professor Yes research group for their support and time to help me succeed in this work, especially, Mengwei Si and Dr. Jingyun Zhang for their devotion, mentorship during my research, and valuable contribution to my study. My gratitude to the rest of the group: Nathan Conrad, Dr. Hong Zhou, Gang Qiu, Dr. Yuchen Du, Dr. Linming Yang, Dr. Yexin Deng, Dr. Heng Wu, Dr. Xuefei Li, Wonil Chung, Jinhyun Noh and Dr. Hagyoul Bae.

I would also like to thank my friend Abdullah Alshaibani for his help and support and all my collaborators, Prof. Roy G. Gordon and Dr. Xiabing Lou from Harvard University.

Many thanks to Birck Nanotechnology Center and all the staff, Bill Rowe, Kenny Schwartz, Dave Lubelski, Jeremiah Shepard, Dan Hosler, Lorraine Fox, Geo Gardner, John Coy and Ira Young for their technical support on cleanroom facilities and Mary Jo, Nancy Black and other clerical staff for their helps. And all thanks to my parents, my wife and my family who had faith on me, unselfish and limitless support, and for being with me all along, especially during difficult times, throughout the years and from country to another.

## TABLE OF CONTENTS

|    |      |         |                                                        | Page   |

|----|------|---------|--------------------------------------------------------|--------|

| LI | ST O | F TAB   | LES                                                    | . viii |

| LI | ST O | F FIGU  | JRES                                                   | . ix   |

| SY | YMBC | DLS .   |                                                        | . xvi  |

| AI | BBRE | VIATI   | ONS                                                    | . xix  |

| AI | BSTR | ACT     |                                                        | . xxi  |

| 1  | INT  | RODU    | CTION                                                  | . 1    |

|    | 1.1  | Beyon   | d Moore's Law: It Is All About Power                   | . 1    |

|    | 1.2  | High N  | Mobility Channel Materials and Compound Semiconductors | . 3    |

|    |      | 1.2.1   | Germanium (Ge) and 2-D van der waals Materials         | . 5    |

|    |      | 1.2.2   | Gallium Nitride (GaN) and Gallium Oxide (Ga $_2O_3$ )  | . 9    |

|    | 1.3  | Emerg   | ging Transistors Structures                            | . 10   |

|    |      | 1.3.1   | Ferroelectric Insulators                               | . 10   |

|    |      | 1.3.2   | Steep-Slope Transistors                                | . 12   |

|    |      | 1.3.3   | Ferroelectric Transistors (Fe-FET)                     | . 13   |

|    | 1.4  | Electri | ical Characterization Methods for Modern Devices       | . 14   |

|    |      | 1.4.1   | AC Conductance                                         | . 15   |

|    |      | 1.4.2   | Pulsed Current-Voltage (Pulsed I-V)                    | . 16   |

|    |      | 1.4.3   | Conventional and Single Pulse Charge Pumping methods   | . 17   |

|    |      | 1.4.4   | Low-Frequency Noise (LFN)                              | . 19   |

|    | 1.5  | Thesis  | Overview                                               | . 22   |

| 2  |      |         | E CHARACTERISTICS OF EMERGING WIDE-BANDGAP             | . 25   |

|    | 2.1  | Introd  | uction                                                 | . 25   |

|    | 2.2  | Epitax  | tial Lattice Matched MgCaO Insulator on GaN            | . 26   |

| Page |

|------|

|------|

| 2.3 | MgCa                                                                             | O/GaN Interface Electrical Characterization                                                                                                                                                                                                                                                                                         | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 2.3.1                                                                            | Interface Traps via C-V and AC Conductance Methods                                                                                                                                                                                                                                                                                  | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.3.2                                                                            | Frequency and Temperature Dependent C-V                                                                                                                                                                                                                                                                                             | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.4 | $\beta$ -Ga                                                                      | $_{2}O_{3}$ : A Promising Wide-Bandgap Semiconductor $\ldots \ldots \ldots$                                                                                                                                                                                                                                                         | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.4.1                                                                            | $\beta$ -Ga <sub>2</sub> O <sub>3</sub> Surface Treatment and Preparation                                                                                                                                                                                                                                                           | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.4.2                                                                            | Comparative Interface Study of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> Surfaces                                                                                                                                                                                                                                                     | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.4.3                                                                            | C-V Measurements on $Al_2O_3/\beta$ -Ga $_2O_3$ MOSCAP                                                                                                                                                                                                                                                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.4.4                                                                            | Photo-Assisted C-V on $Al_2O_3/\beta$ - $Ga_2O_3$ MOSCAP                                                                                                                                                                                                                                                                            | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.5 | Summ                                                                             | ary                                                                                                                                                                                                                                                                                                                                 | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |                                                                                  |                                                                                                                                                                                                                                                                                                                                     | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1 | GaN N                                                                            | MOS-HEMT With MgCaO As Gate Dielectric                                                                                                                                                                                                                                                                                              | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 3.1.1                                                                            | Interface Trap Density using Pulsed IV                                                                                                                                                                                                                                                                                              | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 3.1.2                                                                            | Interface Trap Density using SPCP                                                                                                                                                                                                                                                                                                   | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 3.1.3                                                                            | Ultraviolet Light-Based I-V Method for Interface Traps Extrac-<br>tion in $\beta$ -Ga <sub>2</sub> O <sub>3</sub> FETs                                                                                                                                                                                                              | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |                                                                                  |                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1 | LFN N                                                                            | Measurements on $MoS_2 NC$ -FETs                                                                                                                                                                                                                                                                                                    | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

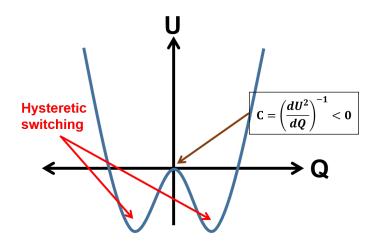

|     | 4.1.1                                                                            | Experimental Evidence of Negative Capacitance                                                                                                                                                                                                                                                                                       | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

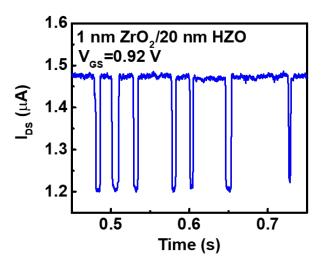

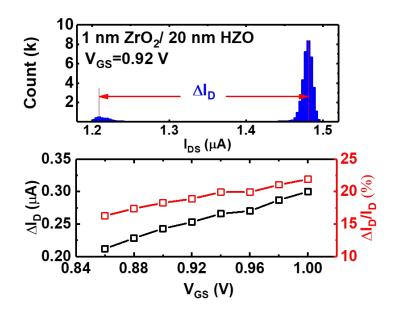

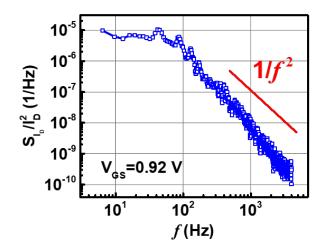

|     | 4.1.2                                                                            | Anomalous RTN Signal Observed in $MoS_2 NC$ -FETs                                                                                                                                                                                                                                                                                   | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

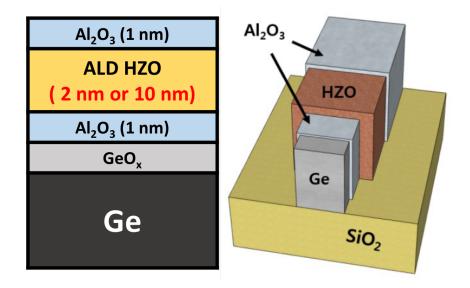

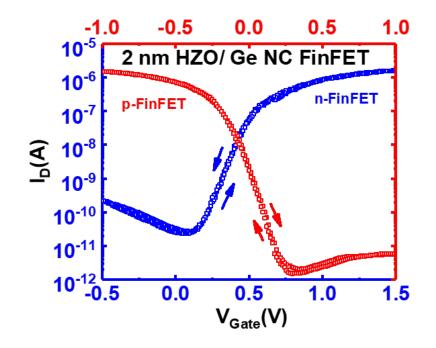

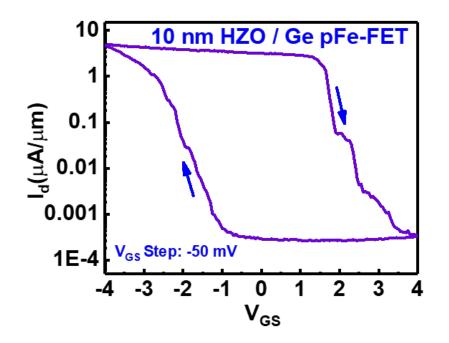

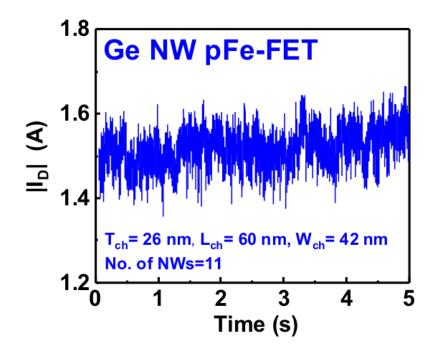

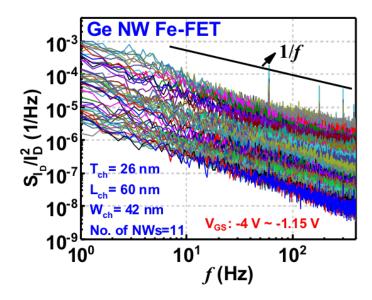

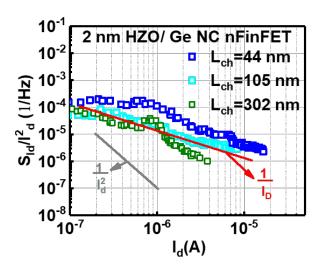

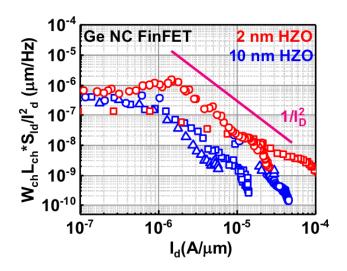

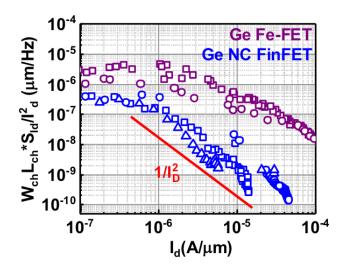

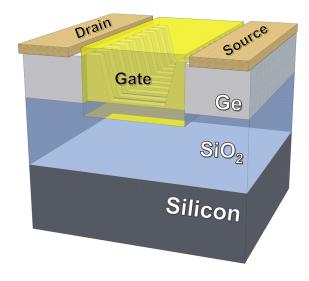

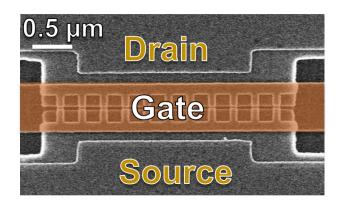

| 4.2 | LFN N                                                                            | Measurements on Ge NC-FinFET and Ge NW Fe-FET                                                                                                                                                                                                                                                                                       | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |                                                                                  |                                                                                                                                                                                                                                                                                                                                     | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1 | Introd                                                                           | uction                                                                                                                                                                                                                                                                                                                              | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

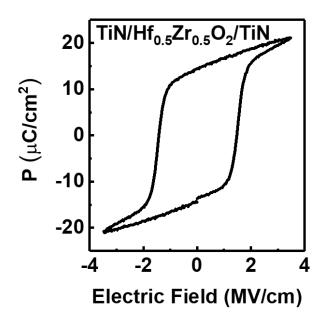

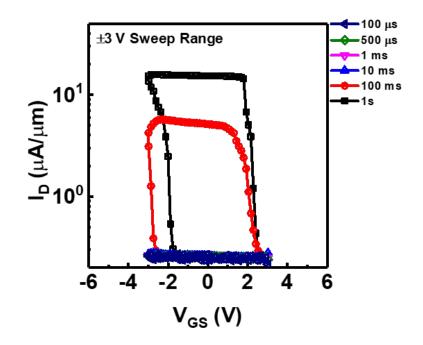

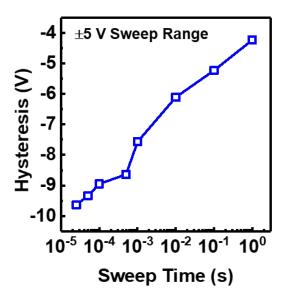

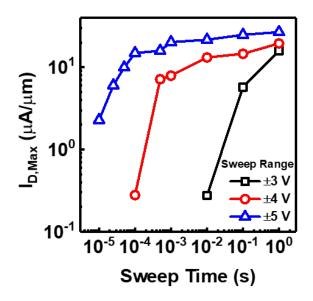

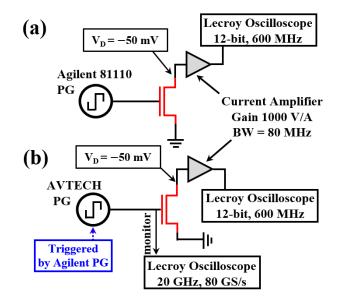

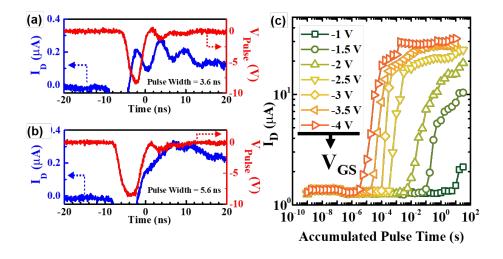

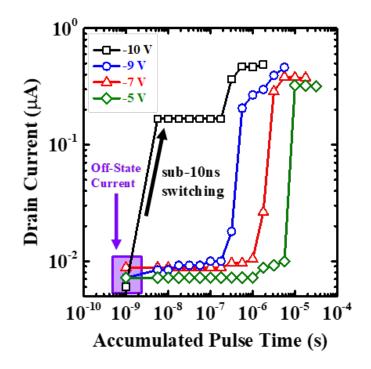

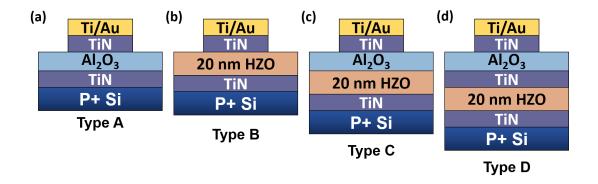

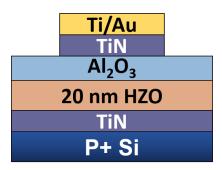

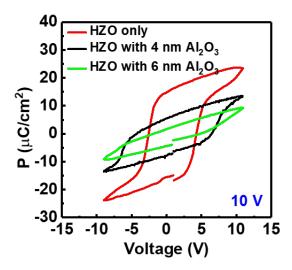

| 5.2 | Ferroe                                                                           | lectric HZO Polarization Switching Speed                                                                                                                                                                                                                                                                                            | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

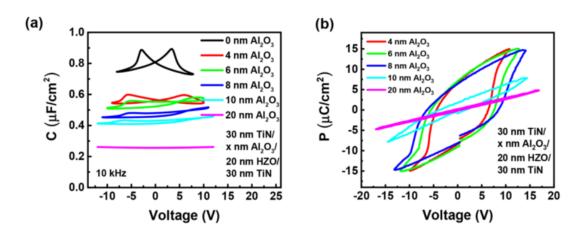

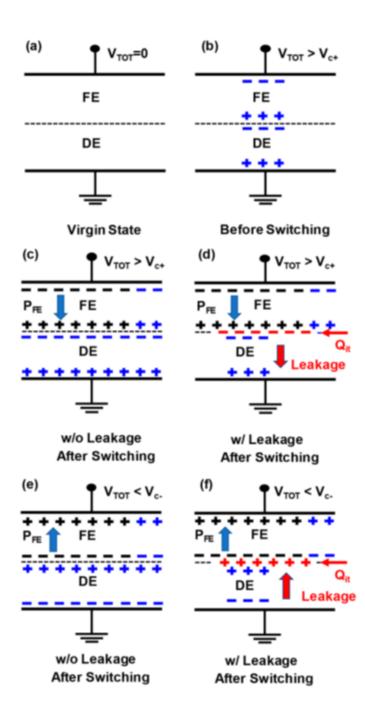

| 5.3 | Ferroe                                                                           | lectric HZO Polarization Switching Mechanism 1                                                                                                                                                                                                                                                                                      | 04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

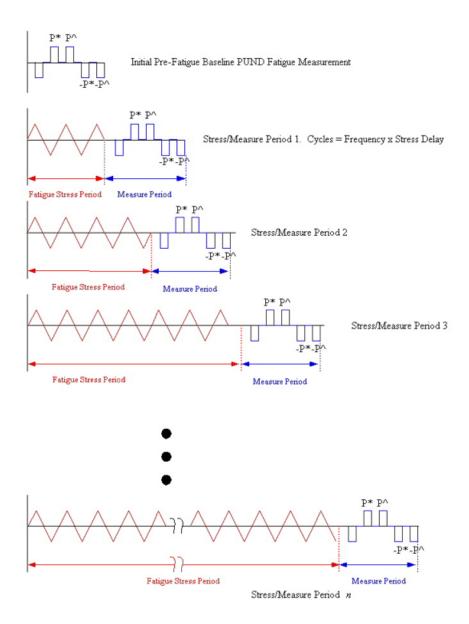

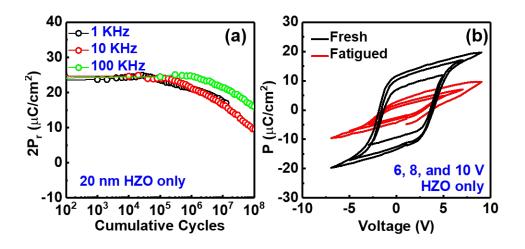

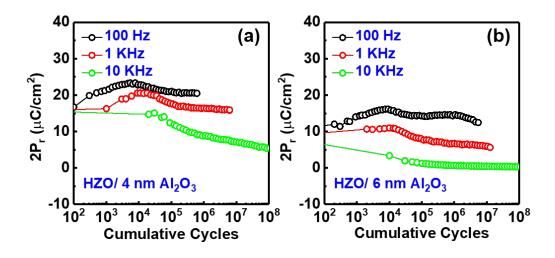

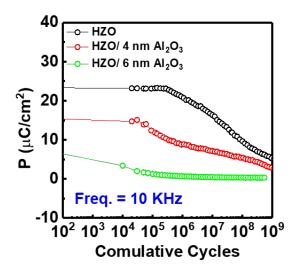

| 5.4 | Ferroe                                                                           | lectric HZO Polarization Switching Endurance 1                                                                                                                                                                                                                                                                                      | 09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 5.4.1                                                                            | Endurance Measurements                                                                                                                                                                                                                                                                                                              | 09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.4<br>2.5<br>DIR<br>TOF<br>3.1<br>4.1<br>4.2<br>REL<br>NIU<br>5.1<br>5.2<br>5.3 | 2.3.1<br>2.3.2<br>2.4 $\beta$ -Gay<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.3<br>2.4.4<br>2.5 Summ<br>DIRECT IN<br>CONSTRA<br>3.1 GaN M<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.1<br>3.1.2<br>3.1.3<br>NOISE ME<br>TRANSIST<br>4.1 LFN M<br>4.1.1<br>4.1.2<br>4.2 LFN M<br>4.1.1<br>4.1.2<br>4.2 LFN M<br>5.1 Introd<br>5.2 Ferroe<br>5.3 Ferroe | 2.3.1       Interface Traps via C-V and AC Conductance Methods         2.3.2       Frequency and Temperature Dependent C-V         2.4       β-Ga <sub>2</sub> O <sub>3</sub> : A Promising Wide-Bandgap Semiconductor         2.4.1       β-Ga <sub>2</sub> O <sub>3</sub> Surface Treatment and Preparation         2.4.2       Comparative Interface Study of β-Ga <sub>2</sub> O <sub>3</sub> Surfaces         2.4.3       C-V Measurements on Al <sub>2</sub> O <sub>3</sub> /β-Ga <sub>2</sub> O <sub>3</sub> MOSCAP         2.4.4       Photo-Assisted C-V on Al <sub>2</sub> O <sub>3</sub> /β-Ga <sub>2</sub> O <sub>3</sub> MOSCAP         2.5       Summary         DIRECT INTERFACE STUDIES ON WIDE-BANDGAP SEMICONDUC-         TORS TRANSISTORS         3.1       Gan MOS-HEMT With MgCaO As Gate Dielectric         3.1.1       Interface Trap Density using Pulsed IV         3.1.2       Interface Trap Density using SPCP         3.1.3       Ultraviolet Light-Based I-V Method for Interface Traps Extraction in β-Ga <sub>2</sub> O <sub>3</sub> FETs         NOISE MEASUREMENTS IN NEGATIVE CAPACITANCE FIELD-EFFECT         TRANSISTOR         4.1       LFN Measurements on MoS <sub>2</sub> NC-FETs         4.1.1       Experimental Evidence of Negative Capacitance         4.1.2       Anomalous RTN Signal Observed in MoS <sub>2</sub> NC-FETs         4.2       LFN Measurements on Ge NC-FinFET and Ge NW Fe-FET         RELIABILITY ISSUES WITH FERROELECTRIC HAFNIUM ZIRCO-         NUM OXIDE (HZO) |

#

| PUBLICATIONS | <br>• | • | • | • | • | • | • | • |  |  | • | • |  | • | • | • | • | • | • |  | • | • | • |

|--------------|-------|---|---|---|---|---|---|---|--|--|---|---|--|---|---|---|---|---|---|--|---|---|---|

|              |       |   |   |   |   |   |   |   |  |  |   |   |  |   |   |   |   |   |   |  |   |   |   |

|              |       |   |   |   |   |   |   |   |  |  |   |   |  |   |   |   |   |   |   |  |   |   |   |

5.4.2

130

## LIST OF TABLES

| Table |                                                   |     |          |  |  |

|-------|---------------------------------------------------|-----|----------|--|--|

| 1.1   | Electrical properties some semiconductor material | •   | 2        |  |  |

| 4.1   | Description of samples and device dimensions      | . ( | <u> </u> |  |  |

| 6.1   | HEMT and MOSHEMT GaN Devices                      | 1   | 17       |  |  |

## LIST OF FIGURES

| Figu | re Pa                                                                                                                                                                                                                                             | ge             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

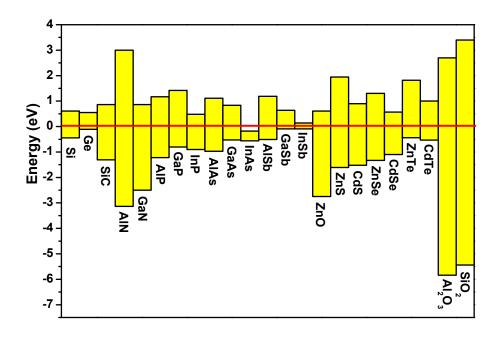

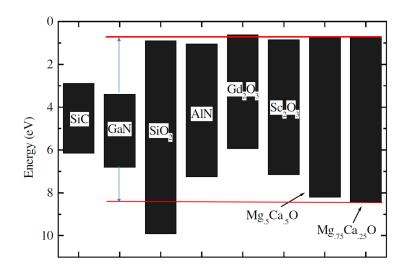

| 1.1  | Charge neutral level alignments for selected semiconductor materials                                                                                                                                                                              | 4              |

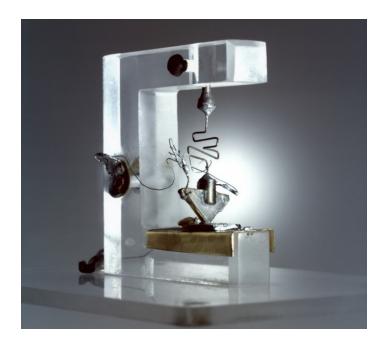

| 1.2  | The first Transistor made of Ge [1]                                                                                                                                                                                                               | 5              |

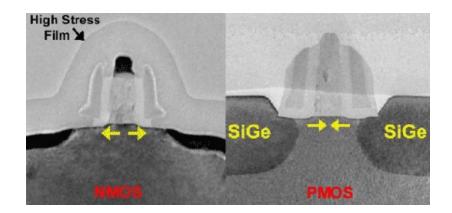

| 1.3  | Strain introduction in CMOS for mobility enhancement [3]                                                                                                                                                                                          | 6              |

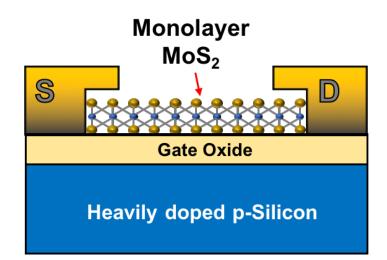

| 1.4  | Schematic of back gated MOSFET with $MoS_2$ as a channel                                                                                                                                                                                          | 8              |

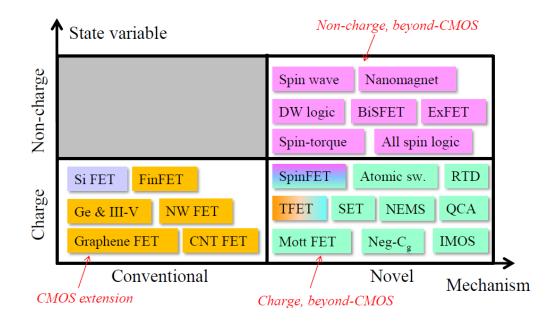

| 1.5  | A classification of emerging devices based on the state variables and the switching mechanisms. [15]                                                                                                                                              | 11             |

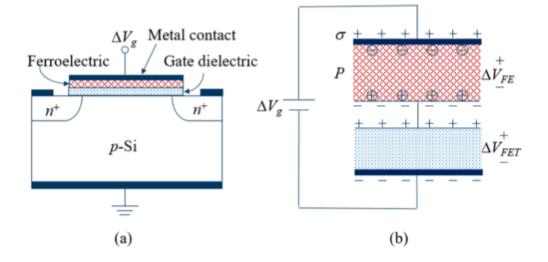

| 1.6  | Schematics of NC-FETs, (a) Device structure, and (b) illustration of the gate stack with Ferroelectric material. [20]                                                                                                                             | 14             |

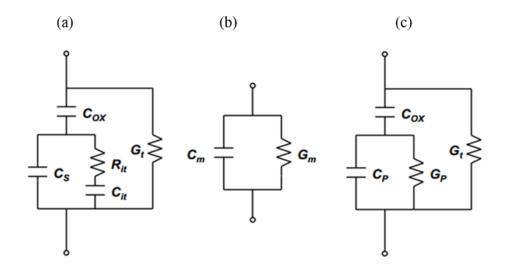

| 1.7  | Equivalent circuits of measurements; (a) an equivalent circuit model of the MOS capacitor, (b) the measured circuit, (c) a simplified circuit of (a) [24]                                                                                         | 15             |

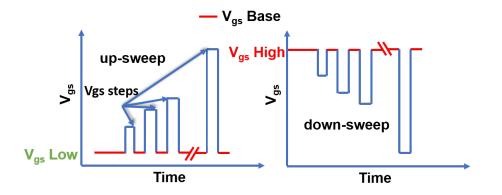

| 1.8  | Illustration of the pulsed I-V signal applied on gate                                                                                                                                                                                             | 17             |

| 1.9  | Schematic band diagram of n-MOSFET device showing the CP process<br>during the conventional CP measurements                                                                                                                                       | 18             |

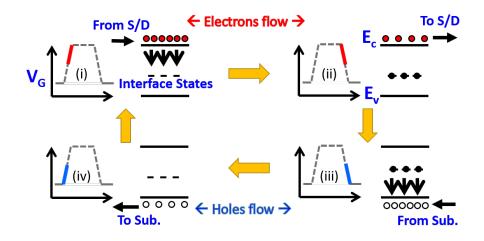

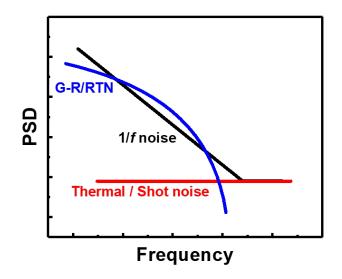

| 1.10 | Schematic representation of different types of noise power spectral density vs frequency in MOSFETs                                                                                                                                               | 20             |

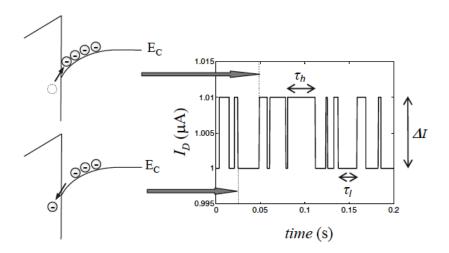

| 1.11 | Schematic representation of RTN noise along side a representation of the trapping de-trapping process. The drain current fluctuate between two distinct current levels when a channel electron moves in and out of a trap in the gate oxide [35]. | 22             |

| 2.1  | Band alignments for SiC, GaN with various dielectrics [38].                                                                                                                                                                                       | 27             |

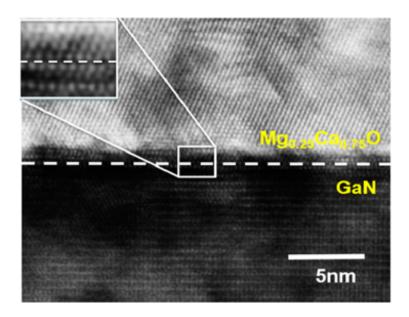

| 2.2  | Cross-sectional TEM of $Mg_{0.25}Ca_{0.75}O$ film grown on $GaN(0001)$ surface. [36]                                                                                                                                                              | 27             |

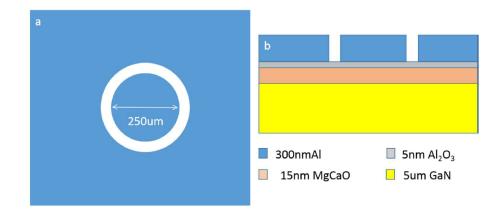

| 2.3  | (a) The top view, and (b) Side view of the $5 \text{ nm Al}_2O_3/15 \text{ nm Mg}_xCa_{1-x}O/GaN MOSCAPs.$ [36]                                                                                                                                   | <b>V</b><br>28 |

х

| rigu | II C                                                                                                                                                                                                                                                                                                                                                                                                                             | I ag    | 30 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----|

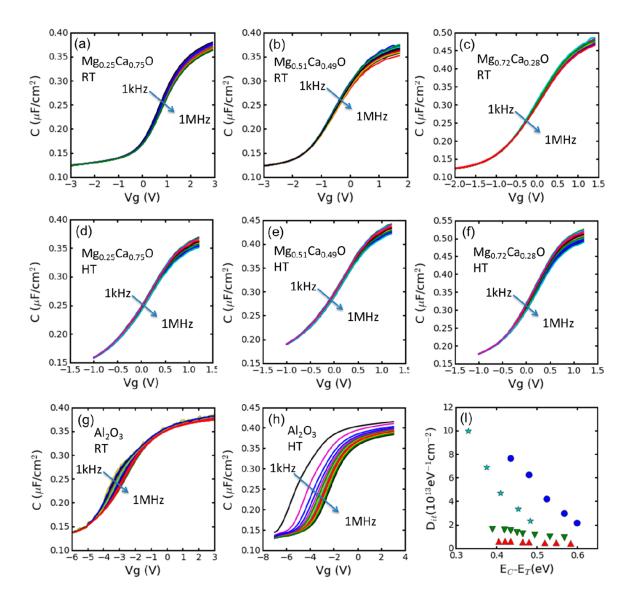

| 2.4  | C-V measurements for $Mg_xCa_{1-x}O$ /GaN and $Al_2O_3$ /GaN samples.<br>(a) to (c) at RT (20°C); (d) to (f) at 150°C, (g) 20°C 20 nm $Al_2O_3$ /GaN for and (h) at 150°C; (i) $D_{it}$ summary of four samples determined by the conductance method: (*) 20 nm $Al_2O_3$ / GaN, ( $\bigcirc$ ) 5 nm $Al_2O_3$ /15 nm $Mg_{0.72}Ca_{0.28}O$ /GaN, ( $\bigtriangledown$ ) 5 nm $Al_2O_3$ / 15 nm $Mg_{0.25}Ca_{0.75}O$ /GaN. [36] |         | 30 |

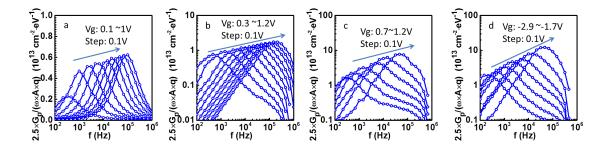

| 2.5  | $G_p/\omega$ vs. frequency at 150 °C. (a) 5 nm Al <sub>2</sub> O <sub>3</sub> / 15 nm Mg <sub>0.25</sub> Ca <sub>0.75</sub> O/GaN<br>(b) 5 nm Al <sub>2</sub> O <sub>3</sub> / 15 nm Mg <sub>0.51</sub> Ca <sub>0.49</sub> O/GaN (c) 5 nm Al <sub>2</sub> O <sub>3</sub> /15 nm Mg <sub>0.72</sub> Ca<br>(d) 20 nm Al <sub>2</sub> O <sub>3</sub> /GaN. [36]                                                                     |         |    |

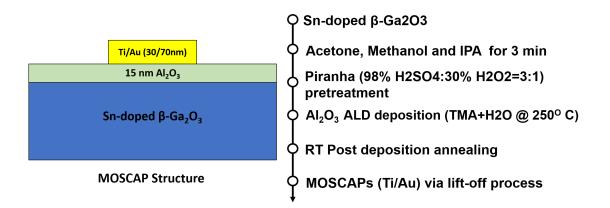

| 2.6  | Schematic of fabricated 15 nm $Al_2O_3/$ bulk $\beta$ -Ga <sub>2</sub> O <sub>3</sub> MOSCAP (left), and flow of fabrication process (right)                                                                                                                                                                                                                                                                                     | . 3     | 33 |

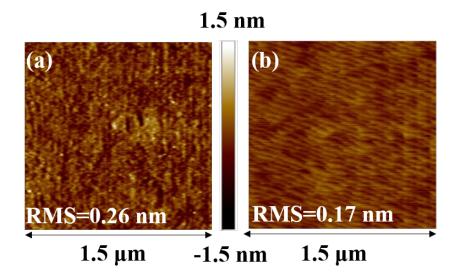

| 2.7  | (a) and (b) are atomic force microscopy images of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> without and wit piranha treatment, respectively [47].                                                                                                                                                                                                                                                                                  | . 3     | 34 |

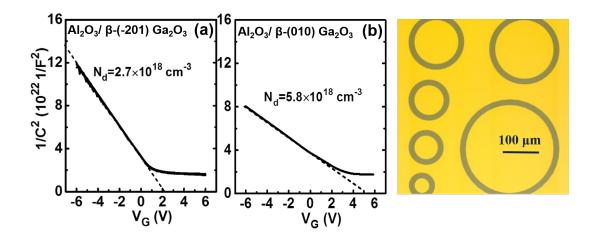

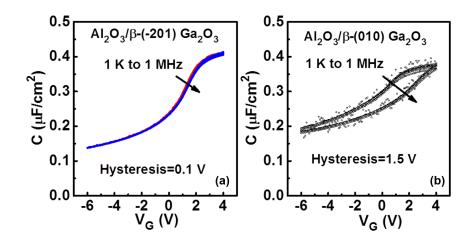

| 2.8  | characteristic as a function of $V_G$ for (a) $Al_2O_3/\beta$ -(-201)Ga <sub>2</sub> O <sub>3</sub> and (b) $Al_2O_3/\beta$ -(010)Ga <sub>2</sub> O <sub>3</sub> , and (c) is the top microscopic view of $Al_2O_3/\beta$ -Ga <sub>2</sub> O <sub>3</sub> MOS serial capacitors.                                                                                                                                                 | ېر<br>۱ | 35 |

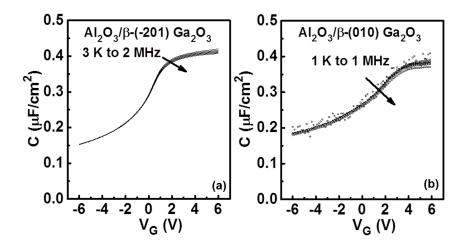

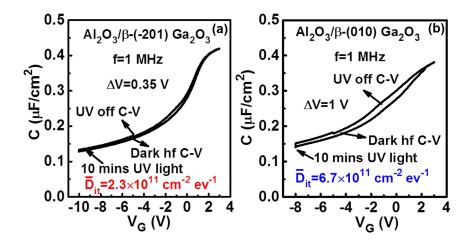

| 2.9  | $f$ -dependent C-V measurements of (a) Al <sub>2</sub> O <sub>3</sub> / $\beta$ -(-201)Ga <sub>2</sub> O <sub>3</sub> and (b) Al <sub>2</sub> O <sub>3</sub><br>(010)Ga <sub>2</sub> O <sub>3</sub> .                                                                                                                                                                                                                            |         | 36 |

| 2.10 | Bi-directional C-V measurement of $Al_2O_3/\beta$ -(-201)Ga <sub>2</sub> O <sub>3</sub> with hysteresis of 0.1 V (Left), and $Al_2O_3/\beta$ -(010)Ga <sub>2</sub> O <sub>3</sub> with hysteresis of 1.5 V (Right)                                                                                                                                                                                                               | . 3     | 37 |

| 2.11 | Photo-assisted C-V measurements of (a) $Al_2O_3/\beta$ -(-201)Ga <sub>2</sub> O <sub>3</sub> and (b) $Al_2O_3/\beta$ -(010)Ga <sub>2</sub> O <sub>3</sub> .                                                                                                                                                                                                                                                                      | . 3     | 38 |

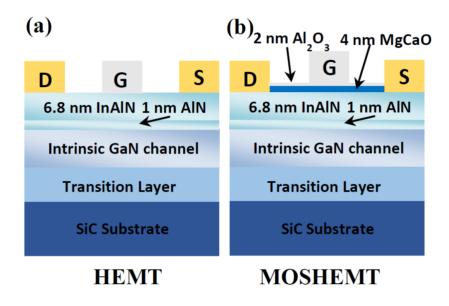

| 3.1  | Schematic of (a) GaN HEMT (left), (b) MOSHEMT (right) $\ldots \ldots$                                                                                                                                                                                                                                                                                                                                                            | . 4     | 11 |

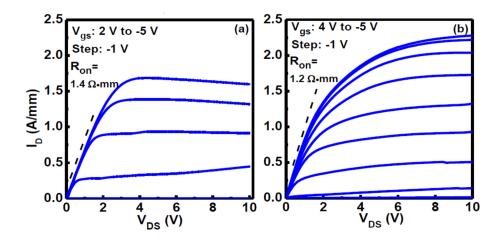

| 3.2  | (a) Output characteristics of GaN HEMT with an $I_{ds,max}=1.7$ A/mm, on-<br>resistance $R_{on}=1.4 \Omega \cdot m$ , $V_T=-1.75$ V, and $g_{m,max}=600$ mS/mm at $V_{ds}=4$ V. (b) Output characteristics of a GaN MOSHEMT with ALE MgCaO as gate dielectric. This device demonstrates an $I_{ds,max}$ of 2.3 A/mm and $R_{on}=1.2 \Omega \cdot m$ .                                                                            | . 4     | 12 |

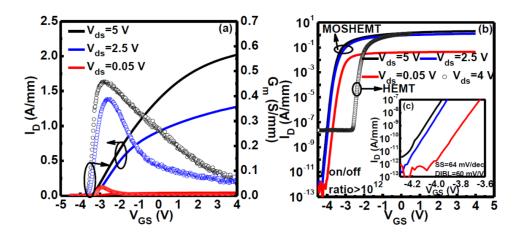

| 3.3  | (a) $I_d$ - $V_g$ transfer characteristics of MOSHEMT (b) Log-scale view of the $I_d$ - $V_g$ for both HEMT and MOSHEMT. A high on/off ratio higher that $10^{12}$ and $10^8$ are obtained for MOSHEMT and HEMT, respectively. (c) as the inset in shows the zoom-in view of $I_d$ - $V_g$ (for MOSHEMT) in the subthreshold region. SS of 64 mV/dec is observed with a small DIBL=60 mV/V                                       | . 4     | 13 |

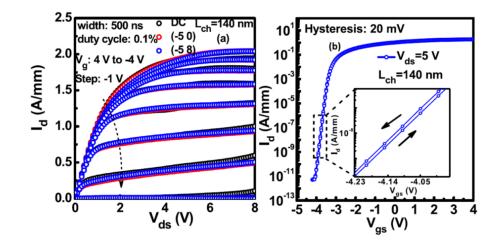

| 3.4  | (a) Pulsed I-V measurements with 500 ns pulse width and 0.1% duty cycle and (b) $I_d$ - $V_{gs}$ hysteresis of a MOSHEMT with $L_{ch} = 140 \text{ nm } [40] \dots$                                                                                                                                                                                                                                                              |         | 14 |

| Figu | re                                                                                                                                                                                                                                                                           | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

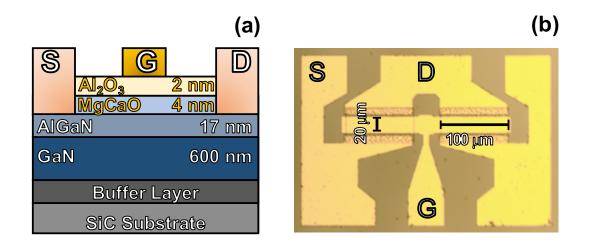

| 3.5  | (a) Schematic of the AlGaN/GaN MOS-HEMT. (b) Microscope image of a fabricated device.                                                                                                                                                                                        | . 46 |

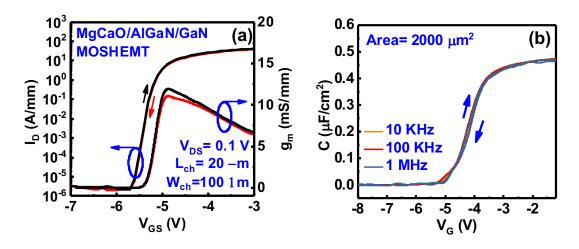

| 3.6  | (a) $I_D$ - $V_{GS}$ characteristics and transconductance $(g_m)$ of a representative AlGaN/GaN MOS-HEMT. (b) C-V characteristics of the same device at different frequencies.                                                                                               | . 47 |

| 3.7  | (a) Schematic diagram of SPCP experimental setup. (b) Sequence of cap-<br>ture and emission process within the band structure of the device channel<br>for the SPCP measurements.                                                                                            | . 49 |

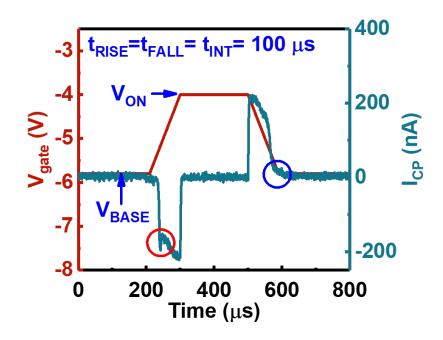

| 3.8  | An illustration of the applied gate pulse with the resulting charge pumping current $I_{cp}$ as a function of time. Electron capture and emission behaviors are observed in red and blue circles, respectivley                                                               | . 50 |

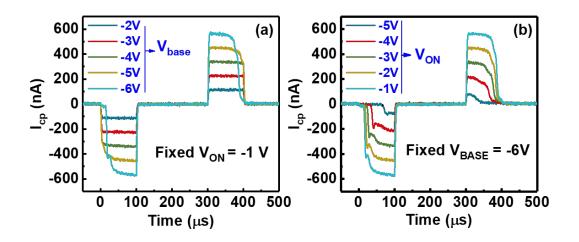

| 3.9  | Measured $I_{cp}$ vs time for (a) multiple $V_{BASE}$ levels with pulse maximum $V_{ON}$ held at -1 V and (b) multiple gate voltages $V_{ON}$ with $V_{BASE}$ being fixed. Both rise and fall edges are shown as measured directly by SPCP.                                  | . 51 |

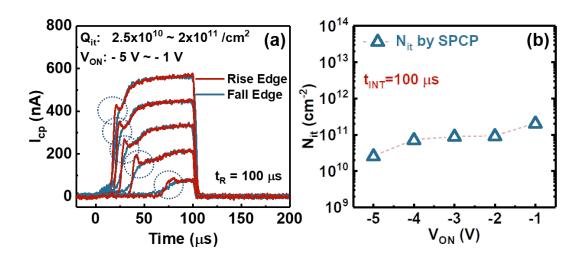

| 3.10 | (a) Measured $I_{cp}$ as a function of time at different $V_{ON}$ . $V_{BASE}$ is fixed at - 6 V. The current differences are compared for the purpose of $Q_{it}$ estimation in (b).                                                                                        | . 52 |

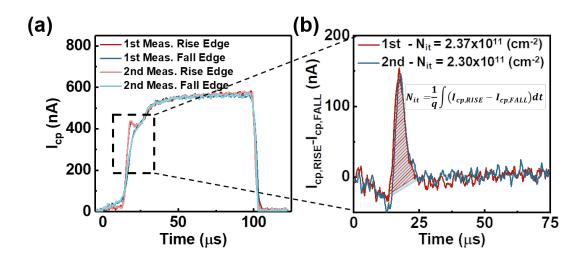

| 3.11 | Comparison of two subsequent measurements by single pulse charge pumping. (a) $I_{cp}$ versus time. (b) Nit extracted for each run                                                                                                                                           | . 53 |

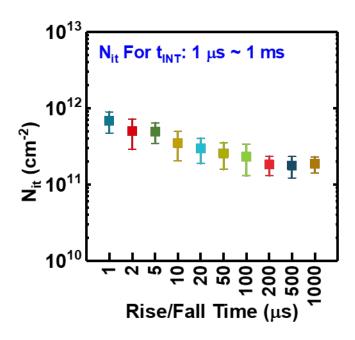

| 3.12 | Nit extracted from charge pumping current of 4-6 devices with various rise times.                                                                                                                                                                                            | . 54 |

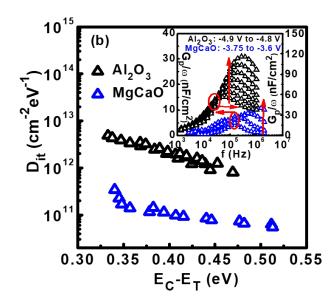

| 3.13 | $D_{it}$ distribution extracted from conductance method on GaN MOS-HEMT with $Al_2O_3$ as gate dielectric and MgCaO as gate dielectric.                                                                                                                                      | . 56 |

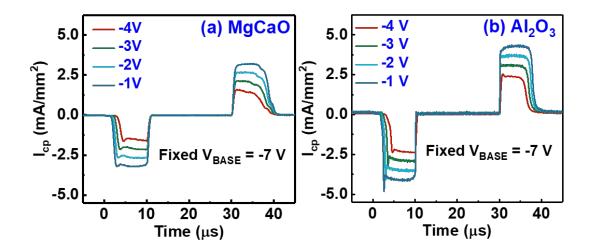

| 3.14 | Measured $I_{cp}$ vs time for multiple gate voltages $V_{ON}$ for (a) MgCaO as gate dielectric and (b) $Al_2O_3$ as gate dielectric.                                                                                                                                         | . 56 |

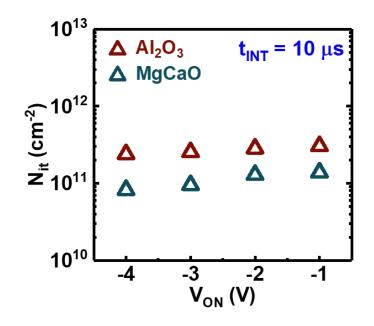

| 3.15 | Comparison of Nit versus $V_{ON}$ using SPCP method on GaN MOS-HEMT with MgCaO as gate dielectrics and $Al_2O_3$ as gate dielectrics                                                                                                                                         | . 57 |

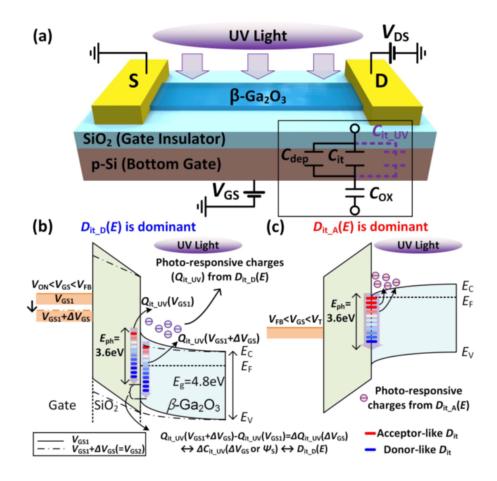

| 3.16 | (a) Schematic view of the measurement setup under a photonic state with the sub-bandgap UV light including the equivalent circuit model as the inset. (b) and (c) Energy band diagrams for the concept of simultaneous extractions of both $D_{it\_D}(E)$ and $D_{it\_A}(E)$ | . 60 |

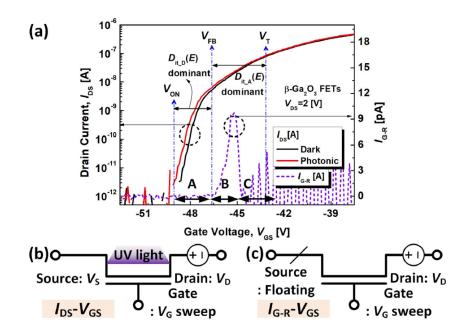

| 3.17 | (a) Measured $I_{DS}$ - $V_{GS}$ characteristics under dark (black line) and photonic (red line) states. The $I_{G-R}$ (dash line) was measured with the source terminal floating. Measurement setup for (b) $I_{DS}$ - $V_{GS}$ with UV light and (c) $I_{G-R}$ .           | . 62 |

xii

| Figu | re                                                                                                                                                                                                                                                                                                                                                               | Р | age |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

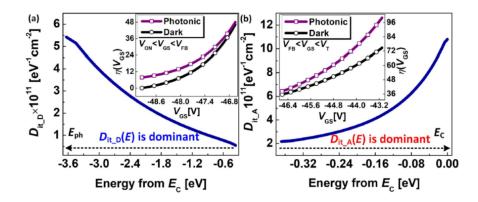

| 3.18 | Energy distribution of extracted $D_{it}$ [(a): $D_{it_D}(E)$ and (b): $D_{it_A}(E)$ ] via photo-responsive I-V characteristics with sub-bandgap UV light. The inset shows the extracted $\eta(V_{GS})$                                                                                                                                                          |   | 64  |

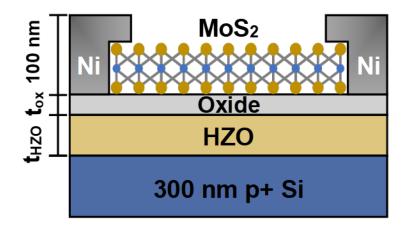

| 4.1  | Schematic diagram of a $MoS_2$ NC-FET. The device includes the p++ Si as gate electrode, HZO as the ferroelectric layer, $Al_2O_3$ , $HfO_2$ , or $ZrO_2$ as the oxide layer and 100 nm Ni as source/drain contacts.                                                                                                                                             |   | 68  |

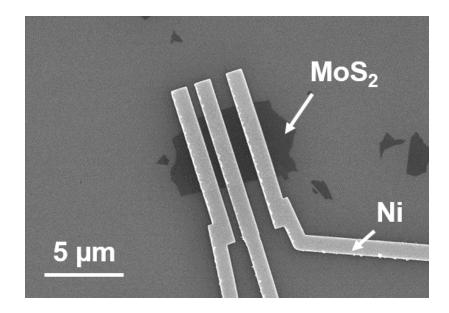

| 4.2  | Top-view SEM image of two $MoS_2$ NC-FETs, capturing the $MoS_2$ flake and Ni electrodes.                                                                                                                                                                                                                                                                        |   | 68  |

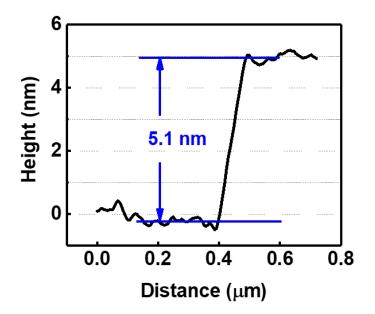

| 4.3  | Typical $MoS_2$ flake thickness measured by AFM for a $MoS_2$ NC-FET.                                                                                                                                                                                                                                                                                            |   | 69  |

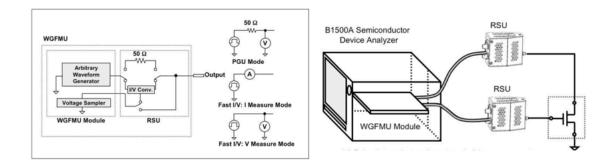

| 4.4  | Simplified circuit diagram of the WGFMU showing its operation modes (left) and Measurements setup (right)                                                                                                                                                                                                                                                        |   | 70  |

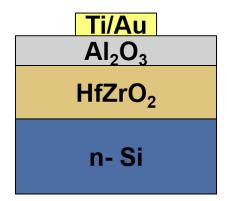

| 4.5  | M-I-Si capacitor structure schematic of the capacitor used in C-V and P-V measurements.                                                                                                                                                                                                                                                                          |   | 71  |

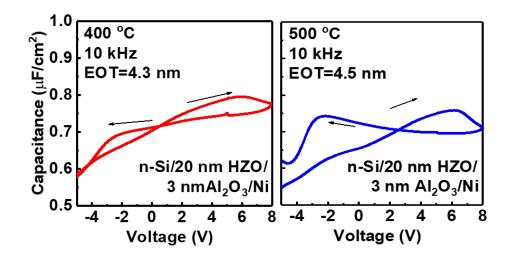

| 4.6  | C-V measurements of the M-I-M capacitor with different capacitance peak for forward and reveres $V_G$ sweeps.                                                                                                                                                                                                                                                    |   | 71  |

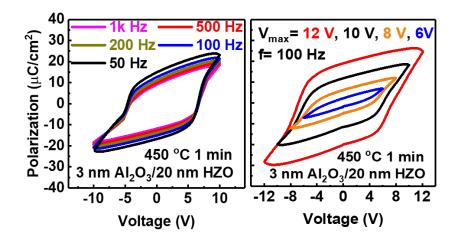

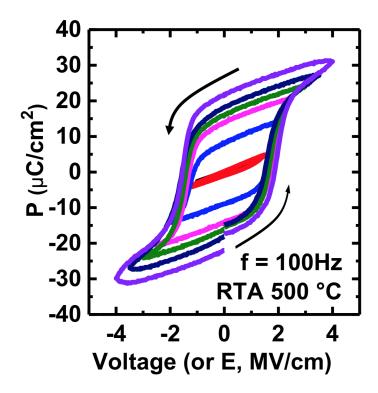

| 4.7  | (LEFT) Hysteresis loops of P-V for 20 nm HZO/3 nm $Al_2O_3$ annealed at 450 °C, measured from 50 Hz to 1 kHz. (RIGHT) Hysteresis loops of P-V for 20 nm HZO/3 nm $Al_2O_3$ annealed at 450 °C at voltage sweep ranges from 6V to 12 V.                                                                                                                           |   | 72  |

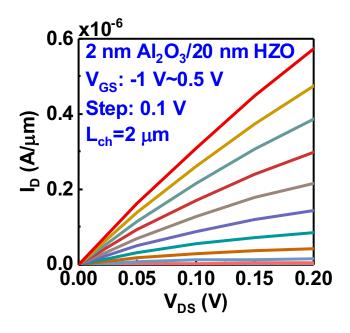

| 4.8  | $I_D$ - $V_{DS}$ characteristics of a MoS <sub>2</sub> NC-FET measured at room temper-<br>ature, W <sub>ch</sub> =5.7 $\mu$ m. The transistor exhibits good switching behavior<br>(I <sub>on</sub> /I <sub>off</sub> ;10 <sup>6</sup> 6), with linear relationship between $I_D$ and $V_{DS}$ which also<br>confirms minimal effect of the S/D Schottky barriers |   | 73  |

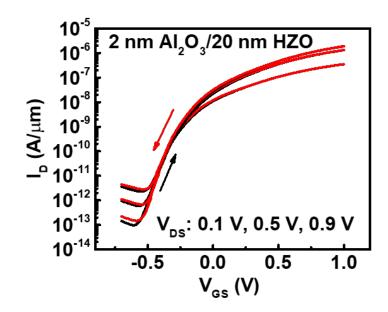

| 4.9  | $I_D$ - $V_{GS}$ characteristics of a MoS <sub>2</sub> NC-FET measured at room temperature.<br>This device has a L <sub>ch</sub> of 1 $\mu$ m, W <sub>ch</sub> of 5.7 $\mu$ m, channel thickness of 10 nm, and 2 nm Al <sub>2</sub> O <sub>3</sub> and 20 nm HZO as gate dielectric.                                                                             |   | 74  |

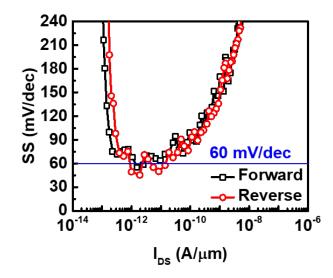

| 4.10 | SS vs. $I_D$ characteristics of the same device as in Fig.4.9. SS less than 60 mV/dec is obtained at room temperature for both forward and reverse gate voltage sweep directions.                                                                                                                                                                                |   | 75  |

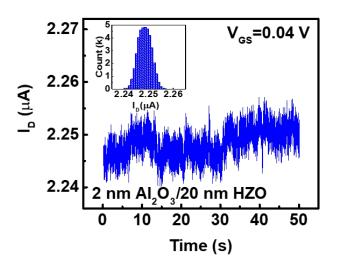

| 4.11 | SS vs. $I_D$ characteristics of the same device as in Fig.4.9. A typical $I_D$ fluctuation vs. time measured at $V_{GS}$ =0.04 V for a MoS <sub>2</sub> NC-FET with 2 nm Al <sub>2</sub> O <sub>3</sub> /20 nm HZO as gate dielectric.                                                                                                                           |   | 75  |

## $\mathbf{Fi}$

| Figure                                                                                                                                                                                                                                                                                                                                           | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

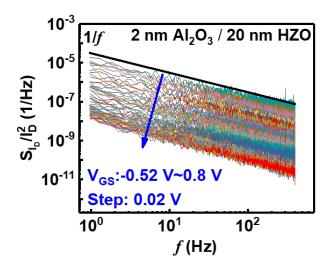

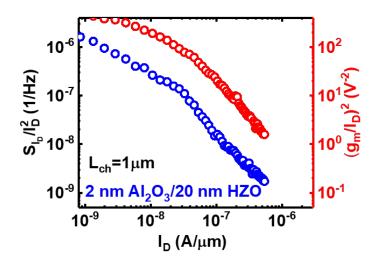

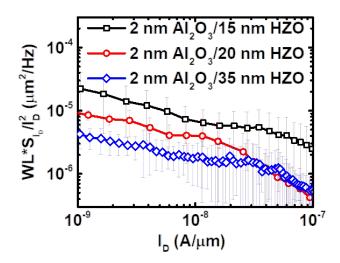

| 4.12 Normalized $I_D$ noise at f=10 Hz for a MoS <sub>2</sub> NC-FET with 2 nm Al <sub>2</sub> O <sub>3</sub> /20 nm HZO as gate dielectric. The non-linear behavior at low drain current and the proportional scaling with $(g_m/I_D)^2$ indicates charge number fluctuation to be the source of the low-frequency noise measured in this work. | . 76 |

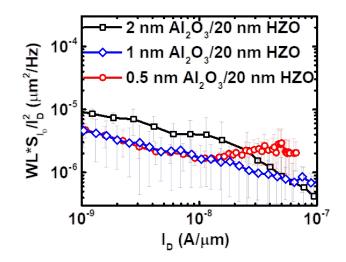

| 4.13 Normalized $I_D$ noise at f=10 Hz for a MoS <sub>2</sub> NC-FET with 2 nm Al <sub>2</sub> O <sub>3</sub> /20 nm HZO as gate dielectric. The non-linear behavior at low drain current and the proportional scaling with $(g_m/I_D)^2$ indicates charge number fluctuation to be the source of the low-frequency noise measured in this work. | . 77 |

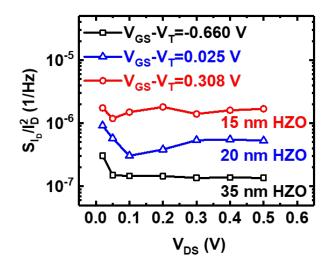

| 4.14 Normalized $I_D$ noise vs. $V_{DS}$ at f=10 Hz for MoS <sub>2</sub> NC-FETs with 2 nm Al <sub>2</sub> O <sub>3</sub> and HZO from 15 nm to 35 nm as gate dielectric. The weak dependence of $S_{ID}$ above $V_{DS}$ = 0.1 V suggests the noise mostly comes from the channel instead of Schottky contacts.                                  | . 78 |

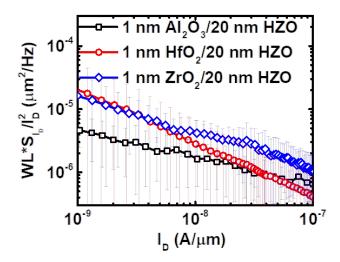

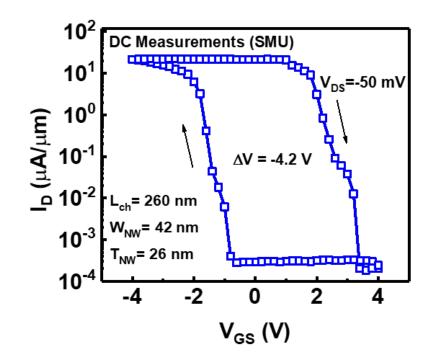

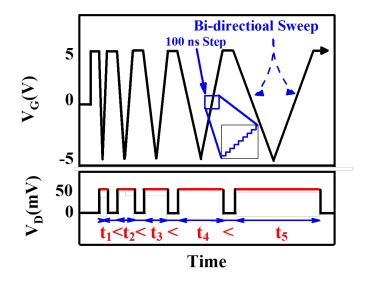

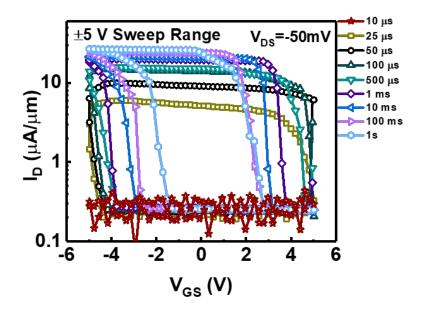

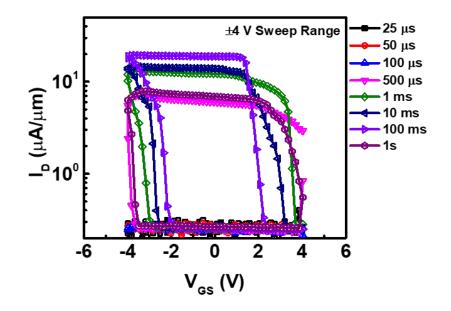

| 4.15 Normalized $I_D$ noise vs. $I_D$ at f=10 Hz for MoS <sub>2</sub> NC-FETs with 1 nm different interfacial oxides and 20 nm HZO as gate dielectric                                                                                                                                                                                            | . 78 |