# TEST GENERATION AND RESYNTHESIS PROCEDURES FOR TEST AND DIAGNOSIS QUALITY

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Naixing Wang

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2019

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Prof. Irith Pomeranz, Chair School of Electrical and Computer Engineering Prof. Raymond A. Decarlo

School of Electrical and Computer Engineering

- Prof. Anand Raghunathan School of Electrical and Computer Engineering

- Prof. Vijay Raghunathan School of Electrical and Computer Engineering

### Approved by:

Prof. Dimitrios Peroulis

Head of the School Graduate Program

To my parents for their unconditional love and support and to Yue.

#### ACKNOWLEDGMENTS

I would like to express my gratitude to my advisor, Professor Irith Pomeranz, for her inspiration, encouragement and guidance throughout my Ph.D. study. Her advices and feedback has been priceless. This work would not have been accomplished without her guidance.

I am also greatly thankful to my lab mate Dr. Shraddha Bodhe for always being there encourage me and give me valuable advices.

I also would like to thank Professor Raymond A. Decarlo, Professor Anand Raghunathan and Professor Vijay Raghunathan for serving on my advisory committee. Particularly, I would like to thank Dr. Xijiang Lin and Dr. Brady Benware from Mentor, A Siemens Business, Dr. Bo Yao, Dr. Srikanth Venkataraman, Dr. Enamul Amyeen and Dr. Arani Sinha from Intel Corporation, Professor Sudhakar M. Reddy from University of Iowa for their contributions to this work.

In addition, I would like to thank Semiconductor Research Corporation (SRC) and National Science Foundation (NSF) for providing the grants to support this work.

## TABLE OF CONTENTS

|    |       |           |                                                             | Pa  | age  |

|----|-------|-----------|-------------------------------------------------------------|-----|------|

| LI | ST O  | F TAB     | LES                                                         | . 1 | viii |

| LI | ST O  | F FIGU    | JRES                                                        | •   | ix   |

| A] | BSTR  | ACT       |                                                             | •   | x    |

| 1  | Intro | oduction  | 1                                                           | •   | 1    |

|    | 1.1   | Delay     | Fault Testing                                               | •   | 1    |

|    |       | 1.1.1     | Transition Delay Fault Model                                | •   | 1    |

|    |       | 1.1.2     | Scan-based Testing for Transition Delay Fault               | •   | 2    |

|    |       | 1.1.3     | Overtesting and Functional Broadside Test                   | •   | 3    |

|    |       | 1.1.4     | Contribution                                                | •   | 4    |

|    | 1.2   | Defect    | Diagnosis                                                   | •   | 5    |

|    |       | 1.2.1     | Simulation-based Diagnosis                                  | •   | 5    |

|    |       | 1.2.2     | Diagnosis for Multiple Defects                              | •   | 6    |

|    |       | 1.2.3     | Contribution                                                | •   | 8    |

|    | 1.3   | System    | natic Defects Based on DFM guidelines                       | •   | 8    |

|    |       | 1.3.1     | Testing Systematic Defects Based on DFM Guidelines          | •   | 8    |

|    |       | 1.3.2     | Contribution                                                | •   | 10   |

|    | 1.4   | Organ     | ization                                                     | •   | 12   |

| 2  | Func  | ctional l | Broadside Test Generation Using a Commercial ATPG Tool      | •   | 13   |

|    | 2.1   | Introd    | uction                                                      | •   | 13   |

|    | 2.2   | Genera    | ation of Functional Broadside Tests                         | •   | 17   |

|    |       | 2.2.1     | Test Generation                                             | •   | 17   |

|    |       | 2.2.2     | Finding Reachable States and Constructing $R_{\text{next}}$ | •   | 19   |

|    |       | 2.2.3     | Termination Conditions                                      | •   | 20   |

|    |       | 2.2.4     | Multi-cycle Test Generation                                 |     | 21   |

vi

|   |     |        |                                                                                 | -  |

|---|-----|--------|---------------------------------------------------------------------------------|----|

|   | 2.3 | Experi | imental Results                                                                 | 21 |

| 3 |     |        | the Resolution of Multiple Defect Diagnosis by Removing and ests                | 27 |

|   | 3.1 | Introd | uction                                                                          | 28 |

|   | 3.2 | Backg  | round                                                                           | 31 |

|   | 3.3 | Procee | lure Based on Test Removal                                                      | 32 |

|   | 3.4 | Procee | lure Based on Test Selection                                                    | 33 |

|   | 3.5 | Experi | imental Results                                                                 | 36 |

| 4 | 0   |        | thesis for Avoiding Undetectable Faults Based on DFM Guide-<br>ell-Based Design | 42 |

|   | 4.1 | Introd | uction                                                                          | 43 |

|   | 4.2 | Backg  | round                                                                           | 46 |

|   | 4.3 | Resynt | thesis Procedure                                                                | 48 |

|   | 4.4 | Backtr | cacking Procedure                                                               | 52 |

|   | 4.5 | Experi | imental Results                                                                 | 54 |

| 5 | v   |        | ynthesis by Applying DFM Guidelines to Avoid Low-CoverageCell-Based Design      | 59 |

|   | 5.1 | Introd | uction                                                                          | 60 |

|   | 5.2 | Undet  | ectable Faults Related to DFM Guideline Violations                              | 63 |

|   |     | 5.2.1  | Analysis of DFM Guideline Violations                                            | 64 |

|   |     | 5.2.2  | Detectable Defects Modeled by Undetectable Faults                               | 64 |

|   |     | 5.2.3  | Circuit Areas with Poor Coverage                                                | 67 |

|   |     | 5.2.4  | Coverage for Faults with Weighted DFM Guidelines                                | 69 |

|   | 5.3 | Layout | t Resynthesis                                                                   | 71 |

|   |     | 5.3.1  | Fixing DFM Guideline Violations                                                 | 71 |

|   |     | 5.3.2  | Layout Resynthesis Procedure                                                    | 72 |

|   | 5.4 | Experi | imental Results                                                                 | 74 |

|   |     | 5.4.1  | Layout Resynthesis Procedure                                                    | 76 |

|   |     | 5.4.2  | Circuits with Test Points                                                       | 79 |

## Page

vii

| 5.4.3      | Circuits after Logic Resynthesis    | 32 |

|------------|-------------------------------------|----|

| 5.4.4      | Weighted DFM Guidelines             | 3  |

| 5.4.5      | Circuits with High Cell Utilization | 34 |

| 6 Summary  |                                     | 6  |

| REFERENCES | S                                   | 88 |

| VITA       |                                     | )6 |

| PUBLICATIO | NS                                  | )7 |

## LIST OF TABLES

| Tab | le Page                                                                      | Э |

|-----|------------------------------------------------------------------------------|---|

| 1.1 | Multiple Defects Cause Large Candidate Fault Set                             | 7 |

| 2.1 | Multi-cycle Functional Broadside Tests with Unconstrained Input Vectors . 23 | 3 |

| 2.2 | Fault Coverage Achieved with All-0 State                                     | 5 |

| 2.3 | Hamming Distance                                                             | 3 |

| 3.1 | Experimental Results (Same Coverage and Precision)                           | ) |

| 3.2 | Experimental Results (Different Coverage or Precision)                       | ) |

| 3.3 | Statistical Analysis                                                         | ) |

| 4.1 | Clustered undetectable faults                                                | 3 |

| 4.2 | Experimental results                                                         | 7 |

| 5.1 | DFM Guideline Violations                                                     | 5 |

| 5.2 | Uncovered Short Defects                                                      | 7 |

| 5.3 | Layouts with 70% Cell Utilization                                            | 3 |

| 5.4 | Layout Resynthesis (Benchmarks)                                              | 3 |

| 5.5 | Layout Resynthesis (OpenSPARC T1)                                            | 9 |

| 5.6 | Circuits with Test Points                                                    | ) |

| 5.7 | Circuits after Logic Resynthesis                                             | 2 |

| 5.8 | Weighted DFM Guidelines                                                      | 3 |

| 5.9 | Circuits with Higher Cell Utilization                                        | 5 |

## LIST OF FIGURES

| Figu | Ire                                                                                                  | Pa   | ge |

|------|------------------------------------------------------------------------------------------------------|------|----|

| 1.1  | Example of a transition delay fault                                                                  |      | 2  |

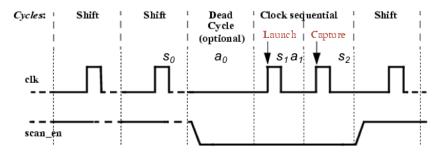

| 1.2  | Timing waveform of a broadside test                                                                  |      | 3  |

| 2.1  | Functional Broadside Test Generation Flowchart.                                                      |      | 17 |

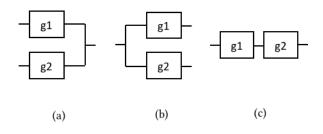

| 4.1  | Adjacent Gates.                                                                                      |      | 47 |

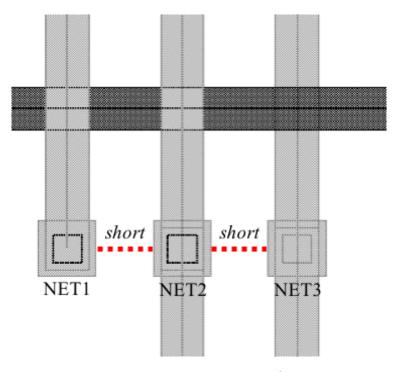

| 5.1  | Potential short defects.                                                                             |      | 65 |

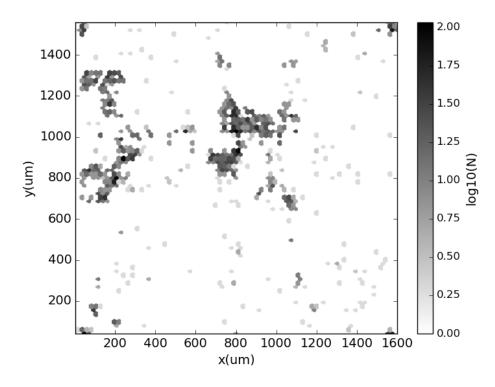

| 5.2  | Undetectable external faults related to DFM guideline violations in <i>sparc_f</i>                   | ťpu. | 68 |

| 5.3  | Coverages for the undetectable external faults in <i>sparc_fpu</i>                                   |      | 69 |

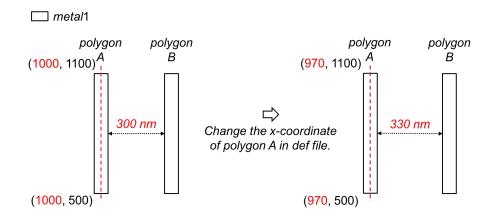

| 5.4  | Fixing a DFM guideline violation                                                                     |      | 71 |

| 5.5  | Coverages of the original neighborhoods of undetectable faults in <i>sparc_fpu</i> after resynthesis |      | 80 |

#### ABSTRACT

Wang, Naixing Ph.D., Purdue University, December 2019. Test Generation and Resynthesis Procedures for Test and Diagnosis Quality. Major Professor: Irith Pomeranz.

Testing and diagnosis are performed to detect and identify manufacturing failures in integrated circuits. In this dissertation, we focus on three important issues in test and diagnosis. The solutions to these issues are implemented using commercial EDA tools. No modification to the commercial tools is required. Thus, they can be easily applied to complex designs with state-of-the-art features. We first address overtesting of delay faults. Overtesting may occur when the circuit is brought into states that cannot be reached during functional operations. We address this issue by generating functional broadside tests using reachable states as scan-in states. Next, we address the issue of improving the resolution of multiple-defect diagnosis by ignoring certain tests. A feature of commercial defect diagnosis tools is used to avoid losing accuracy. Last, we address the issue of avoiding undetectable faults that model potential systematic defects caused by design-for-manufacturability (DFM) guideline violations in a cell-based design. We demonstrate that these undetectable faults tend to cluster in certain areas of the circuit, resulting in circuit areas with low coverage. The missing tests may allow detectable defects in these areas to escape detection. This can impact the defective-parts-per-million (DPPM) and reliability significantly since the defects are likely to be systematic. We address this issue in a cell-based design by eliminating the undetectable faults related to DFM guidelines that are internal and external to cells. We first propose a logic resynthesis procedure to eliminate large clusters of undetectable faults that are internal to cells. Next, we propose a layout resynthesis procedure that eliminates undetectable faults external to cells by making fine changes to the layout so as to fix the corresponding DFM guideline violations.

#### 1. INTRODUCTION

Aggressive scaling of integrated circuit (IC) technologies continues to decrease device sizes and increase circuit complexity. The scaling of integrated circuit (IC) technologies has brought about many benefits including faster devices, lower power consumption, reduced chip sizes and advanced functionality. However, the continuous shrinking of device sizes also increases the systematic imperfection and random variation in a highly complex manufacturing process. As a result, for each smaller process technology node, the chips are increasingly impacted by deviations in manufactured patterns from the intended design. This can impact the yield and defective-partsper-million (DPPM) significantly. As the occurrence of defects is expected to be prominent, it is more important than ever to perform testing and diagnosis with high quality.

In this dissertation, three important issues related to delay fault testing, defect diagnosis and systematic defects based on design-for-manufacturability (DFM) guidelines are discussed to improve the quality of testing and diagnosis. The solutions to these issues are implemented using commercial EDA tools. No modification to the commercial tools is required. Thus, they can be easily applied to complex designs with state-of-the-art features.

#### 1.1 Delay Fault Testing

#### 1.1.1 Transition Delay Fault Model

Defects that cause faulty timing behaviors of a circuit are modeled by delay faults. One of the most widely used delay fault models is transition delay fault model [1]. The transition fault model captures timing-related defects that cause slow-to-rise transitions or/and slow-to-fall transitions at gate pins in the circuit. Under transition delay fault model, it is assumed that the extra delay caused by a transition fault at a gate pin is large enough such that the delay of every path passing through this gate pin exceeds the desired clock period.

For illustration, in Fig. 1.1, a slow-to-rise transition fault is at the output Y of a two-input AND gate. Input B has a constant logic value 0. The logic value of input A changes from 0 to 1 at  $t_1$ . If the circuit is fault-free, the logic value of Y should be changed to 1 at the required time point  $t_2$ , where  $t_2 - t_1$  is the desired clock period. However, due to the slow-to-rise transition fault at Y, the logic value of Y remains 0 at  $t_2$ . Therefore, the circuit cannot operate correctly.

Fig. 1.1.: Example of a transition delay fault.

#### 1.1.2 Scan-based Testing for Transition Delay Fault

Sequential circuits contain state elements such as latches and flip-flops. The existence of state elements increases the complexity of generating tests for the circuit. In order to improve the testability of a sequential circuit, scan structure is inserted by replacing the state elements with scannable state elements (scan cells) and then stitching the scan cells into scan chains [2]. The scan cells can then be used for controlling circuit states and observing test responses.

To test a transition fault in a scan-based circuit, a two-pattern test are required. We denote a two-pattern test by  $\langle s_0, a_0 \rangle$  and  $\langle s_1, a_1 \rangle$ .  $s_0$  and  $s_1$  are state values.  $a_0$ and  $a_1$  are primary input values. The first pattern  $\langle s_0, a_0 \rangle$  is used for initializing the target fault site. The second pattern  $\langle s_1, a_1 \rangle$  is used for activating the fault by launching a transition at the fault site, and propagating the response to a primary output or state element. If the captured value indicates that the logic involved does not transit as expected during the desired clock period, the transition fault is expected to be present at the target fault site.

One of the widely used types of test for detecting transition delay fault is broadside test [3]. The advantage of broadside test is that it does not require scan enable signal to be shifted at-speed. Therefore, the scan enable does not need to be routed as a timing critical clock. Under a broadside test,  $s_0$  is the initial state that is scanned into the scan cells, and  $s_1$  is determined by the response of the circuit to  $\langle s_0, a_0 \rangle$ . A broadside test can thus be denoted by  $\langle s_0, a_0, a_1 \rangle$ . The circuit is tested by first shifting in the scan-in state  $s_0$  at slow speed in test mode. Two at-speed clock cycles are then pulsed for launch transition and capture response in functional mode. Once the test response is captured, the scan-out state can be shifted out at slow speed in test mode. The timing requirement for a broadside test is illustrated in Fig. 1.2. Note that the dead cycle is used for guaranteeing that the scan enable signal is off, and it is optional.

Fig. 1.2.: Timing waveform of a broadside test.

#### 1.1.3 Overtesting and Functional Broadside Test

Scan-based testing may cause overtesting of transition faults when the circuit is brought to states that cannot be reached during functional operations [4]. The existence of overtesting can fail a good circuit, and thus resulting in significant yield loss. Specifically, overtesting can impact the yield in the following ways.

- Overtesting can cause non-functional operations, which can lead to a higher switching activity [5,6]. This can result in excessive current demands, and thus resulting in voltage drops that slow down the circuit and cause a good circuit to fail.

- Overtesting may activate slow logic that can only be activated during nonfunctional mode, and thus causing the circuit to appear slower [4].

Thus, detecting transition faults under functional operation conditions is necessary in order to address overtesting and avoid unnecessary yield loss.

Different strategies to address overtesting are described in [4–15]. The solutions proposed in [4–8, 12–15] use functional constraints during test generation to avoid non-functional states and the resulting high current demands. These methods do not guarantee functional operation conditions during the functional capture cycles where delay faults are detected, and therefore, do not guarantee that overtesting can be avoided.

The approaches described in [9–11] create functional operation conditions during the functional capture cycles of every generated test by using reachable states as scan-in states. The generated tests are referred to as functional broadside tests, as the functional operations are guaranteed when applying these tests.

#### 1.1.4 Contribution

The procedures for generating functional broadside tests from [9–11] are implemented using academic ATPG tools. The part of contribution of this dissertation is demonstrating that it is possible to use a commercial ATPG tool for generating functional broadside tests. In particular, a commercial ATPG tool is used for addressing the challenge of identifying reachable states that are useful as scan-in states efficiently. This will allow functional broadside tests to be generated for state-of-the-art circuits with features that are not handled by academic tools.

#### 1.2 Defect Diagnosis

#### 1.2.1 Simulation-based Diagnosis

After generating a test set, the testing of a circuit is accomplished by applying the tests to this circuit on an Automatic Test Equipment (ATE). If the observed responses and the expected responses to all the tests in the test set are the same, then the circuit under test passes the test, otherwise it fails. For circuits that fail during testing, it is important to identify the locations and the root causes of the failures, so as to achieve a fast yield ramp up. For this purpose, the differences between the observed and the expected responses are recorded in a fail-log.

Defect diagnosis is then carried out to analyze the fail-log of every failing circuit. The aim of defect diagnosis is to determine the root causes in the defective circuits. With a high-quality defect diagnosis procedure, yield ramp up can be achieved more quickly. Typically, The output of defect diagnosis is a list of fault candidates that are identified as the potential causes of the failing circuit.

One of the wildly used diagnosis procedures is based on effect-cause fault simulation [16]. The similar procedure is also used in leading commercial defect diagnosis tools. The procedure can be summarized as follows.

- 1. Perform path-tracing to obtain an initial candidate list by analyzing all the failing tests. An initial candidate fault is identified if it satisfies the following requirements:

- The fault resides in the fan-in cone of an affected observe point of a failing test.

- There exists a parity-consistent path from the fault site to the affected observe point.

- If a failing test has more than one affected observe points, the fault must reside in the intersection of all the fan-in cones of all the affected observe points. This is based on the single-defect assumption, such that, for a failing test, only one defect is activated, and the corresponding faulty responses are observed.

- 2. Perform fault simulate for each fault in the initial candidate list to see if it perfectly explains any of the failing tests. If so, assign it a weight equaling to the number of tests it explains. Store the candidate fault with the greatest weight, and exclude the failing tests explained by it for consideration.

- 3. The procedure terminates when all the failing tests have been explained, or all the initial candidate faults have been examined. Rank the obtained candidate faults using their weights obtained in Step 2, and report the candidate fault list.

#### **1.2.2** Diagnosis for Multiple Defects

In order to collect additional information about the candidate faults obtained during diagnosis, failure isolation is typically performed through optical and electrical physical tools after the defect diagnosis. Physical failure analysis is the last step in this process to pinpoint the defects or the root causes of failures in the circuit, by taking a defect sample through a scanning electron microscope or transmission electron microscope. Typically, physical failure analysis is applied only if the number of candidate faults small enough, as the process of physical failure analysis is very time-consuming and expensive. However, large sets of candidate faults are typically obtained in the case where multiple defects are present in a circuit, which makes it impossible for physical failure analysis.

High defect densities are very common due to very fine geometries and lithography pushed to its limit with multi-patterning. While defect densities improve as the process matures, multiple defects are prevalent until the process yield reaches very high mature levels. The reason that the existence of multiple defects can cause large candidate fault sets is shown next.

The interactions among the defects that are present together in the circuit may result in an output response that is difficult for the defect diagnosis procedure to analyze. This occurs, for example, if the circuit contains multiple defects, and the interaction among them creates output responses that any single defect in the circuit cannot create alone. Considering a defect diagnosis procedure that is based on a fault model, even if the fault model used perfectly matches every defect in the circuit alone, the procedure may not be able to interpret the joint response of the defects to a particular test. This is illustrated in Table 1.1. In this case, two defects are present in the circuit, and they can be modeled by faults  $f_0$  and  $f_1$  respectively. Suppose that the output responses of  $f_0$  and  $f_1$  under test t are  $O_0$  and  $O_1$ , and the joint response of them is  $O_2$ . If there exists another fault  $f_2$  that can produce a output response  $O_2$  under test t, the defect diagnosis procedure will conclude that  $f_2$  is likely to be present in the circuit. When this happens multiple times during defect diagnosis, a large candidate fault list can be obtained.

| Candidate faults | Response under $t$ |

|------------------|--------------------|

| $f_0$            | $O_0$              |

| $f_1$            | $O_1$              |

| $f_0$ and $f_1$  | $O_2$              |

| $f_2$            | $O_2$              |

Table 1.1.: Multiple Defects Cause Large Candidate Fault Set

In order to address this issue, the procedures described in [17–19] consider to use reduced test sets for diagnosis, so as to allow the defect diagnosis procedure to compute a more accurate candidate fault set. As a result, the overall defect diagnosis quality can be improved.

#### 1.2.3 Contribution

The procedures from [17–19] reduce the number of candidate faults to a manageable number for physical failure analysis in cases where large candidate fault sets are obtained. However, they may lose the candidate faults that model the defects that are present in a faulty chip. This is inevitable with the defect diagnosis tool they use. In addition, they rely on the ability to modify the defect diagnosis tool, which is not possible for the usage of a commercial defect diagnosis tool.

As part of the work in this dissertation, we develop a new procedure that reduces the number of candidate faults obtained for multiple-defect diagnosis by ignoring certain tests. The main contribution of the new procedure is the following.

- The new procedure does not need to modify the defect diagnosis tool at source code level. This is appropriate when a commercial tool is used for defect diagnosis, and the source code is not available.

- The new procedure uses a partition of the candidate faults into subsets, so as to avoid losing the ones that match the defects present in the circuit. This feature is provided by commercial defect diagnosis tools. Avoiding losing the candidate faults matching the real defects is crucial when physical failure analysis is performed. It helps pinpoint more of the defects that are present in the circuit. It also helps avoid spending physical failure analysis effort on candidate faults that do not model any defects in the circuit.

#### 1.3 Systematic Defects Based on DFM guidelines

#### **1.3.1** Testing Systematic Defects Based on DFM Guidelines

The gap between the feature size and wavelength is increasing due to continuous shrinking of process technology. Due to the drawing of sub-wavelength feature sizes in lithography processes, deformities typically occur in the taped-out chips. As a result, for each smaller process technology node, the chips are increasingly impacted by deviations in manufactured patterns from the intended design. In particular, certain layout features are more difficult to manufacture than others, and are more likely to cause circuit failures. When such features are present multiple times in a chip, they can result in repeated or systematic defects, which can impact the yield and DPPM significantly [20–25]. Due to modeling errors and algorithmic inaccuracies in removing the resulting systematic variations, process-related corrective actions using OPC/RET techniques are not sufficient for acceptable yield and DPPM [26]. Thus, appropriate interventions on design side are inevitable so as to remedy the potential manufacturing issues and address the systematic defects.

Such design interventions are formulated as design rules and DFM guidelines. Design rules are mandatory, and must all be applied when designing the chip. DFM guidelines are typically taken as recommendations, and they are adhered to when possible to improve the quality of the design within the constraints of area, delay and power. When DFM guidelines are not adhered to, potential systematic defects may occur. The relationship between DFM guideline violations and potential systematic defects was discussed in [27–29]. In all these works, the layout sites where DFM guidelines are violated are first pinpointed. The affected transistors are then identified at the schematic level. The expected defect behaviors are translated into gate-level logic faults by using switch-level simulation. Test patterns are generated to target the resulting logic faults so as to avoid potential test holes.

Among the logic faults resulting from DFM guideline violations, there are undetectable faults. The clustering of undetectable faults related to DFM guideline violations in certain areas of the circuit can impact the coverage for the potential systematic defects in these areas. The missing tests may allow detectable defects in these areas to escape detection. This can impact the yield and DPPM significantly.

#### 1.3.2 Contribution

As part of the work in this dissertation, we first demonstrate that the undetectable faults caused by DFM guideline violations tend to cluster in areas of the circuit, resulting in circuit areas with low coverage for potential systematic defects. In order to improve the coverage of the circuit for potential systematic defects caused by DFM guideline violations, we propose two procedures based on logic and layout resynthesis respectively. The procedures are developed for cell-based designs. For this discussion we distinguish between faults that are internal to the standard cells (internal faults), and faults that are external to the standard cells (external faults).

First, we propose a procedure that is based on logic resynthesis followed by physical design process to eliminate undetectable internal faults. In this process of this procedure, the large clusters of undetectable faults related to DFM guideline violations are eliminated, and thus the coverage of the circuit for potential systematic defects is improved. Specifically, the procedure targets clusters of potential systematic defects related to DFM guidelines when the clusters may remain uncovered. It leaves other areas unaffected by logic resynthesis. This is important for allowing the design to be implemented in the constraints of delay, power and area.

The proposed logic resynthesis procedure is based on the fact that every time a gate, or an instance of a standard cell, is used in the circuit, it introduces the same internal faults caused by DFM guideline violations. The procedure eliminates the undetectable internal faults by resynthesizing the circuit with standard cells containing fewer internal faults. The procedure does not require to modify the cell library, but only uses different standard cells from the same cell library. The total number of undetectable internal and external faults is only allowed to decrease monotonically when applying the procedure. Hence, the increase in circuit coverage and the reduction in the number of undetectable faults related to DFM guideline violations are significant when undetectable internal faults are eliminated by logic resynthesis.

Next, we propose a layout resynthesis procedure that makes fine changes to the layout so as to improve the coverage of areas with low coverage because of the presence of undetectable external faults. The proposed layout resynthesis procedure eliminates undetectable external faults by fixing the DFM guideline violations that lead to them. The procedure prefers to eliminate faults whose effect on the circuit coverage is more significant. The DFM guideline violations are fixed by automatically changing the layout with the help of a place and route tool. The procedure maintains the same critical path delay, power consumption and die area when making changes to the layout.

The layout resynthesis method of the proposed procedure is not the main contribution of the proposed procedure. The contribution is using DFM guidelines to identify areas of the circuit with low coverage, and improving their coverage with the help of layout resynthesis. From a test point of view, we demonstrate which DFM guideline violations need to be fixed first so as to improve the coverage for potential systematic defects. As part of this solution, we suggest a layout-based coverage metric that can be used for identifying areas with low coverage.

Both two resynthesis procedures described above can be embedded into a standard cell based design flow as follows. In a cell based design flow, after the initial design, several iterations of incremental logic and physical design processes are typically required for satisfying the design constraints of delay, power and area. Both two procedures are iterative, and can thus fit within the overall iterative design process. In particular, an iteration of the design process can include one or more iterations of the proposed procedures to eliminate undetectable faults in poorly covered circuit areas, and improve the coverage for potential systematic defects in these areas. For a large chip, to maintain an acceptable computational effort, the proposed procedures can be applied to each logic block separately.

### 1.4 Organization

This dissertation is organized as follows. Chapter 2 describes the functional broadside test generation procedure to address the overtesting of delay faults. Chapter 3 describes the procedure to improve the quality of multiple defect diagnosis by removing and selecting tests. Chapter 4 and Chapter 5 describe the logic and layout resynthesis procedures for avoiding undetectable faults caused by DFM guideline violations respectively. The summary of this dissertation is shown in Chapter 6.

## 2. FUNCTIONAL BROADSIDE TEST GENERATION USING A COMMERCIAL ATPG TOOL

©2017 IEEE. Reprinted, with permission, from N. Wang, B. Yao, X. Lin and I. Pomeranz, "Functional Broadside Test Generation Using a Commercial ATPG Tool," in *Proceedings of the IEEE Computer Society Annual Symp. on VLSI*, Jul 2017. doi: 10.1109/ISVLSI.2017.61

Scan-based tests may lead to overtesting of delay faults by bringing a circuit to states that the circuit cannot enter during functional operation. Functional broadside tests address this issue by using reachable states as scan-in states. Different strategies for generating functional broadside tests have been studied and implemented by academic tools. The main challenge that these procedures address is the identification of reachable states that are useful as scan-in states. This chapter describes the generation of functional broadside tests using a commercial test generation tool. Our results demonstrate that it is possible to generate functional broadside tests without requiring any modifications to the commercial tool, and using the tests that the tool produces to obtain reachable states. This is expected to enable the generation of functional broadside tests for state-of-the-art designs that cannot be handled by academic tools. To demonstrate this point, we apply the procedure to two large logic blocks of the OpenSPARC T1 microprocessor.

#### 2.1 Introduction

The rapid decrease of geometry size and increase of clock frequency in ICs have lead to a growing of timing-related defects. These timing-related defects can generally be modeled by delay faults. One of the widely used delay fault models is the transition fault model.

Scan-based tests may cause overtesting of delay faults when the circuit is brought to states that cannot be reached during normal functional operation [4]. This can cause yield loss in the following ways. (1) Non-functional operation may lead to a higher switching activity, which will cause excessive current demands [5, 6]. These current demands may lead to voltage drops that slow down the circuit and cause a good circuit to fail. (2) Slow logic that can only be activated during non-functional operation may cause the circuit to appear slower [4]. Based on theses observations, detecting delay faults under functional operation conditions is necessary in order to avoid unnecessary yield loss.

Different strategies to address overtesting are described in [4–15]. To reduce the current demands, [5] and [6] describe solutions for generating scan-based tests with low switching activity. In [7] and [8], methods are proposed to avoid detecting functionally untestable faults. The methods in [12–14] apply functional constraints extracted from the circuit to avoid unreachable states. The tests generated by [12–14] are called pseudo-functional tests since the functional constraints may not avoid all the unreachable states. Pseudo-functional tests are also generated in [15]. These solutions do not guarantee functional operation conditions during the functional capture cycles where delay faults are detected, and therefore, do not guarantee that overtesting will be avoided.

The test sets in [9–11] create functional operation conditions during the functional capture cycles of a test by using reachable states as scan-in states. In [9] and [10], the methods target circuits that can be synchronized; while in [11], the method targets circuits with a hardware reset state. Two-cycle broadside tests are generated in [10] and [11]. The tests are referred to as functional broadside tests.

Functional constraints on primary input sequences exist when a circuit is embedded in a design. To simplify the generation of functional broadside tests, the test generation procedures typically assume that the primary input sequences are unconstrained during functional operation. We make the same simplifying assumption in this work.

With reachable scan-in states and unconstrained primary input vectors, the state transitions caused by a functional broadside test that is generated by the procedure from [10] or [11] can occur during functional operation. Delay faults detected by these tests can also be activated during functional operation, and the switching activity can occur during functional operation. Therefore, the tests avoid the unnecessary yield loss described before.

We denote a broadside test by  $\langle s_i, a_0, a_1 \rangle$ , where  $s_i$  is the scan-in state, and  $a_0$  and  $a_1$  are primary input vectors that are applied during two functional capture cycles. In a functional broadside test,  $s_i$  is a reachable state, and the state transitions from  $s_i$  under  $a_0$  and then  $a_1$  can be obtained during functional operation as well.

The procedures for generating functional broadside tests from [10, 11] are implemented using academic tools. The goal of this work is to show that it is possible to use a commercial tool for implementing the generation of functional broadside tests. In particular, a commercial tool is used for addressing the challenge of identifying reachable states that are useful as scan-in states efficiently. This will allow functional broadside tests to be generated for state-of-the-art circuits with features that are not handled by academic tools.

This chapter describes an implementation of a functional broadside test generation procedure that is based on the procedure presented in [11] using a commercial ATPG tool. The procedure is applied to two large logic blocks of the OpenSPARC T1 microprocessor to demonstrate its applicability to such designs.

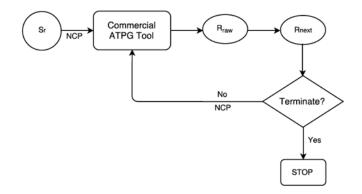

The test generation procedure described in this chapter starts from a single known reachable state denoted by  $s_r$ . For circuits with hardware reset,  $s_r$  is the reset state. For circuits that are synchronized by applying a synchronizing sequence,  $s_r$  is entered after applying the synchronizing sequence. Similar to the procedure in [11], we use the all-0 state as  $s_r$ . The test generation procedure is iterative. In every iteration, it uses a set of reachable states  $R_{\text{next}}$  as scan-in states for functional broadside tests. Initially,  $R_{\text{next}}$  contains only  $s_{\text{r}}$ . In an arbitrary iteration, the procedure uses the commercial tool to generate functional broadside tests with scan-in states from  $R_{\text{next}}$ . The scan-out states of the generated tests, which are also reachable states, are used for reconstructing  $R_{\text{next}}$  for the next iteration. Thus, the commercial tool is used for test generation as well as for identifying new reachable states.

The commercial tool can generate tests with several additional features that are also useful for functional broadside tests. We discuss these features next. In all the cases, we rely on the commercial tool to produce tests with the additional features.

The limitations of ATEs may require the input vectors applied during different functional capture cycles of a broadside test to be equal. The commercial tool can be applied with this constraint.

The studies in [30–32] have demonstrated that the number of clock cycles needed for test application, as well as the test data volume, can be reduced significantly with multi-cycle tests. This was shown for functional broadside tests in [32]. Multi-cycle tests were also used in [33]. We denote an *l*-cycle broadside test by  $\langle s_i, a_0, ..., a_{l-1} \rangle$ , where  $s_i$  is the scan-in state, and  $a_0, ..., a_{l-1}$  are primary input vectors that are applied during *l* consecutive functional capture cycles. It is possible to use the commercial tool for generating multi-cycle tests. The commercial tool is also used for fault simulation of multi-cycle tests.

We focus on the use of the commercial tool for the generation of multi-cycle functional broadside tests with unconstrained primary input vectors, for the following reasons. (1) Two-cycle tests are a special case of multi-cycle tests, and the procedure we develop can be used for generating two-cycle tests as a special case. (2) In addition to providing test compaction, the use of multi-cycle tests reduces the number of calls to the commercial tool during the iterative test generation procedure. This reduces the runtime. (3) Equal primary input vectors reduce the fault coverage achievable for benchmark circuits.

#### 2.2 Generation of Functional Broadside Tests

The test generation procedure from [11] iterates through a process where it generates functional broadside tests and identifies new reachable states. Fig. 2.1 presents the structure of the functional broadside test generation procedure. We implement the parts of the procedure around the commercial ATPG tool using TCL, Python, and C shell language. In addition, the commercial tool is used whenever fault simulation or logic simulation is needed.

Fig. 2.1.: Functional Broadside Test Generation Flowchart.

The procedure maintains a set of target faults that is denoted by  $\Phi$ . As tests are generated,  $\Phi$  is simulated with fault dropping. The procedure terminates when  $\Phi$  is empty, or when certain other termination conditions are satisfied.

In the following subsections of this section, we describe the details of this procedure. In subsection 2.2.1, we describe the details of test generation. In subsection 2.2.2, we describe the details of finding reachable states to construct  $R_{\text{next}}$ . In subsection 2.2.3, we describe the termination conditions. In subsection 2.2.4, we describe our strategy for generating multi-cycle tests.

#### 2.2.1 Test Generation

In this part, we describe the procedure for generating functional broadside tests using the commercial tool. Suppose that  $R_{\text{next}}$  contains *n* reachable states, denoted by  $s_0, s_1, ..., s_{n-1}$ . For every state  $s_i$  from  $R_{next}$ , the procedure needs to be able to call the commercial tool to generate functional broadside tests with scan-in state  $s_i$ .

There are two ways to specify a scan-in state for the commercial tool. The first is through ATPG constraints on the values of the state variables. This can be done using a command to specify the constrained values of the state variables before performing test generation. This approach turned out to be slow. In particular, it can only use one reachable state to generate functional broadside tests in each call. A significantly faster approach, which we used for our implementation, is to use what is called the Named Capture Procedure (NCP) [34].

NCP was originally introduced for explicitly defining the legal relationship between external and internal clock sequences, and controlling the complex clock-generator circuits. In this work, we use an NCP to define a scan-in state by specifying a scan-in value for every scan cell. In addition, we use NCP to specify the number of functional capture cycles in a test. We use multiple NCPs in each call to the commercial tool. This makes it possible to use several reachable states as scan-in states in each call.

The number of NCPs we use in a call to the commercial tool is denoted by m. The number of capture cycles is denoted by l, and it is the same in all the m NCPs. The selection of values for m and l is described later. For each call, we use the first m reachable states  $s_0, s_1, ..., s_{m-1}$  from  $R_{next}$  to define NCPs. If there exist fewer than m reachable states in  $R_{next}$ , we use all of them. With these m NCPs, the commercial tool generates l-cycle functional broadside tests to detect as many faults from  $\Phi$ as possible. The set of tests that is returned is denoted by  $\Psi_{cur}$ . We apply fault simulation with fault dropping of  $\Phi$  under  $\Psi_{cur}$ . We also add the tests to a test set denoted by  $\Psi$ . We then remove  $s_0, s_1, ..., s_{m-1}$  from  $R_{next}$ .

The test generation procedure described above is shown next.

#### **Procedure 2.1** Test Generation with $R_{\text{next}}$

- 1: Define *m* NCPs for the first *m* reachable states  $s_0, s_1, ..., s_{m-1}$  in  $R_{next}$ .

- 2: Use the commercial tool to generate functional broadside tests for the faults in  $\Phi$  with the NCPs defined in step 1. Collect the generated tests into  $\Psi_{cur}$ .

- 3: Run fault simulation of  $\Phi$  under  $\Psi_{cur}$ , and remove the detected faults from  $\Phi$ . Add  $\Psi_{cur}$  to  $\Psi$ .

- 4: Remove  $s_0, s_1, ..., s_{m-1}$  from  $R_{next}$ .

#### 2.2.2 Finding Reachable States and Constructing $R_{\text{next}}$

In this part, we describe the procedure we use to update the set of reachable states  $R_{\text{next}}$  for the next iteration.

Considering the tests that the commercial tool generates, the procedure collects the scan-out states, and places them in a set denoted by  $R_{\rm raw}$ . The scan-out state of a functional broadside test is a reachable state for the following reason. With a reachable scan-in state, the test takes the circuit through state-transitions that the circuit can make during functional operation. Therefore, the circuit visits reachable states during the test. This includes the final state, which is the scan-out state of the test. Although all the states that the circuit visits during a functional broadside test are reachable states, we only use the scan-out state because it is available after fault simulation, while extracting other states requires additional simulations. In addition, these states have no special features compared with the scan-out states. Therefore, using these states does not increase the fault coverage.

To avoid using the same reachable states in different iterations, the procedure maintains a set called  $R_{used}$  that includes all the reachable states that it has used. For the next iteration, the procedure includes in  $R_{next}$  every state from  $R_{raw}$  that is not included in  $R_{used}$ .

If  $R_{\text{next}}$  is empty, we need to find more reachable states using a different process. Different strategies for finding reachable states have been described in [9] and [11]. The strategy we use here is the following. For every state  $s_i$  in  $R_{next}$ , we apply a preselected number r of random input vectors  $v_0, v_1, ..., v_{r-1}$ . We simulate each pattern, denoted by  $\langle s_i, v_k \rangle$ , to find a nextstate, which is also reachable. The state is added to a set denoted by  $R_{sim}$ . The states in  $R_{sim}$  that are not included in  $R_{used}$  are added to  $R_{next}$ . If  $R_{next}$  is empty after using  $R_{sim}$ , we use the states in  $R_{sim}$  to generate additional reachable states using the same process with random primary input vectors. We only apply this process once again. It does not indicate all the reachable states have been visited if  $R_{next}$  is empty after applying this process. However, it is desirable to terminate this process after one iteration, in order to limit the runtime.

The procedure described above is shown next. The procedure stops when  $R_{\text{next}}$  is not empty to allow the test generation process to continue to the next iteration. The test generation process stops if  $R_{\text{next}}$  is empty after Procedure 2.2 terminates.

| Procedure | 2.2 | Finding | Reacha | able States | s and | Constructi | ng $R_{\text{next}}$ |

|-----------|-----|---------|--------|-------------|-------|------------|----------------------|

|-----------|-----|---------|--------|-------------|-------|------------|----------------------|

- 1: For each newly generated test in  $\Psi_{cur}$ , add its final state to  $R_{raw}$ .

- 2: For each state in  $R_{\text{raw}}$ , add it to  $R_{\text{next}}$  and  $R_{\text{used}}$  if it is not included in  $R_{\text{used}}$ .

- 3: If  $R_{\text{next}}$  is not empty, **stop**.

- 4: Simulate each state currently in  $R_{\text{raw}}$  with random input vectors  $v_0, v_1, ..., v_{r-1}$ and add the states into  $R_{\text{sim}}$ .

- 5: Add the states in  $R_{\text{sim}}$  that are not in  $R_{\text{used}}$  into  $R_{\text{next}}$  and  $R_{\text{used}}$ .

- 6: If  $R_{\text{next}}$  is not empty, **stop**.

- 7: Repeat steps 4, 5 and 6 with  $R_{\rm sim}$ .

- 8: **Stop**.

#### 2.2.3 Termination Conditions

The test generation procedure terminates if or  $R_{\text{next}}$  (after the application of Procedure 2.2) are empty. In addition, the procedure terminates when it appears that the fault coverage has saturated. This is measured as follows.

Suppose that after *i* iterations the fault coverage is  $fc_i$ . Suppose that after 2i iterations the fault coverage is still  $fc_i$ . This implies that doubling the number of iterations did not increase the fault coverage. In this case, the procedure terminates.

#### 2.2.4 Multi-cycle Test Generation

Experimental results show that the runtime of an iteration increases with the number of capture cycles of a functional broadside test. Therefore, it is important to avoid generating multi-cycle tests with large numbers of capture cycles when this is not necessary for test compaction. At the same time, using multi-cycle tests with more functional capture cycles increases the number of faults that the commercial tool can detect with every additional test, thus reducing the number of iterations. To balance these observations, we generate tests with decreasing numbers of functional capture cycles. The process is described by Procedure 2.3.

In Procedure 2.3, we use Procedure 2.1 to generate multi-cycle functional broadside tests, and Procedure 2.2 to find more reachable states and construct  $R_{\text{next}}$ . The pair (l, m) implies that we use m reachable states from  $R_{\text{next}}$  to generate l-cycle tests. The selection of values for l and m is based on experimental results that show the following. (1) Using l > 8 results in a high runtime, and we avoid it. (2) For l = 8it is important to limit the number of reachable states in order to limit the runtime. The lowest possible limit is m = 1 and we use this value. (3) After using l = 8, using l = 7 and 6 does not increase the fault coverage significantly enough to use these values. (4) Using l = 5, 4, 3 and 2 is important for increasing the fault coverage. It is important to continue limiting the number of reachable states in order to limit the runtime. Increasing m gradually to use m = 8, 16, 32 and 256 proved to be an effective choice. (5) Iterative calls to the commercial tool are cost-effective only with l = 2.

#### 2.3 Experimental Results

The procedure described in Section 2.2 is applied to ISCAS-89, ITC-99 and OpenCores<sup>®</sup> [35] benchmark circuits. To further demonstrate the capability and effectiveness of the procedure, it is also applied to two large blocks of the OpenSPARC

#### Procedure 2.3 Multi-cycle Test Generation

- 1: Assign  $R_{\text{next}} = \{s_r\}.$

- 2: for (l,m) = (8,1), (5,8), (4,16), (3,32) do

- 3: Call Procedure 2.1 to generate l-cycle tests with  $R_{\text{next}}$  and m.

- 4: Call Procedure 2.2 to update  $R_{\text{next}}$ .

- 5: if any termination condition is satisfied then

- 6: **stop.**

- 7: end if

- 8: end for

- 9: if no termination condition is satisfied then

- 10: Call Procedure 2.1 to generate 2-cycle tests with  $R_{\text{next}}$  and m = 256.

- 11: Call Procedure 2.2 to update  $R_{\text{next}}$ .

- 12: end if

T1 [36] microprocessor. OpenSPARC T1 is a 64-bit open-source microprocessor. It has eight cores and each core can support up to four threads for a total of thirty-two threads. Within OpenSPARC T1, we apply the proposed procedure to a single SPARC core (*sparc*) and the floating-point unit (*sparc-fpu*). We run the procedure on a Linux machine with 2.6GHz processors.

We experimented with different values of r, which is the number of random input vectors to apply during the simulation procedure for finding reachable states. Both the computational effort and the number of reachable states increase with r. We found experimentally that r = 256 balances the two parameters well.

For comparison, we use the commercial tool to generate a multi-cycle broadside test set without considering functional constraints. When multi-cycle tests are generated for the purpose of increasing the fault coverage, it is typical to supplement two-cycle tests with tests that have higher numbers of capture cycles. To match our functional broadside test set, we generate 2-, 3-, 4-, 5-, and 8-cycle tests, in this order. In every case, the commercial tool generates tests to detect as many faults as possible that were not detected with lower numbers of capture cycles. The resulting test set is denoted by  $\Psi_{nonfunc}$ .

We show the results in Table 2.1. In column G, we show the number of gates in the circuit. In column ff, we show the number of flip-flops in the circuit. In column

F, we show the number of transition faults. In column R, we show the number of reachable states the procedure used to generate tests. It should be noted that not all the reachable states lead to a contribution to the test set. In column *Tests*, we show the number of tests generated by the proposed procedure. We also show the number of multi-cycle tests in the non-functional broadside test set  $\Psi_{nonfunc}$  generated by the commercial tool. Next, we show the fault coverage achieved by the proposed procedure. This is followed by the fault coverage of  $\Psi_{nonfunc}$ . In the first column under *ATPG time*, we show the runtime of the commercial tool as part of the proposed test generation procedure. We then show the total runtime of the proposed test generation procedure. We also show the runtime for generating  $\Psi_{nonfunc}$  in the last column under *ATPG time* for comparison.

| Circuit    | G      | ff    | F      | R    | Te   | $\mathbf{sts}$ | Fault | Coverage    | A      | ГРG tim | e           |

|------------|--------|-------|--------|------|------|----------------|-------|-------------|--------|---------|-------------|

| Circuit    | G      | 11    | F      | п    | func | non<br>func    | func  | non<br>func | tool   | func    | non<br>func |

| b04        | 1176   | 66    | 2400   | 709  | 108  | 117            | 81.25 | 85.38       | 15s    | 38s     | 4s          |

| b10        | 332    | 17    | 746    | 42   | 41   | 53             | 84.58 | 86.73       | 2s     | 5s      | 6s          |

| b14        | 6780   | 215   | 21444  | 481  | 480  | 551            | 93.19 | 93.91       | 121s   | 137s    | 155s        |

| b20        | 14641  | 430   | 47986  | 2674 | 1473 | 904            | 92.7  | 94.46       | 906s   | 1020s   | 379s        |

| s1423      | 1169   | 74    | 2090   | 504  | 120  | 108            | 84.3  | 92.73       | 10s    | 31s     | 5s          |

| s5378      | 2535   | 163   | 4468   | 618  | 117  | 174            | 70.12 | 89.86       | 2s     | 16s     | 2s          |

| s35932     | 22909  | 1728  | 26456  | 635  | 113  | 70             | 96.31 | 97.18       | 25s    | 115s    | 9s          |

| s38584     | 18577  | 1164  | 34646  | 2973 | 1072 | 329            | 82.57 | 95.41       | 262s   | 545s    | 19s         |

| aes_core   | 23516  | 530   | 85118  | 472  | 471  | 599            | 99.94 | 99.95       | 368s   | 497s    | 55s         |

| des_perf   | 157078 | 8808  | 355028 | 6190 | 6195 | 202            | 100   | 100         | 12119s | 17542s  | 76s         |

| i2c        | 2047   | 128   | 3872   | 439  | 155  | 122            | 86.24 | 94.4        | 8s     | 20s     | 4s          |

| systemcaes | 13644  | 670   | 29306  | 1377 | 294  | 383            | 61.6  | 94.2        | 606s   | 696s    | 99s         |

| systemcdes | 4301   | 190   | 11182  | 684  | 83   | 164            | 98.33 | 99.82       | 28s    | 50s     | 5s          |

| spi        | 4763   | 229   | 11864  | 1039 | 938  | 965            | 98.68 | 99.29       | 174s   | 198s    | 20s         |

| usb_phy    | 1391   | 98    | 2010   | 353  | 52   | 75             | 32.95 | 92.9        | 1s     | 10s     | 2s          |

| wb_dma     | 8621   | 523   | 15258  | 193  | 192  | 212            | 71.21 | 98.94       | 3s     | 7s      | 5s          |

| sparc-fpu  | 87748  | 4431  | 333420 | 2599 | 1594 | 785            | 92.13 | 98.73       | 3324s  | 4329s   | 842s        |

| sparc      | 350468 | 17942 | 658844 | 4791 | 4678 | 1217           | 86.37 | 92.11       | 14453s | 19453s  | 8167s       |

Table 2.1.: Multi-cycle Functional Broadside Tests with Unconstrained Input

Vectors

From Table 2.1 it can be seen that the proposed procedure achieves a fault coverage that is typically close to the one achieved by non-functional broadside tests. The existence of functionally redundant logic in the circuits leads to functionally-undetectable faults that cannot be detected by functional broadside tests. These faults may be detectable by non-functional broadside tests, resulting in the fault coverage differences. The difference in fault coverage is larger when a circuit contains more functionally redundant logic. Differences between the fault coverages that can be achieved with functional and non-functional tests were also observed in [10] and explained by the existence of functionally-undetectable faults [37]. Close-to-functional tests can be used to reduce the occurrence of overtesting while increasing the fault coverage (or reducing the fault coverage difference). However, using close-to-functional tests does not guarantee that unreachable states will be avoided. In this chapter, we focus on functional broadside tests, in order to ensure that overtesting is avoided.

The need to satisfy functional constraints also causes the number of functional broadside tests to be higher than the number of non-functional tests for a similar fault coverage. With reachable states as scan-in states, fewer faults can be detected by each functional broadside test, and more tests are needed for detecting the same or similar number of faults.

The number of reachable states is typically larger than the number of tests. This is reasonable, since not all the reachable states contribute to the functional broadside test set.

The proposed multi-cycle functional broadside test generation procedure has a higher runtime than when non-functional broadside tests are generated. The proposed procedure needs to iteratively call the commercial tool to generate functional broadside tests, and it needs to compute reachable states. This increases the runtime. In addition, because of the simplicity of Python, we use it to implement the procedure for finding reachable states and constructing  $R_{\text{next}}$ . Running Python scripts increases the runtime. For complex logic blocks such as *sparc-fpu* and *sparc*, the runtime of the proposed procedure is around 5 and 2 times the runtime of the non-functional broadside test generation procedure, respectively. This demonstrates the feasibility and scalability of the proposed multi-cycle functional broadside test generation procedure. To further illustrate the benefits of using multi-cycle functional broadside tests, in Table 2.2, we present the results obtained when the procedure uses only the all-0 state as a scan-in state. We generate functional broadside tests with different numbers of capture cycles for comparison. The results are shown for b04, b14, s1423 and des\_perf. For each of the circuits and every number of capture cycles, we show the number of functional broadside tests, the fault coverage achieved by the tests, and the runtime.

| Circuit  |     | 2-cycle |      | 3-cycle |        |      |     | 5-cycle |      | 8-cycle |        |       |

|----------|-----|---------|------|---------|--------|------|-----|---------|------|---------|--------|-------|

| Circuit  | Т   | fc      | time | Т       | fc     | time | Т   | fc      | time | Т       | fc     | time  |

| b04      | 2   | 7.88%   | 1s   | 51      | 47.17% | 1s   | 95  | 69.33%  | 4s   | 96      | 78.71% | 10s   |

| b14      | 275 | 48.26%  | 2s   | 311     | 53.22% | 5s   | 622 | 90.49%  | 16s  | 364     | 91.18% | 35s   |

| s1423    | 27  | 32.97%  | 1s   | 46      | 53.01% | 2s   | 73  | 67.61%  | 5s   | 65      | 80.38% | 11s   |

| des_perf | 89  | 9.78%   | 65s  | 133     | 17.28% | 209s | 174 | 28.31%  | 954s | 89      | 39.53% | 5532s |

Table 2.2.: Fault Coverage Achieved with All-0 State

It can be seen that the fault coverage increases rapidly as the number of capture cycles increases. The comparison shows that generating multi-cycle functional broadside tests can reduce the need to find additional reachable states.

Next, we consider an additional parameter of the non-functional tests, the distance between the scan-in state and a reachable state. For functional broadside tests this distance is zero. For non-functional tests, a lower distance implies that the circuit operates closer to functional operation conditions. This is the basis for the generation of what are called partially-functional broadside tests. An accurate computation of the distances requires enumeration of all the reachable states, which is infeasible. We obtain a pessimistic estimate of these distances by using the set  $R_{used}$  of all the reachable states that were computed during the generation of functional broadside tests. Let S be the set of scan-in states of the non-functional broadside test set. For a state s in S, the minimum distance between s and a reachable state in  $R_{used}$ is denoted by d(s). For a circuit with k state variables, we include in a subset  $S_p$ every state s from S for which  $d(s) \leq p\% k$ . When p is small, the states in  $S_p$  have low distances from reachable states and thus maintain close-to-functional operation conditions.

Table 2.3 shows the percentage of tests included in  $S_{10}$ ,  $S_{20}$ ,  $S_{30}$  and  $S_{40}$ .

| Circuit    | $S_{10}$ | $S_{20}$ | $S_{30}$ | $S_{40}$ |

|------------|----------|----------|----------|----------|

| s38584     | 0        | 0        | 0        | 0        |

| systemcaes | 0        | 0        | 0        | 1.04     |

| usb_phy    | 0        | 0        | 0        | 10.67    |

| s5378      | 0        | 0        | 0        | 41.23    |

| wb_dma     | 0        | 0        | 3.21     | 5.33     |

| sparc      | 0        | 0        | 4.55     | 10.11    |

| des_perf   | 0        | 0.5      | 4.67     | 21.1     |

| fpu        | 0.07     | 0.22     | 5.11     | 15.81    |

| b20        | 0.39     | 1.3      | 7.1      | 27.55    |

| systemcdes | 1.67     | 5.21     | 7.99     | 59.31    |

| aes_core   | 2.11     | 5.13     | 10.11    | 71.11    |

| spi        | 2.44     | 3.56     | 7.33     | 51.71    |

| i2c        | 2.51     | 6.31     | 18.03    | 83.32    |

| b04        | 2.56     | 9.21     | 10.26    | 99.14    |

| s35932     | 3.11     | 3.11     | 7.97     | 29.99    |

| b14        | 4.31     | 5.77     | 12.11    | 98.55    |

| s1423      | 4.51     | 7.43     | 18.52    | 93.52    |

| b10        | 9.23     | 31.21    | 61.33    | 100      |

Table 2.3.: Hamming Distance

From Table 2.3 it can be seen that only small percentages of non-functional tests have a distance of 10% or lower from a reachable state in  $R_{used}$ . This is consistent with the observation made in [10] that non-functional tests rarely use reachable states accidentally. As p increases, the number of states in  $S_p$  increases. However, even with p = 30 or 40, only small percentages of states in S have  $d(s) \leq p\% k$ . This implies that non-functional tests do not create close-to-functional operation conditions accidentally.

# 3. IMPROVING THE RESOLUTION OF MULTIPLE DEFECT DIAGNOSIS BY REMOVING AND SELECTING TESTS

©2018 IEEE. Reprinted, with permission, from N. Wang, I. Pomeranz, B. Benware, M. E. Amyeen and S. Venkataraman, "Improving the Resolution of Multiple Defect Diagnosis by Removing and Selecting Tests," in *Proceedings of the Defect and Reliability Symp.*, Oct 2018. doi: 10.1109/DFT.2018.8602935

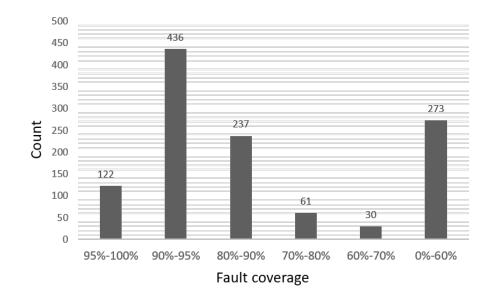

Earlier works showed that the resolution of defect diagnosis when multiple defects are present in a chip can be improved by instructing the defect diagnosis procedure to ignore certain tests. Specifically, these procedures reduce the number of candidate faults when the defect diagnosis procedure produces large numbers of candidates. Diagnosis with a large number of candidates poses challenges to failure isolation as optical emission and electrical probing physical tools need to eliminate a large number of candidates to isolate the defects. The procedures from the earlier works improved the diagnostic resolution by reducing the number of candidates at the cost of a reduced accuracy, or a reduced overlap between the candidates and the defects present in the faulty chip. In addition, they relied on the ability to modify the defect diagnosis tool. This chapter develops a procedure that improves the diagnostic resolution for multiple defects by ignoring certain tests without modifying the defect diagnosis tool. Moreover, the procedure uses a feature of commercial defect diagnosis tools to avoid losing accuracy. Experimental results for multiple defects indicate that reductions in the numbers of candidate faults are typically achieved without losing accuracy.

### 3.1 Introduction

A defect diagnosis procedure identifies the locations of the defects in a faulty chip using the faulty output response produced by the chip [38-57]. The output of a defect diagnosis procedure is a set of faults that is referred to as a candidate fault set. After obtaining a candidate fault set, failure isolation is performed through optical and electrical physical tools to obtain additional information about the candidates. Physical failure analysis is the last step in this process, taking a defect sample through a scanning electron microscope or transmission electron microscope. Physical failure analysis is applied only if the candidate fault set is small enough (such as 20 or fewer candidate faults). Large sets of candidate faults are obtained in the case where multiple defects are present in a chip. In modern process technologies, due to very fine geometries and lithography pushed to its limit with multi-patterning, high defect densities are very common. It takes a while for the process to reach a mature yield level. With high defect densities, multiple defects are common. While defect densities improve as the process matures, multiple defects are prevalent until the process yield reaches very high mature levels. The interactions between the defects that are present together in the circuit may result in an output response that is difficult for the defect diagnosis procedure to analyze. As a result, the procedure may yield a large set of candidate faults. If a candidate fault set is large, diagnostic tests may be added and used to reduce the number of faults in the candidate fault set. The additional tests are expected to improve the defect diagnosis results by providing more information.

However, the inclusion of a test in the test set used for diagnosis does not always improve the results of defect diagnosis. The observation that a defect diagnosis procedure does not require the output response obtained from the complete test set to produce accurate results is the basis for the approaches described in [58–60]. The need to ignore certain tests when computing the actual output response from a compacted output response is noted in [61]. The procedure in [17] goes further to show that certain tests reduce the resolution of diagnosis, and removing them from consideration is advantageous.

Improvements of the procedure from [17] are described in [18] and [19]. Similar to [17], the procedure from [18] is also based on the removal of tests from the test set used for diagnosis. In contrast, the procedure from [19] starts from an empty test set, and adds tests one by one such that the best diagnosis results will be obtained after the addition of every test. After selecting one test, the procedure typically produces a single candidate that matches one of the defects that exists in the circuit. As the number of tests is increased, the number of candidate faults increases, and more of the defects are identified correctly.

The procedures from [17–19] reduce the number of candidate faults to a manageable number in cases where the defect diagnosis procedure produces large sets of candidate faults, thus improving the diagnostic resolution. However, they may lose accuracy by identifying fewer of the defects that are present in a faulty chip. This is inevitable with the defect diagnosis tool they use. In addition, they rely on the ability to modify the defect diagnosis tool.

As part of the work in this dissertation, we develop a new procedure that improves the diagnostic resolution for multiple defects by ignoring certain tests. The main differences between the new procedure and the previous ones are the following. (1) The new procedure does not need to modify the defect diagnosis tool. This is appropriate when a commercial tool is used for defect diagnosis, and the source code is not available. (2) The new procedure uses a partition of the candidate faults into subsets, so as to avoid losing accuracy. This feature is provided by commercial defect diagnosis tools. When n defects are present in a faulty chip, the defect diagnosis tool is typically able to compute n subsets of candidate faults where each subset corresponds to one of the defects that is present in the faulty chip. By considering the subsets one by one, and ensuring that the same number of subsets is obtained after test removal, the procedure described in this chapter avoids losing candidates that match the defects. It thus rarely loses accuracy. A higher accuracy is crucial when

physical failure analysis is applied. It helps single out more of the defects that exist in the circuit. It also helps avoid spending physical failure analysis effort on candidate faults that do not correspond to any defects in the circuit.

Considering the issue of modifying the defect diagnosis tool, the procedures from [17–19] call the defect diagnosis procedure not only with reduced sets of tests, but also with reduced sets of faults from which candidates may be selected. After computing a basic set of candidate faults  $C_{\rm B}$  using the complete test set, these procedures do not require new candidate faults to be identified. As tests are removed or selected, the procedures compute new sets of candidate faults out of the faults in  $C_{\rm B}$ . This reduces the computational effort for additional calls to the defect diagnosis procedure. With the defect diagnosis tool used in this chapter, limiting the set of tests is possible without interfering with the tool, but limiting the set of faults requires the tool to be modified. We prefer to use the tool as a black box, and avoid interfering with its internal operation.

To address the computational effort, we develop a new algorithm that has two phases. The first phase is based on the removal of subsets of tests without omitting any candidate faults. The second phase is based on the selection of subsets of tests from the test set obtained in the first phase, so as to obtain smaller sets of candidate faults, and thus improve the resolution of defect diagnosis. In the first phase, most of the tests are removed from the initial test set to reduce the number of tests considered by the second phase. Experimental results show that the reduction in the computational effort of the second phase is higher than the additional computational effort required by the first phase. Consequently, the first phase improves the efficiency of the new algorithm significantly.

As in [17–19], considering fewer tests for defect diagnosis implies that the defect diagnosis procedure is given a subset of tests with their corresponding output responses. A new application of the test set to the faulty chip in order to obtain a new output response is not required.

The following example explains the reason why the diagnostic resolution can be potentially improved by ignoring certain tests, when multiple defects are present in a chip.

Considering a defect diagnosis tool that is based on a fault model, suppose that the fault model used by the tool can perfectly match every one of the defects that are present in the chip if they are present alone. However, the interactions between the defects under a particular test may result in an observed response that is different from the response of any one of the faults. The removal of such tests from consideration by the defect diagnosis tool improves the results of defect diagnosis. For example, suppose that two defects are present in a faulty chip, modeled by faults  $f_0$  and  $f_1$ . Considering a test t, suppose that the observed responses produced by  $f_0$  and  $f_1$  are  $z_0$ and  $z_1$ , respectively. Suppose that when  $f_0$  and  $f_1$  are present in the circuit together, the joint observed response produced is  $z_2$ . Other faults, such as  $f_2$ , in the fault model may produce  $z_2$  under test t individually. Therefore, the defect diagnosis tool would conclude that  $f_2$  might be present in the chip based on the observed response under test t. A more accurate candidate fault set can be computed by ignoring test t.

We denote the defect diagnosis tool by Diag(). The procedure described in this chapter first computes a basic candidate fault set, denoted by  $C_{\rm B}$ . This is accomplished by calling the defect diagnosis procedure Diag() with the complete test set, denoted by  $T_{\rm B}$ . Every additional candidate fault set that the procedure computes is intersected with  $C_{\rm B}$ . We do this because a small subset of  $T_{\rm B}$  does not provide sufficient information to produce accurate diagnosis results by itself [19]. Similar to [19], the procedure described in this chapter considers the candidate faults in  $C_{\rm B}$  as appropriate and sufficient, thus, it does not attempt to obtain new candidate faults that are not contained in  $C_{\rm B}$ . By taking intersections with  $C_{\rm B}$ , it only attempts to reduce the number of candidate faults in  $C_{\rm B}$  to improve the resolution of defect diagnosis. To define quality metrics for the results of defect diagnosis, we assume that the defects in the chip are best described by a subset of modeled faults  $f_{\text{in}}$ . Let C be candidate fault set obtained for  $f_{\text{in}}$ . The number of subsets of candidate faults in C is denoted by n. The overlap between C and  $f_{\text{in}}$  is denoted by  $OVLP = C \cap f_{\text{in}}$ . We define the following quality metrics.

- **Coverage**: The diagnosis coverage is defined as  $COV = |OVLP|/|f_{in}|$ . A higher coverage indicates that the defect diagnosis procedure singles out more of the defects correctly.

- **Precision**: The diagnosis precision is defined as PRC = |OVLP|/n. A higher precision is important when physical failure analysis is guided by the subsets of candidate faults. It helps avoid spending physical failure analysis effort on candidate faults that do not correspond to any defects in the circuit. The precision rarely reduces by keeping n unchanged.