# IN-MEMORY COMPUTING WITH CMOS AND EMERGING MEMORY

### TECHNOLOGIES

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Shubham Jain

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2019

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Anand Raghunathan, Chair

School of Electrical and Computer Engineering

Dr. Kaushik Roy

School of Electrical and Computer Engineering

Dr. Shreyas Sen

School of Electrical and Computer Engineering

Dr. Vijay Raghunathan

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

Head of the School Graduate Program

To my family for their unconditional love and support, and for always inspiring me to be better.

#### ACKNOWLEDGMENTS

First and foremost, I want to express my deepest gratitude to my advisor Prof. Anand Raghunathan for his invaluable teachings, guidance, and support throughout my PhD. Undoubtedly, over the years, his insightful suggestions, work ethics, and inspiration to pursue challenging problems have shaped me as a researcher. His immense energy for research and constant drive for problem-solving, deeply motivated me and enabled me in overcoming numerous challenges throughout my PhD. His strong emphasis on intuitive communication, polished research presentations, and high-quality writing helped me hone my non-technical skills. I thank him for being an outstanding mentor, critic, and advisor to me through the course of my PhD.

I want to thank Prof. Kaushik Roy, Prof. Shreyas Sen, Prof. Vijay Raghunathan, and Prof. Sumeet Gupta for their help, advice, and guidance throughout my PhD. Their insightful thoughts and suggestions helped me considerably in refining my research proposals and ideas. I also thank them for extremely fruitful discussions and brainstorming sessions, and for their availability and willingness to share their thoughts.

Next, I will like to thank the alumni and current members of Integrated Systems Laboratory – Swagath Venkataramani, Ashish Ranjan, Sanchari Sen, Younghoon Kim, Jacob Stevens, Vinod Ganesan, Shrihari Sridharan, Sourjya Roy, Reena Elangovan, Sarada Krithivasan, Manik Singhal and Abinand Nallathambi, for their help and friendship during my PhD. I truly enjoyed our conversations over a broad range of topics and in the process learned so much from each one of them. I will also like to thank my collaborators Sandeep Thirumula, Abhronil Sengupta, Leland Chang, Vijayalakshmi Srinivasan, and Jungwook Choi with whom I was able to explore a wide range of topics that enabled me to gain a more comprehensive research perspective. Lastly, I want to thank my parents, Tulika and Pradeep, for their unconditional love, support, motivation, and countless sacrifices. They are the true pillars of my aspirations. I want to thank my wife, Radhika, for her immense love, patience, and sacrifices. To my brother Ankit, my sister Devansi, my sister-in-law Bhawna, and my nephew Advit, I thank them for believing in me and being there for me. I solely dedicate the following pages of my dissertation to all of them for their love and support.

## TABLE OF CONTENTS

|    |       |          |                                                                        | Page |

|----|-------|----------|------------------------------------------------------------------------|------|

| LI | ST O  | F TAB    | LES                                                                    | . x  |

| LI | ST O  | F FIGU   | JRES                                                                   | . xi |

| A  | BSTR  | ACT      |                                                                        | . XV |

| 1  | Intro | oduction | 1                                                                      | . 1  |

|    | 1.1   | The P    | rocessor-Memory Bottleneck                                             | . 4  |

|    | 1.2   | Emerg    | ing Memories                                                           | . 5  |

|    | 1.3   | Thesis   | contributions                                                          | . 6  |

|    |       | 1.3.1    | Boolean Computing with Spin-Transfer Torque Magnetic RAM               | 6    |

|    |       | 1.3.2    | Non-Boolean Computing with resistive crossbars                         | . 7  |

|    |       | 1.3.3    | Non-Boolean Computing with CMOS-based memory cells                     | . 9  |

|    | 1.4   | Thesis   | outline                                                                | . 10 |

| 2  | Rela  | ted Wo   | rk                                                                     | . 11 |

|    | 2.1   | Near-n   | nemory Computing                                                       | . 11 |

|    | 2.2   | In-mer   | nory Computing                                                         | . 12 |

|    |       | 2.2.1    | General-purpose in-memory computing                                    | . 13 |

|    |       | 2.2.2    | Application-specific in-memory computing                               | . 13 |

|    |       | 2.2.3    | In-memory computing for Deep Neural Networks (DNNs)                    | . 13 |

|    |       | 2.2.4    | In-memory computing for DNN applications using CMOS-based memory cells | . 14 |

|    |       | 2.2.5    | In-memory computing for DNN applications using emerging memories       | . 15 |

|    | 2.3   | Thesis   | contributions                                                          | . 17 |

| 3  | Back  | ground   |                                                                        | . 20 |

|    | 3.1   | STT-N    | /RAM                                                                   | . 20 |

## Page

|   | 3.2         | Spintr                        | onic synaptic device                                       | 21 |

|---|-------------|-------------------------------|------------------------------------------------------------|----|

|   | 3.3         | 3.3 Resistive crossbar system |                                                            | 22 |

|   | 3.4         | Deep                          | Neural Network (DNN)                                       | 25 |

| 4 | Bool        | lean Co                       | mputing with Spin-Transfer Torque Magnetic RAM             | 26 |

|   | 4.1         | STT-N                         | MRAM based Compute-in-Memory (STT-CiM)                     | 28 |

|   |             | 4.1.1                         | STT-CiM overview                                           | 28 |

|   |             | 4.1.2                         | STT-CiM array                                              | 32 |

|   |             | 4.1.3                         | CiM operation under process-variations                     | 34 |

|   | 4.2         | STT-0                         | CiM Architecture                                           | 38 |

|   |             | 4.2.1                         | Optimizations for STT-CiM                                  | 39 |

|   |             | 4.2.2                         | Architectural Extensions for STT-CiM                       | 41 |

|   |             | 4.2.3                         | Data Mapping                                               | 42 |

|   | 4.3         | Exper                         | imental Methodology                                        | 45 |

|   | 4.4 Results |                               |                                                            |    |

|   |             | 4.4.1                         | Array-level analysis                                       | 48 |

|   |             | 4.4.2                         | Application-level memory energy                            | 50 |

|   |             | 4.4.3                         | System-level performance                                   | 52 |

|   | 4.5         | Summ                          | nary                                                       | 53 |

| 5 | Fran        | nework                        | for Evaluating Deep Neural Networks on Resistive Crossbars | 55 |

|   | 5.1         | Cross                         | oar Non-Idealities                                         | 57 |

|   |             | 5.1.1                         | Crossbar Non-idealities                                    | 57 |

|   |             | 5.1.2                         | Errors due to Non-Idealities                               | 60 |

|   | 5.2         | Cross                         | par Modeling                                               | 62 |

|   |             | 5.2.1                         | FCM Overview                                               | 63 |

|   |             | 5.2.2                         | Abstraction of interconnect non-idealities                 | 67 |

|   | 5.3         | RxNN                          | Framework                                                  | 72 |

|   | 5.4         | Exper                         | imental Methodology                                        | 74 |

|   | 5.5         | Result                        | 5S                                                         | 76 |

## Page

|   |      | 5.5.1   | FCM: Crossbar-level Evaluation                                           | 77  |

|---|------|---------|--------------------------------------------------------------------------|-----|

|   |      | 5.5.2   | RxNN: Application-Level Evaluation                                       | 78  |

|   |      | 5.5.3   | Sensitivity of accuracy to non-idealities                                | 81  |

|   |      | 5.5.4   | Impact of non-idealities: Insight                                        | 82  |

|   | 5.6  | Summ    | nary                                                                     | 83  |

| 6 |      |         | Software Compensation methods for Deep Neural Networks onrossbar Systems | 84  |

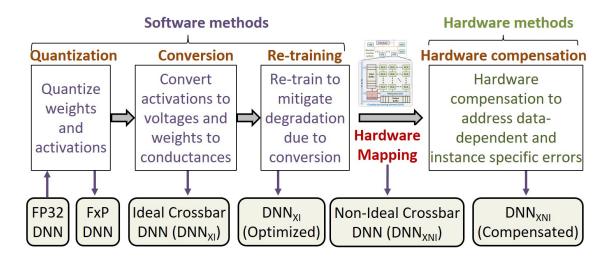

|   | 6.1  | CxDN    | N: Compensation methods for DNNs on resistive crossbars                  | 86  |

|   |      | 6.1.1   | CxDNN: Approach and Overview                                             | 86  |

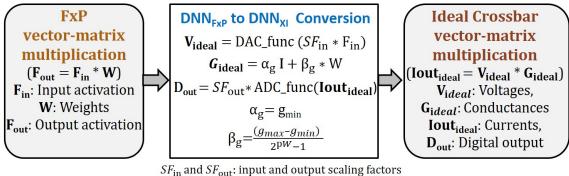

|   |      | 6.1.2   | Conversion algorithm                                                     | 88  |

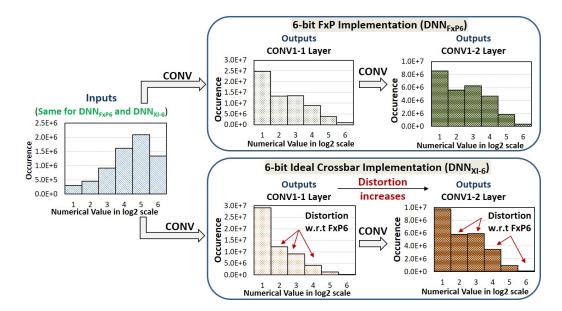

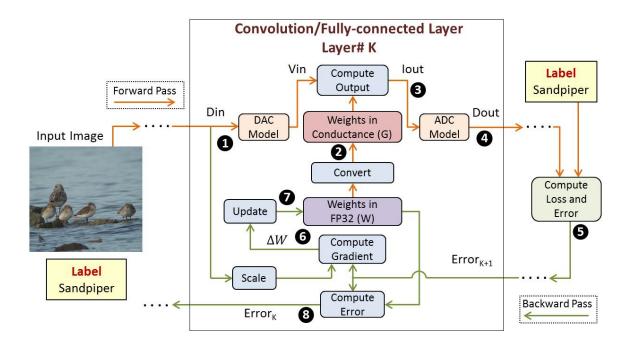

|   |      | 6.1.3   | Re-training method                                                       | 90  |

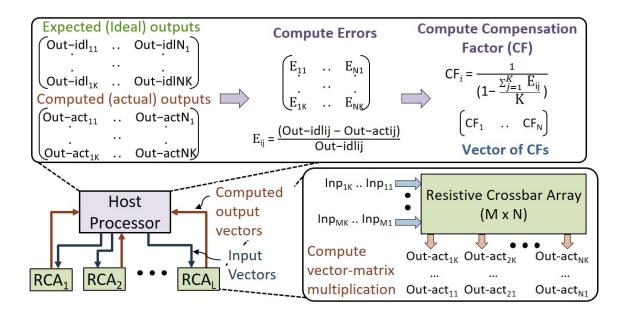

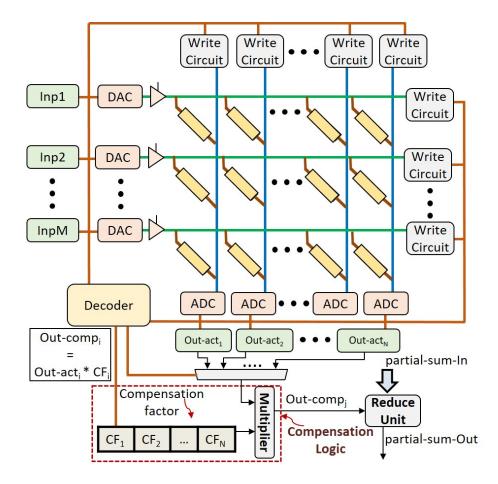

|   |      | 6.1.4   | Hardware compensation                                                    | 93  |

|   | 6.2  | Exper   | imental Methodology                                                      | 98  |

|   | 6.3  | Result  | ts                                                                       | 01  |

|   |      | 6.3.1   | Application-level compensation                                           | .01 |

|   |      | 6.3.2   | Compensating hardware-instance-specific errors 1                         | .04 |

|   |      | 6.3.3   | Re-training efficiency                                                   | .05 |

|   |      | 6.3.4   | Hardware compensation at the array-level                                 | .06 |

|   |      | 6.3.5   | Comparison with ECC scheme                                               | .07 |

|   |      | 6.3.6   | Area and Power breakdown                                                 | .08 |

|   | 6.4  | Summ    | nary                                                                     | .09 |

| 7 | Tern | ary in- | Memory accelerator for Deep Neural Networks                              | 10  |

|   | 7.1  | TiM-I   | ONN architecture                                                         | 13  |

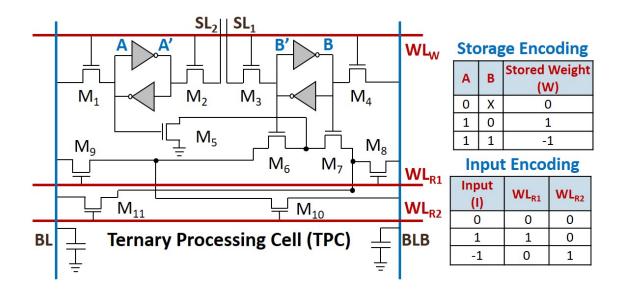

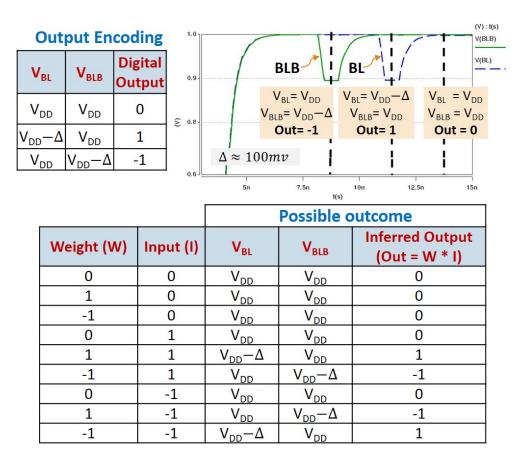

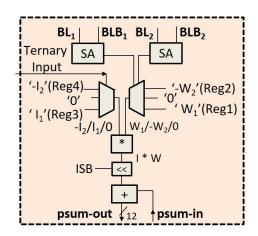

|   |      | 7.1.1   | Ternary Processing Cell (TPC)                                            | 13  |

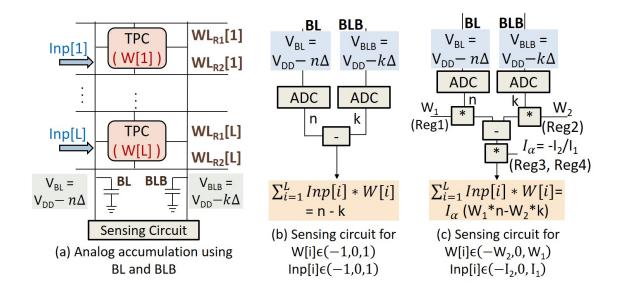

|   |      | 7.1.2   | Dot-product computation using TPCs                                       | 16  |

|   |      | 7.1.3   | TiM tile                                                                 | .18 |

|   |      | 7.1.4   | TiM-DNN accelerator architecture                                         | .21 |

|   | 7.2  | Exper   | imental Methodology                                                      | .23 |

|    |      |         |                                        | F | Page |

|----|------|---------|----------------------------------------|---|------|

|    | 7.3  | Result  | $\mathrm{ts}$                          | • | 127  |

|    |      | 7.3.1   | Comparison with prior DNN accelerators | • | 127  |

|    |      | 7.3.2   | Analysis of performance benefits       |   | 128  |

|    |      | 7.3.3   | Analysis of energy benefits            | • | 129  |

|    |      | 7.3.4   | Kernel-level benefits                  |   | 130  |

|    |      | 7.3.5   | TiM-DNN area breakdown                 |   | 131  |

|    |      | 7.3.6   | Impact of under process variations     |   | 132  |

|    | 7.4  | Summ    | nary                                   | • | 134  |

| 8  | Con  | clusion |                                        |   | 135  |

|    | 8.1  | Thesis  | 5 summary                              |   | 135  |

| RI | EFER | ENCE    | S                                      |   | 138  |

| VI | TA   |         |                                        |   | 153  |

## LIST OF TABLES

| Tab | le                                                                           | Page |

|-----|------------------------------------------------------------------------------|------|

| 2.1 | Examples of In-memory Computing for DNN applications                         | . 15 |

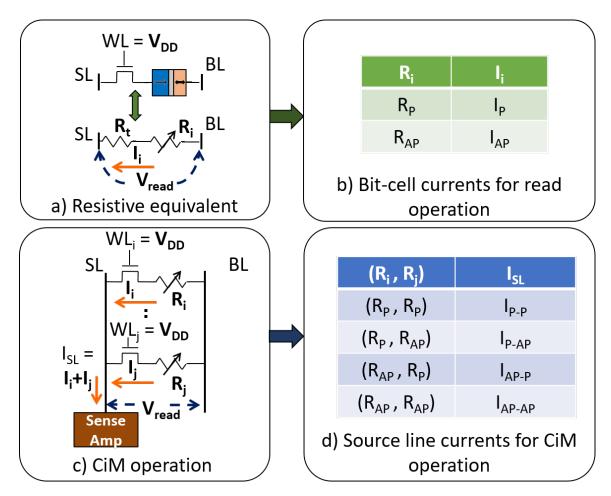

| 4.1 | Possible outputs of various sensing schemes in STT-CiM                       | . 31 |

| 4.2 | STT-CIM operations control signals                                           | . 34 |

| 4.3 | Examples of reduction operations                                             | . 40 |

| 4.4 | Device parameters for evaluating STT-CiM                                     | . 46 |

| 4.5 | Benchmark applications for evaluating STT-CiM                                | . 47 |

| 5.1 | Device and Technology parameters for evaluating RxNN $\ . \ . \ . \ .$       | . 75 |

| 5.2 | Benchmark DNN Applications                                                   | . 76 |

| 6.1 | Crossbar non-idealities modeled during evaluation of CxDNN $\ \ . \ . \ .$ . | . 99 |

| 6.2 | Device, circuit, and system parameters used for evaluating CxDNN $$          | 100  |

| 7.1 | TiM-DNN micro-architectural parameters                                       | 124  |

| 7.2 | DNN benchmarks for evaluating TiM-DNN $[153,154]$                            | 126  |

| 7.3 | Comparison of TiM-DNN with other DNN accelerators                            | 128  |

## LIST OF FIGURES

| Figu | re                                                                                                                                                                               | Pa | ge |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|

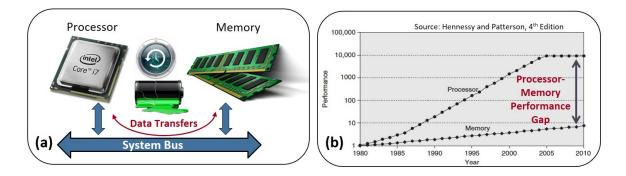

| 1.1  | Von Neumann computing Systems: (a) Separate processor and memory<br>subsystems lead to significant data transfers, (b) Processor-memory bot-                                     |    | 4  |

| 1.0  | tleneck [3]                                                                                                                                                                      |    |    |

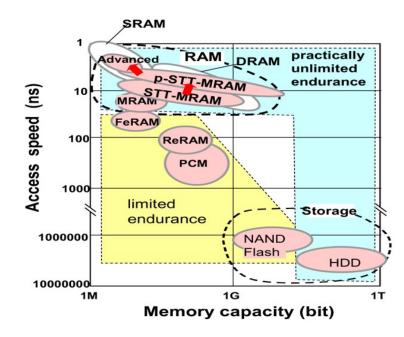

| 1.2  | Comparison of different memory technologies [34]                                                                                                                                 |    |    |

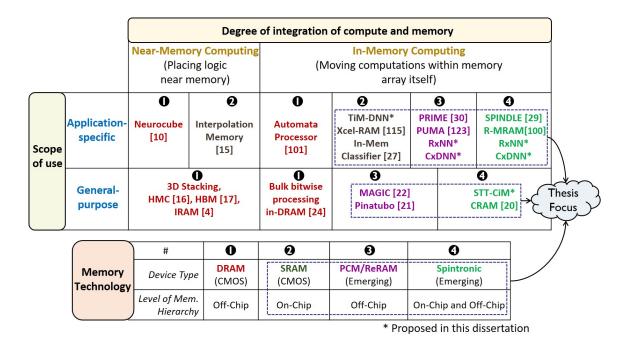

| 2.1  | Taxonomy of computing near/in memory                                                                                                                                             |    |    |

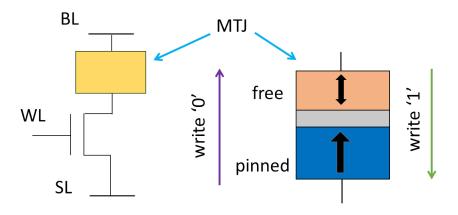

| 3.1  | STT-MRAM bit-cell                                                                                                                                                                | •  | 20 |

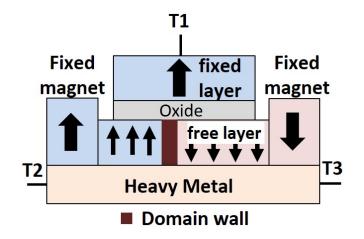

| 3.2  | Spintronic synaptic device                                                                                                                                                       | •  | 22 |

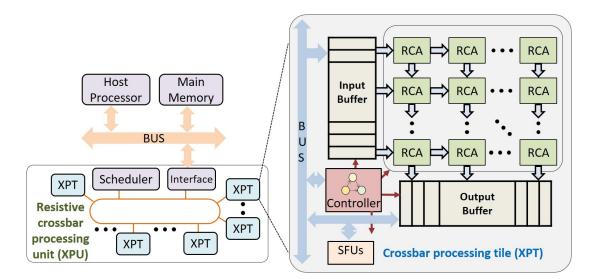

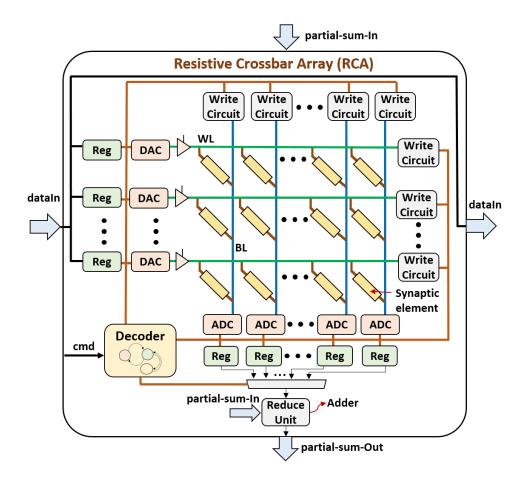

| 3.3  | Architecture for resistive crossbar system                                                                                                                                       |    | 23 |

| 3.4  | Resistive crossbar array                                                                                                                                                         |    | 24 |

| 4.1  | STT-CiM: Principle of operation                                                                                                                                                  |    | 29 |

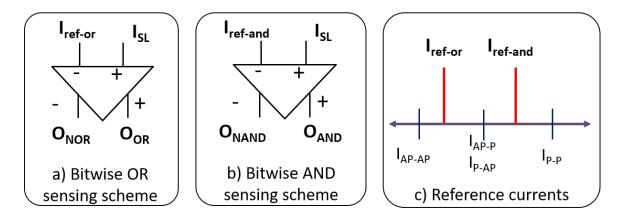

| 4.2  | STT-CiM sensing schemes                                                                                                                                                          | •  | 30 |

| 4.3  | In-Memory ADD operation using STT-CiM                                                                                                                                            | •  | 31 |

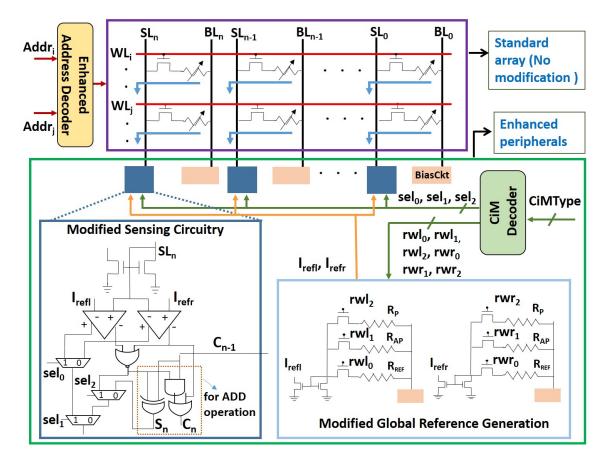

| 4.4  | STT-CiM array structure                                                                                                                                                          | •  | 32 |

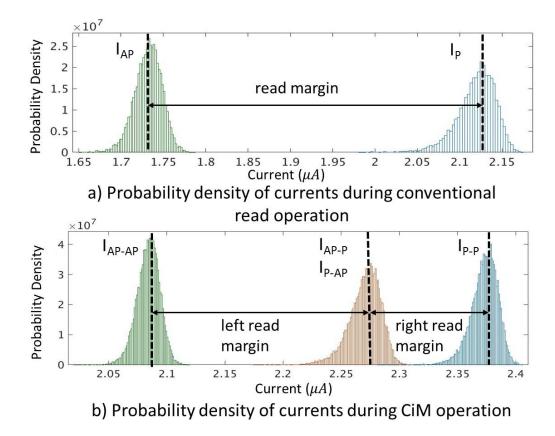

| 4.5  | Probability density distribution of $I_{SL}$ under process variations during read and CiM operations in STT-CiM $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | •  | 36 |

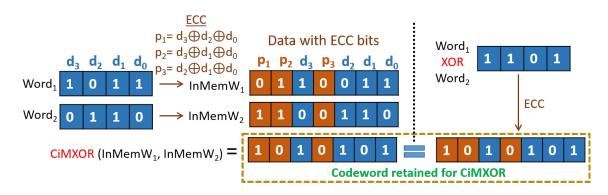

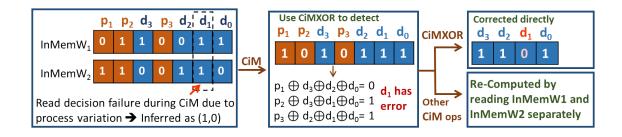

| 4.6  | Codeword retention property of CIM XOR                                                                                                                                           | •  | 37 |

| 4.7  | Error detection and correction for CiM operations in STT-CiM $\ . \ . \ .$ .                                                                                                     | •  | 37 |

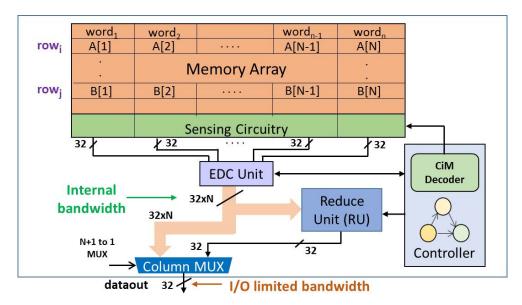

| 4.8  | STT-CiM supporting In-memory vector operation                                                                                                                                    | •  | 39 |

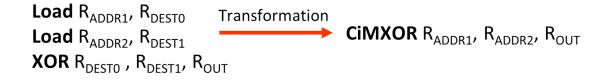

| 4.9  | Program transformation for CiMXOR                                                                                                                                                | •  | 42 |

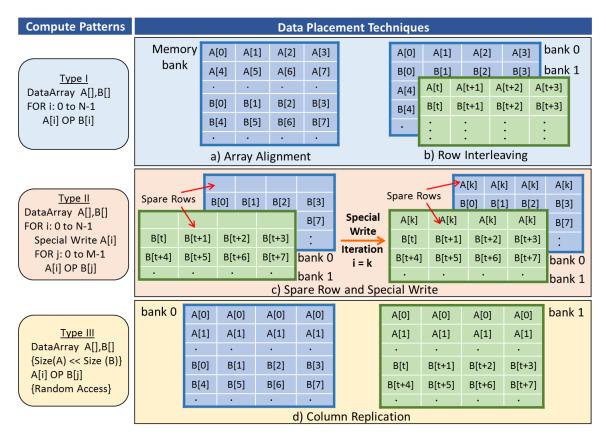

| 4.10 | Data mapping for various computation patterns                                                                                                                                    | •  | 44 |

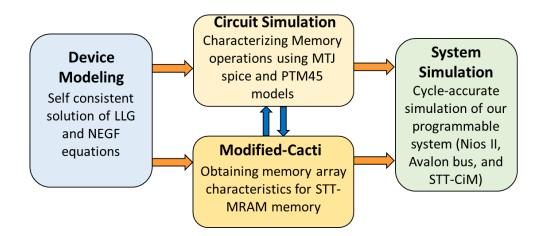

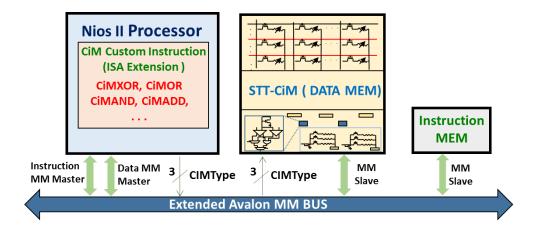

| 4.11 | STT-CiM device-to-architecture evaluation framework                                                                                                                              | •  | 45 |

| 4.12 | System level integration of STT-CiM                                                                                                                                              | •  | 45 |

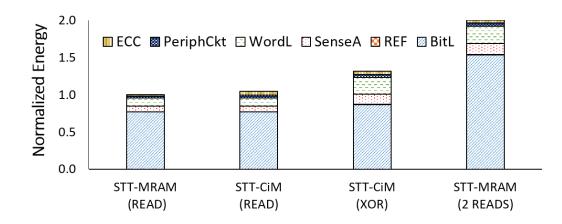

| 4.13 | Array-level energy evaluation of STT-CiM                                                                                                                                         | •  | 48 |

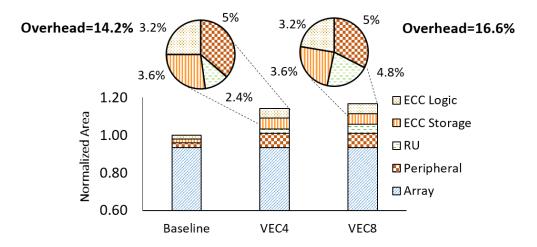

| 4.14 | Array-level area evaluation of STT-CiM                                                                                                                                           | •  | 49 |

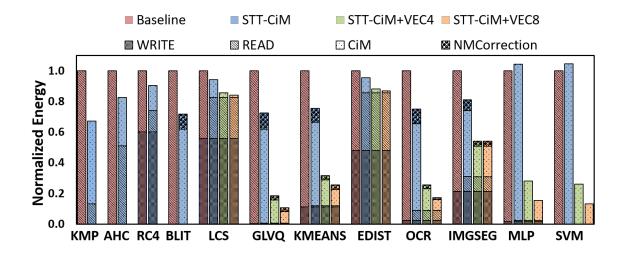

| 4.15 | Improvement in application-level memory energy using STT-CiM                                                                                                                     |    | 50 |

| Figu | re                                                                                                                                                                                                                                                                                      | Ра | age |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

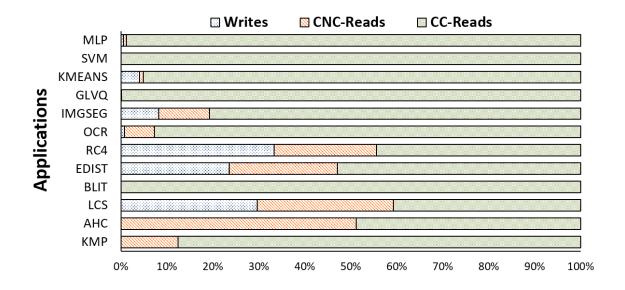

| 4.16 | Memory access breakdown of applications used in evaluation of STT-CiM                                                                                                                                                                                                                   |    | 51  |

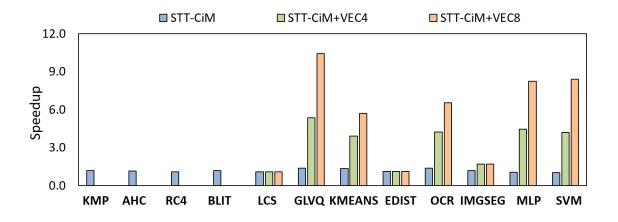

| 4.17 | Improvement in application-level system performance using STT-CiM                                                                                                                                                                                                                       |    | 52  |

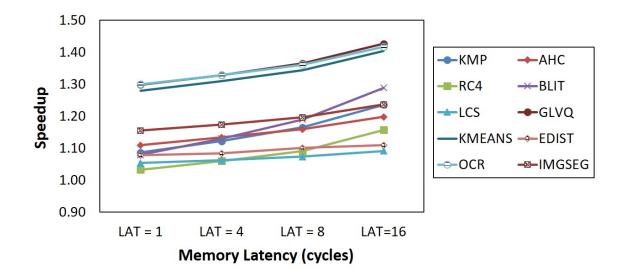

| 4.18 | STT-CiM performance sensitivity to memory latency                                                                                                                                                                                                                                       |    | 53  |

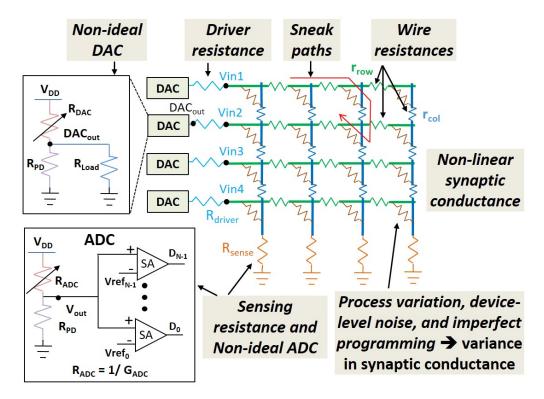

| 5.1  | Crossbar non-idealities overview                                                                                                                                                                                                                                                        |    | 58  |

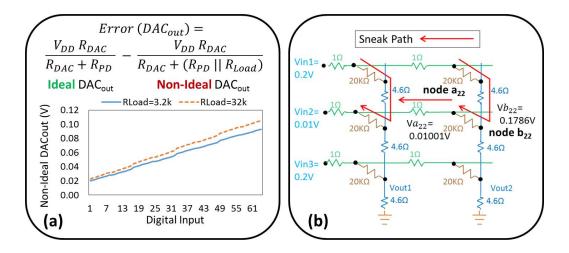

| 5.2  | Example of non-idealities in resistive crossbar: (a) Non-ideal DAC, (b) Sneak paths                                                                                                                                                                                                     |    | 59  |

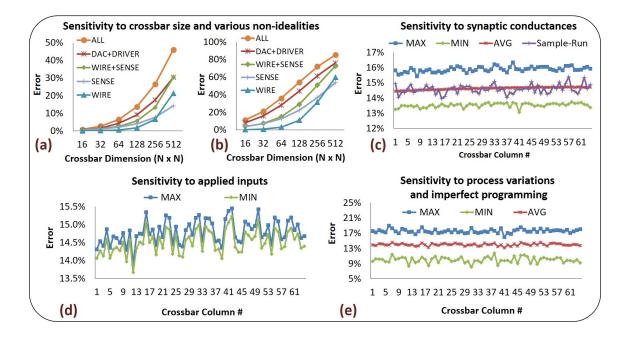

| 5.3  | Crossbar non-idealities: (a)-(b) Sensitivity to crossbar dimension with all synaptic conductances programmed to $G_{MIN}$ and $G_{MAX}$ , respectively, (c)-(d) Sensitivity to synaptic conductances and applied inputs, (e) Sensitivity to process variation and imperfect programming |    | 60  |

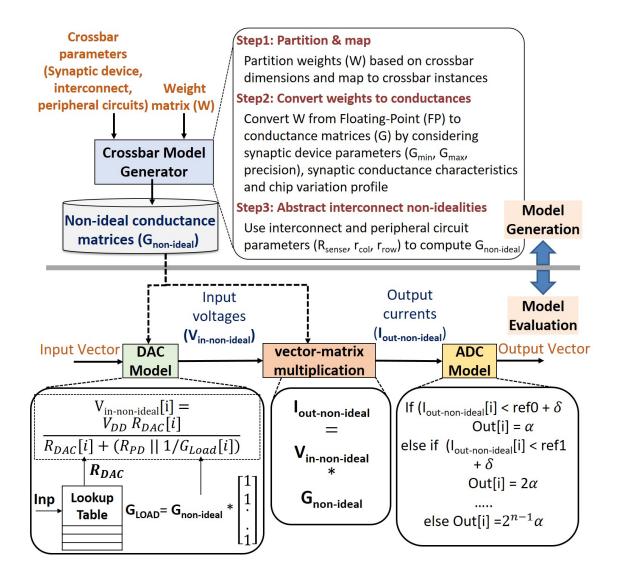

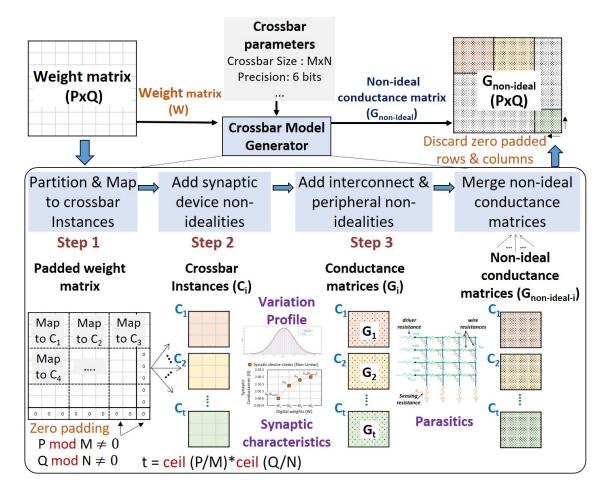

| 5.4  | FCM: Overview                                                                                                                                                                                                                                                                           |    | 63  |

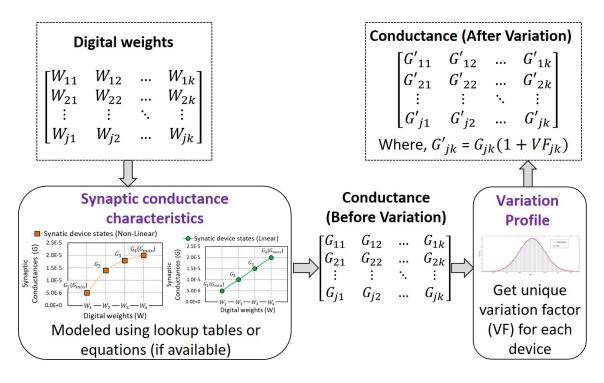

| 5.5  | Crossbar model generator: Details                                                                                                                                                                                                                                                       |    | 64  |

| 5.6  | Abstracting synaptic device non-idealities                                                                                                                                                                                                                                              |    | 65  |

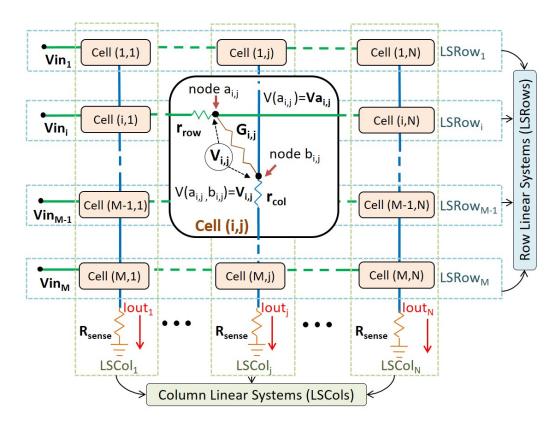

| 5.7  | Equivalent resistance circuit of MxN crossbar array                                                                                                                                                                                                                                     |    | 67  |

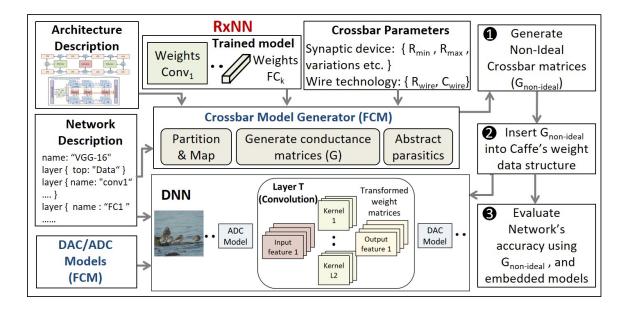

| 5.8  | RxNN Overview                                                                                                                                                                                                                                                                           |    | 73  |

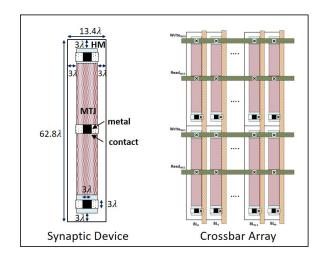

| 5.9  | Layout of synaptic device and crossbar array                                                                                                                                                                                                                                            |    | 76  |

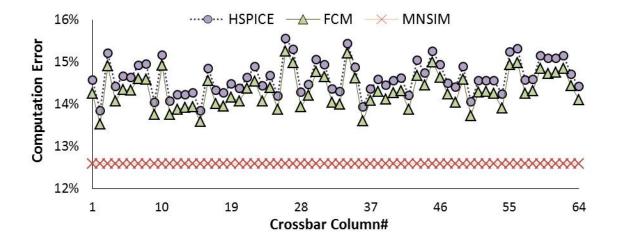

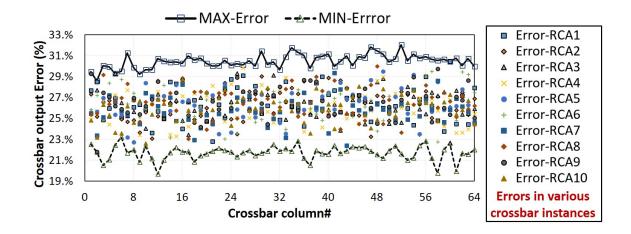

| 5.10 | Computation Errors observed in crossbar for various crossbar models $\ . \ .$                                                                                                                                                                                                           |    | 77  |

| 5.11 | FCM speedup over HPSICE                                                                                                                                                                                                                                                                 |    | 78  |

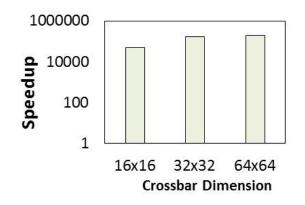

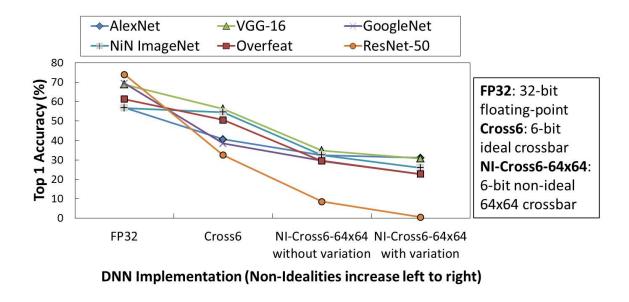

| 5.12 | Application-Level evaluation using RxNN                                                                                                                                                                                                                                                 |    | 79  |

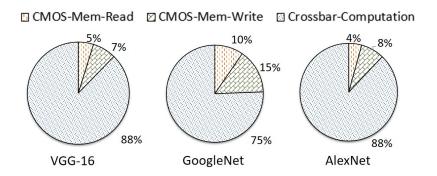

| 5.13 | Energy Breakdown for Cross64 implementation                                                                                                                                                                                                                                             |    | 80  |

| 5.14 | Accuracy's sensitivity to non-idealities                                                                                                                                                                                                                                                |    | 81  |

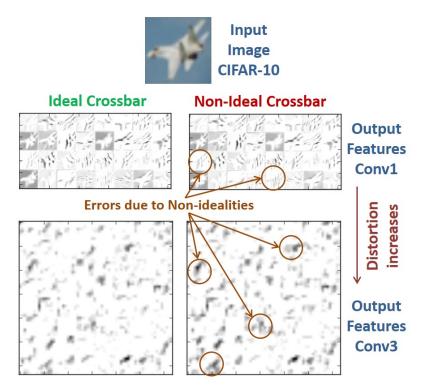

| 5.15 | Visual demonstration of errors using ConvNet                                                                                                                                                                                                                                            |    | 83  |

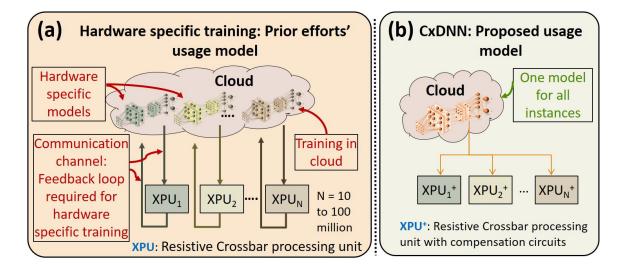

| 6.1  | CxDNN usage model                                                                                                                                                                                                                                                                       |    | 87  |

| 6.2  | CxDNN Overview                                                                                                                                                                                                                                                                          |    | 88  |

| 6.3  | FxP to ideal crossbar conversion function                                                                                                                                                                                                                                               |    | 90  |

| 6.4  | Activation distortion during conversion                                                                                                                                                                                                                                                 |    | 91  |

| 6.5  | Re-training method for DNNs on crossbar system $\ . \ . \ . \ . \ . \ .$                                                                                                                                                                                                                |    | 92  |

| 6.6  | Error characteristics across crossbar instances and columns $\ldots \ldots \ldots$                                                                                                                                                                                                      |    | 93  |

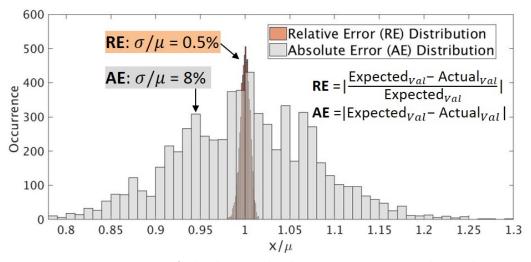

| 6.7  | Histogram of absolute and relative errors at crossbar columns $\ldots$ .                                                                                                                                                                                                                |    | 94  |

| Figu | Figure Page                                                                                                                                                                                                             |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 6.8  | CxDNN Hardware compensation: Calibration phase                                                                                                                                                                          |  |  |  |

| 6.9  | Hardware compensation logic of CxDNN                                                                                                                                                                                    |  |  |  |

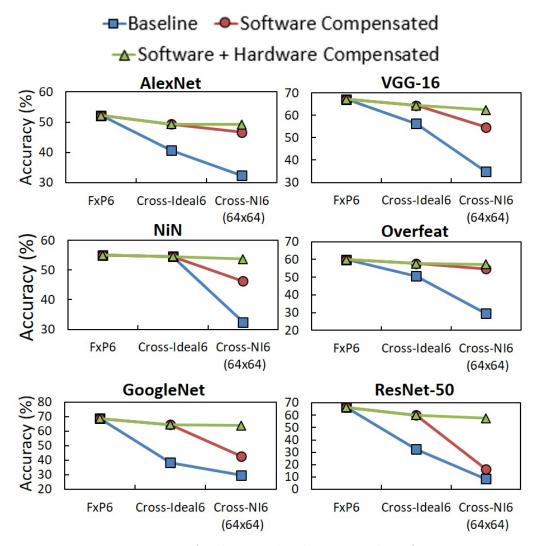

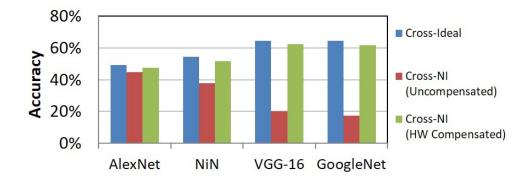

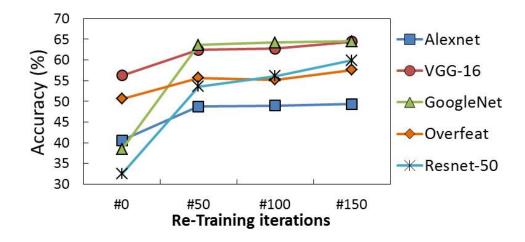

| 6.10 | Application level accuracy benefits 101                                                                                                                                                                                 |  |  |  |

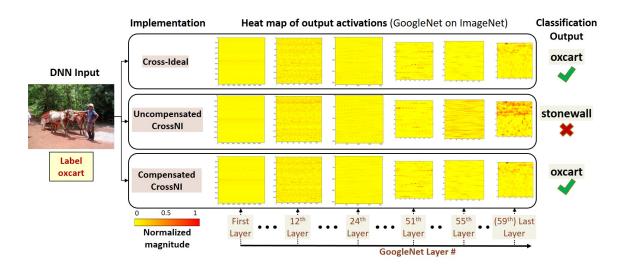

| 6.11 | Visual demonstration of HW error compensation 105                                                                                                                                                                       |  |  |  |

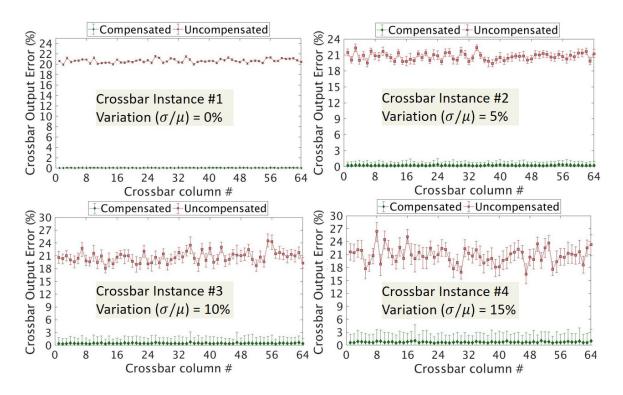

| 6.12 | HW compensation for instance specific errors 104                                                                                                                                                                        |  |  |  |

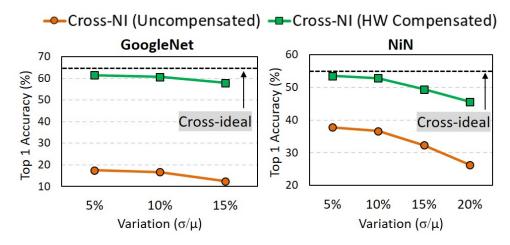

| 6.13 | HW compensation with increasing process variations 105                                                                                                                                                                  |  |  |  |

| 6.14 | Efficiency of the re-training method                                                                                                                                                                                    |  |  |  |

| 6.15 | Hardware compensation in action                                                                                                                                                                                         |  |  |  |

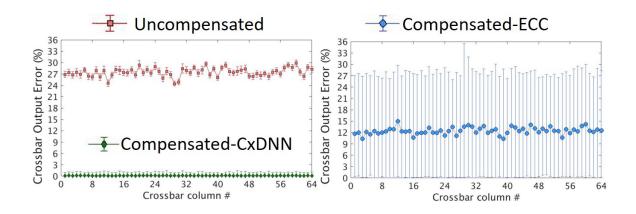

| 6.16 | Comparison of CxDNN and ECC scheme based compensation $[129]$ 107                                                                                                                                                       |  |  |  |

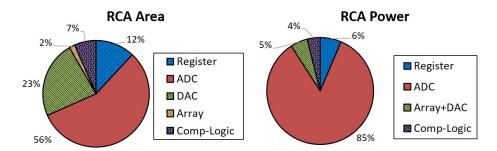

| 6.17 | Area and power breakdown of a crossbar array with compensation logic . $109$                                                                                                                                            |  |  |  |

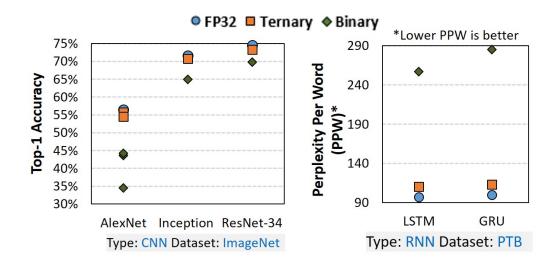

| 7.1  | Accuracy comparison of binary, ternary, and full-precision (FP32) DNNs [96, 104, 105, 145, 151–155]                                                                                                                     |  |  |  |

| 7.2  | Ternary Processing Cell (TPC) circuit and encoding scheme                                                                                                                                                               |  |  |  |

| 7.3  | Scalar multiplication using a TPC                                                                                                                                                                                       |  |  |  |

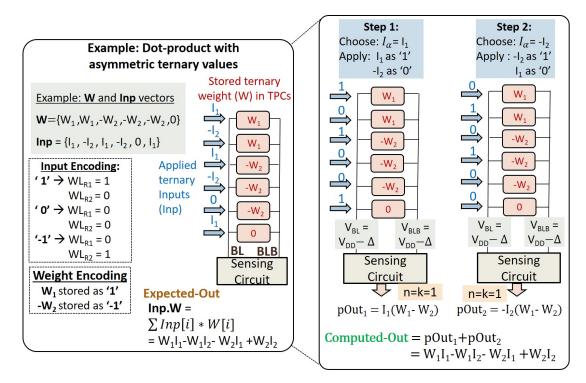

| 7.4  | Dot-product computation using TPCs: (a) Analog accumulation using BL<br>and BLB, (b) sensing circuit for unweighted (-1,0,1) ternary system, (c)<br>Sensing circuit for asymmetric weighted (-a,0,b) ternary system 116 |  |  |  |

| 7.5  | Example dot-product computation with asymmetric weighted ternary values                                                                                                                                                 |  |  |  |

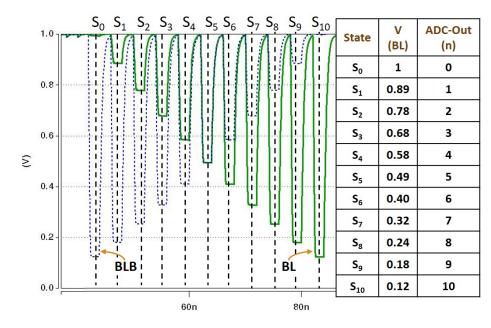

| 7.6  | Dot-product circuit simulation                                                                                                                                                                                          |  |  |  |

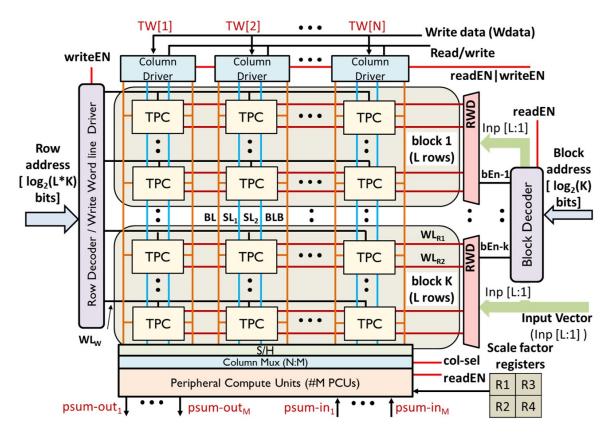

| 7.7  | Ternary in-Memory processing tile 120                                                                                                                                                                                   |  |  |  |

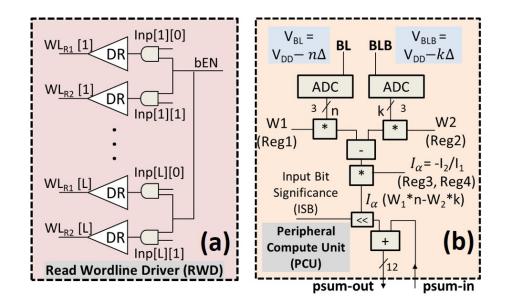

| 7.8  | (a) Read Wordline Driver (RWD), (b) Peripheral and Compute Unit (PCU)121                                                                                                                                                |  |  |  |

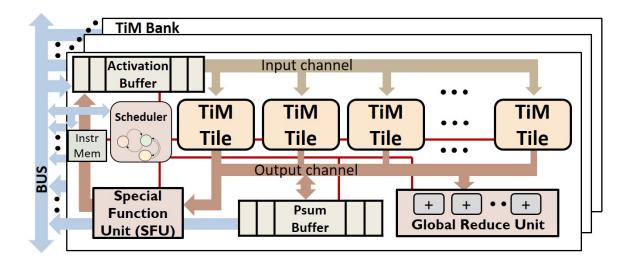

| 7.9  | TiM-DNN accelerator architecture                                                                                                                                                                                        |  |  |  |

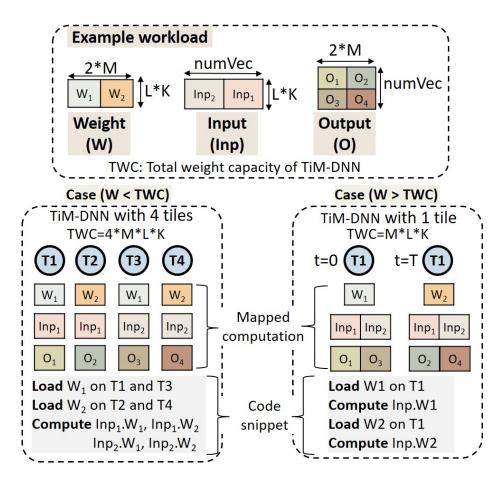

| 7.10 | TiM-DNN mapping: Example                                                                                                                                                                                                |  |  |  |

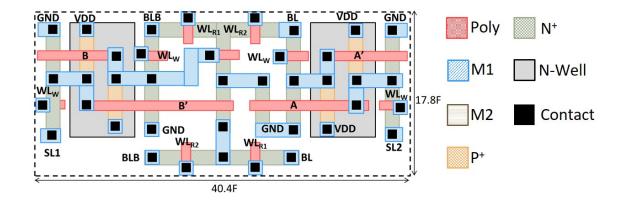

| 7.11 | Ternary Processing Cell (TPC) layout                                                                                                                                                                                    |  |  |  |

| 7.12 | Near-memory compute unit for the baseline design 125                                                                                                                                                                    |  |  |  |

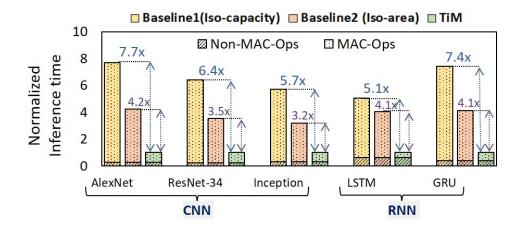

| 7.13 | Performance benefits of TiM-DNN 129                                                                                                                                                                                     |  |  |  |

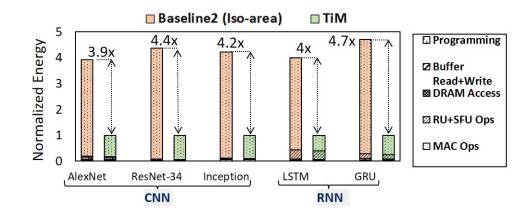

| 7.14 | Energy benefits of TiM-DNN 129                                                                                                                                                                                          |  |  |  |

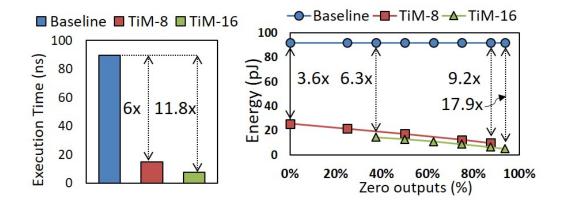

| 7.15 | Kernel-level benefits of TiM tile                                                                                                                                                                                       |  |  |  |

| Figure                                                           | Page                       |

|------------------------------------------------------------------|----------------------------|

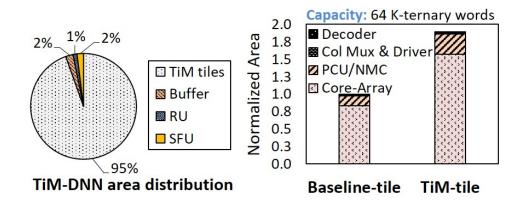

| 7.16 TiM-DNN area breakdown                                      | 131                        |

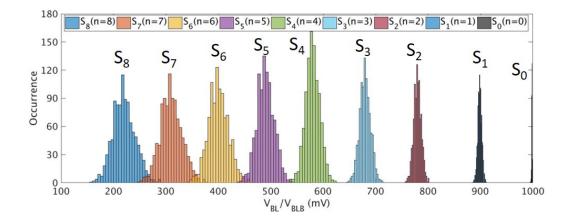

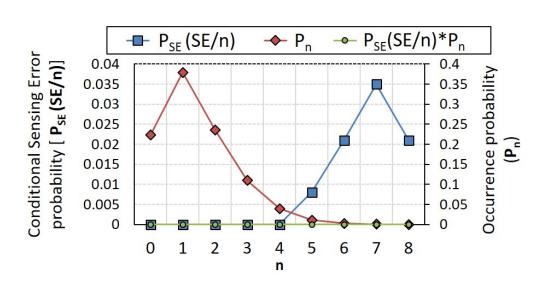

| 7.17 Histogram of the bit-line voltages $(V_{BL}/V_{BLB})$ under | r process variations . 132 |

| 7.18 Error probability during vector-matrix multiplication       | ns                         |

#### ABSTRACT

Jain, Shubham PhD, Purdue University, December 2019. In-Memory Computing with CMOS and Emerging Memory Technologies. Major Professor: Anand Raghunathan.

Modern computing workloads such as machine learning and data analytics perform simple computations on large amounts of data. Traditional von Neumann computing systems, which consist of separate processor and memory subsystems, are inefficient in realizing modern computing workloads due to frequent data transfers between these subsystems that incur significant time and energy costs. In-memory computing embeds computational capabilities within the memory subsystem to alleviate the fundamental processor-memory bottleneck, thereby achieving substantial system-level performance and energy benefits. In this dissertation, we explore a new generation of in-memory computing architectures that are enabled by emerging memory technologies and new CMOS-based memory cells. The proposed designs realize Boolean and non-Boolean computations natively within memory arrays.

For Boolean computing, we leverage the unique characteristics of emerging memories that allow multiple word lines within an array to be simultaneously enabled, opening up the possibility of directly sensing functions of the values stored in multiple rows using single access. We propose Spin-Transfer Torque Compute-in-Memory (STT-CiM), a design for in-memory computing with modifications to peripheral circuits that leverage this principle to perform logic, arithmetic, and complex vector operations. We address the challenge of reliable in-memory computing under process variations utilizing error detecting and correcting codes to control errors during CiM operations. We demonstrate how STT-CiM can be integrated within a generalpurpose computing system and propose architectural enhancements to processor instruction sets and on-chip buses for in-memory computing.

For non-Boolean computing, we explore crossbar arrays of resistive memory elements, which are known to compactly and efficiently realize a key primitive operation involved in machine learning algorithms, i.e., vector-matrix multiplication. We highlight a key challenge involved in this approach - the actual function computed by a resistive crossbar can deviate substantially from the desired vector-matrix multiplication operation due to a range of device and circuit level non-idealities. It is essential to evaluate the impact of the errors introduced by these non-idealities at the application level. There has been no study of the impact of non-idealities on the accuracy of large-scale workloads (e.g., Deep Neural Networks [DNNs] with millions of neurons and billions of synaptic connections), in part because existing device and circuit models are too slow to use in application-level evaluation. We propose a Fast Crossbar Model (FCM) to accurately capture the errors arising due to crossbar nonidealities while being four-to-five orders of magnitude faster than circuit simulation. We also develop RxNN, a software framework to evaluate DNN inference on resistive crossbar systems. Using RxNN, we evaluate a suite of large-scale DNNs developed for the ImageNet Challenge (ILSVRC). Our evaluations reveal that the errors due to resistive crossbar non-idealities can degrade the overall accuracy of DNNs considerably, motivating the need for compensation techniques. Subsequently, we propose CxDNN, a hardware-software methodology that enables the realization of large-scale DNNs on crossbar systems with minimal degradation in accuracy by compensating for errors due to non-idealities. CxDNN comprises of (i) an optimized mapping technique to convert floating-point weights and activations to crossbar conductances and input voltages, (ii) a fast re-training method to recover accuracy loss due to this conversion, and (iii) low-overhead compensation hardware to mitigate dynamic and hardware-instance-specific errors. Unlike previous efforts that are limited to small networks and require the training and deployment of hardware-instance-specific models, CxDNN presents a scalable compensation methodology that can address large DNNs (e.q., ResNet-50 on ImageNet), and enables a common model to be trained and de-

ployed on many devices.

xvi

For non-Boolean computing, we also propose TiM-DNN, a programmable hardware accelerator that is specifically designed to execute ternary DNNs. TiM-DNN supports various ternary representations including unweighted (-1,0,1), symmetric weighted (-a,0,a), and asymmetric weighted (-a,0,b) ternary systems. TiM-DNN is an in-memory accelerator designed using TiM tiles — specialized memory arrays that perform massively parallel signed vector-matrix multiplications on ternary values per access. TiM tiles are in turn composed of Ternary Processing Cells (TPCs), new CMOS-based memory cells that function as both ternary storage units and signed scalar multiplication units. We evaluate an implementation of TiM-DNN in 32nm technology using an architectural simulator calibrated with SPICE simulation and RTL synthesis. TiM-DNN achieves a peak performance of 114 TOPs/s, consumes 0.9W power, and occupies  $1.96mm^2$  chip area, representing a 300X improvement in TOPS/W compared to a state-of-the-art NVIDIA Tesla V100 GPU . In comparison to popular quantized DNN accelerators, TiM-DNN achieves 55.2X-240X and 160X-291Ximprovement in TOPS/W and TOPS/mm<sup>2</sup>, respectively.

In summary, the dissertation proposes new in-memory computing architectures as well as addresses the need for scalable modeling frameworks and compensation techniques for resistive crossbar based in-memory computing fabrics. Our evaluations show that in-memory computing architectures are promising for realizing modern machine learning and data analytics workloads, and can attain orders-of-magnitude improvement in system-level energy and performance over traditional von Neumann computing systems.

### 1. INTRODUCTION

In recent years, we have witnessed a surge in modern computing workloads such as data analytics, machine learning, bioinformatics, and graphics. In particular, machine learning workloads such as Deep Neural Networks (DNNs) have gained tremendous popularity due to their ability to achieve super-human accuracy in many cognitive tasks involving video, image, speech, and natural language processing. Consequently, they are being used in several real-world products and services for speech recognition (Apple Siri, Google Assistant, Amazon Alexa), image analysis (Google+ image search, Facebook DeepFace), natural language processing (Google Translate, Facebook DeepText), search engines, recommendation systems, and more [1, 2]. These workloads differ from traditional workloads in their computing characteristics, *i.e.*, they perform simple computations on large amounts of data leading to frequent data transfers and memory accesses. Von Neumann Computing systems with the separate processor and memory subsystems, such as multi-cores and GPUs, have been the mainstay of computing platforms for the past several decades. However, their performance and energy efficiency on data-intensive workloads are limited by the enormous amount of time and energy spent in frequent data transfers between these subsystems. Von Neumann systems also suffer from the known processor-memory data transfer bottlenecks [3], wherein the memory subsystem is much slower as compared to the processor.

The closer integration of compute and memory is a promising approach to alleviate the processor-memory bottleneck and reduce the frequent memory accesses enabling substantial improvement in system performance and energy. This idea has been explored at various levels of the storage hierarchy leading to numerous academic research efforts [4–15] as well as a few commercial solutions [16,17]. Prior efforts that have explored the closer integration of logic and memory are variedly referred to in the literature as logic-in-memory, computing-in-memory, and processing-in-memory. These efforts may be classified into two categories – moving logic closer to memory, or *near-memory computing* [4–17], and performing computations within memory structures, or *in-memory computing* [18–30]. In-memory computing reduces the number of memory accesses and the amount of data transferred between processor and memory, and exploits the wider internal bandwidth available within memory systems to achieve computing performance and efficiency beyond traditional Von Neumann systems. In this dissertation, we focus on in-memory computing using CMOS and emerging memory technologies to efficiently execute modern computing workloads.

Emerging memories technologies such as spintronic memories, Resistive RAM (ReRAM), and Phase Change Memory (PCM) are promising candidates for future memories due to several desirable attributes such as non-volatility, high density, and near-zero leakage. In particular, spintronic memories such as Spin Transfer Torque Magnetic RAM (STT-MRAM) have garnered significant interest with various prototype demonstrations and early commercial offerings |31-33|. In this dissertation, we explore three exemplary approaches to in-memory computing with emerging memories and a new CMOS-based memory cell that realize Boolean and non-Boolean computations within the memory array. In the first approach, we propose Spin-Transfer Torque Compute-in-Memory (STT-CiM), a design for in-memory computing with STT-MRAM. We exploit the resistive nature of STT-MRAM to realize a range of bit-wise, arithmetic, and vector compute-in-memory operations. We propose architectural enhancements to the processor instruction set and on-chip bus to integrate STT-CiM in larger systems. We also address the challenge of reliable in-memory computing by extending ECC schemes to detect and correct errors during CiM operations.

In the second approach, we explore crossbars with resistive memory elements to realize vector-matrix multiplications, *i.e.*, the primitive compute kernel in machine learning workloads. We highlight a key challenge with resistive crossbars, *i.e.*, the actual computed functions deviate from the desired vector-matrix multiplication operations due to numerous device and circuit-level non-idealities. The cumulative effect of all these non-idealities manifests as errors in the vector-matrix multiplications leading to accuracy degradation in DNNs. We address the need for a fast and accurate simulation framework to enable functional evaluation of large-scale DNNs on resistive crossbars. We propose a Fast Crossbar Model (FCM) to accurately capture the errors arising due to crossbar non-idealities while being four-to-five orders of magnitude faster than circuit simulation. We also develop RxNN, a software framework to evaluate DNN inference on resistive crossbar systems. Our evaluations reveal that the degradation in accuracy due to non-idealities can be significant for large-scale DNNs, motivating a need for cross-layer mitigation and compensation schemes to enable use of resistive crossbar based fabrics. Subsequently, we focus on error mitigation techniques for crossbars systems and propose CxDNN, a hardware-software methodology that enables the realization of large-scale DNNs on crossbar systems with minimal degradation in accuracy by compensating for errors due to non-idealities. CxDNN comprises of (i) an optimized mapping technique to convert floating-point weights and activations to crossbar conductances and input voltages, (ii) a fast re-training method to recover accuracy loss due to this conversion, and (iii) low-overhead compensation hardware to mitigate dynamic and hardware-instance-specific errors. CxDNN presents a scalable compensation methodology that can address large DNNs (e.g., ResNet-50 on ImageNet), and enables a common model to be trained and deployed on many devices.

Finally, in the third approach; we also explore in-memory computing using new CMOS-based memory cells. While emerging memories show considerable promise as future memories due to much higher density and lower leakage, CMOS-based memories are currently (and in near-future may continue to be) the backbone of memory design in computing platforms. We focus on realizing vector-matrix multiplication operations with signed ternary values and propose TiM-DNN, a programmable hard-ware accelerator that is specifically designed to execute state-of-the-art ternary DNNs. TiM-DNN supports various ternary representations including unweighted (-1,0,1),

symmetric weighted (-a,0,a), and asymmetric weighted (-a,0,b) ternary systems, enabling it to execute a broad range of ternary DNNs.

In the following sections, we first present the limitations of traditional Von Neumann computing systems and motivate emerging memory technologies. Next, we provide a brief description of the thesis contribution and the thesis outline.

#### 1.1 The Processor-Memory Bottleneck

In traditional Von Neumann computing systems, the processing and memory units are separate subsystems connected via a system bus or Network-on-Chip (NoC) as shown in Figure 1.1(a). These systems have been the backbone for computing platforms for the past several decades and will continue to be so. However, they are not very efficient in realizing several modern computing workloads such as data analytics and machine learning that perform simple computations on large amounts of data. Realizing these workloads on Von Neumann systems lead to frequent data transfers between the processor and memory subsystem [Figure 1.1(a)], thereby consuming a significant fraction of the overall system energy and time. We can consider the energy and time spent during data transfers undesirable as no useful computations are performed.

Fig. 1.1.: Von Neumann computing Systems: (a) Separate processor and memory subsystems lead to significant data transfers, (b) Processor-memory bottleneck [3].

Processor-memory gap, *i.e.*, the performance gap between the processor and memory, as shown in Figure 1.1(b) is another source of inefficiency in Von Neumann systems. Modern workloads lead to enormous amounts of slow memory access and perform very simple and little computations on the fetched data, thereby leading to processor-memory bottlenecks that degrade the overall system performance.

#### 1.2 Emerging Memories

The growth in data processed and the increase in the number of cores place high demands on the memory systems of modern computing platforms. Consequently, a growing fraction of transistors, area, and power are utilized towards memories. CMOS memories (SRAM and embedded DRAM) have been the mainstays of memory design for the past several decades. However, recent technology scaling challenges in CMOS memories, along with an increased demand for memory capacity and performance, have fueled an active interest in alternative memory technologies.

Several alternative non-volatile memory (NVM) technologies such as spintronic memory, Phase Change Memory (PCM), and Resistive RAM (ReRAM) have emerged as potential candidates for future memories due to several highly desirable characteristics, *viz.*, high density, ultra-low leakage energy, and non-volatility. Figure 1.2 shows the comparison of different emerging and CMOS memory technologies using access speed, memory capacity, and endurance. ReRAM and PCM offer memory capacity in G-bit range with an access speed of 100-1000ns, thereby limiting them to be an alternative for only off-chip memories. In contrast, spintronic memories such as STT-MRAM and p-STT-MRAM (shown in Figure 1.2) offer both high access speeds (1 ns to 10 ns) and capacity (1 M-bits to 10 G-bits), enabling them to be used as both on-chip and off-chip memories. Moreover, unlike PCM and ReRAM, spintronic memories have practically unlimited endurance adding to their bid for being the next generation memory technology.

Fig. 1.2.: Comparison of different memory technologies [34].

#### **1.3** Thesis contributions

In this section, we detail the contributions of this dissertation wherein we explore three exemplary approaches to in-memory computing, viz., boolean computing with Spin-Transfer Torque Magnetic RAM, non-boolean computing with resistive crossbars, and non-boolean computing with novel CMOS memory cells.

#### 1.3.1 Boolean Computing with Spin-Transfer Torque Magnetic RAM

Spintronic memories use electron spin as the state variable to represent logic, as opposed to SRAMs and DRAMs that use charge. There are two spin states -Up and Down - enabling 1-bit of storage. Spin Transfer Torque Magnetic RAM (STT-MRAM) is currently the most popular spintronic memory with commercial chips [31–33] already available in the market. In recent years, there have been several research efforts to boost the efficiency of STT-MRAM at the device, circuit, and architectural levels [35–61]. In this dissertation, we explore in-memory computing

with STT-MRAM motivated by the observation that the movement of data from bitcells in the memory to the processor and back (across the bit-lines, memory interface, and system interconnect) is a major performance and energy bottleneck in computing systems. By exploiting the ability to simultaneously enable multiple wordlines within a memory array, we enhance STT-MRAM arrays to perform a range of arithmetic, logic and vector operations. We propose circuit and architectural techniques for reliable in-memory computing under process variations and for enabling the proposed design to be used in a programmable processor-based system. We also address the question of how should STT-CiM be integrated into a general-purpose computing system. To this end, we propose architectural enhancements to processor instruction sets and on-chip buses to enable utilization of STT-CiM as a scratchpad memory. Finally, we present data mapping techniques to increase the effectiveness of STT-CiM. We evaluate STT-CiM using a device-to-architecture modeling framework and integrate cycle-accurate models of STT-CiM with a commercial processor and onchip bus (Nios II and Avalon from Intel). Our system-level evaluation shows that STT-CiM provides system-level performance improvements of 3.93x on average (upto 10.4x), and concurrently reduces memory system energy by 3.83x on average (upto 12.4x).

#### 1.3.2 Non-Boolean Computing with resistive crossbars

Resistive crossbar based in-memory computing systems have garnered significant interest for realizing DNNs due to their ability to perform the underlying computational kernel, *viz.*, vector-matrix multiplications, efficiently. They may be designed using any of the above mentioned emerging resistive memory devices, including ReRAM, PCM, and Spintronics [62–65]. These devices offer the prospect of highly compact and energy-efficient DNN implementations due to their intrinsic properties. Several research efforts have explored the design of crossbar based systems at the device, circuit, architecture, and algorithmic levels [28–30, 63, 66–86]. A key challenge with resistive crossbars is that the computed function (input voltages multiplied with the weights stored as conductances to obtain output currents) is only an approximation of the desired vector-matrix multiplication. In practice, resistive crossbars suffer from various device and circuit level non-idealities, *viz.*, driver resistance, sensing resistance, sneak paths, interconnect parasitics, process and programming variations, and non-linearities in the peripheral circuits such as ADCs and DACs, which lead to errors in the computed vector-matrix multiplications. These errors can degrade the overall application-level accuracy of a DNN realized on a resistive crossbar system. Although DNNs are resilient to some inaccuracy in their computations [87–90], this resilience is not unlimited. Therefore, it is necessary to evaluate the impact of non-idealities present in imperfect computational fabrics such as resistive crossbars.

In this dissertation, we first evaluate the impact of non-idealities in resistive crossbars to characterize errors due to these non-idealities. We show that the errors show significant data-dependence, *i.e.*, they depend on the weight programmed into, and input applied to, the crossbar, and hardware-instance dependence (due to variations), motivating the need for a detailed crossbar model. Next, we propose a Fast Crossbar Model (FCM) that can accurately capture the impact of crossbar non-idealities. FCM abstracts non-idealities using simple linear algebra operations to achieve orders-of-magnitude faster simulation compared to SPICE. We realize FCM using the well-known BLAS (Basic Linear Algebra Subprograms) library and develop RxNN, a software framework to evaluate DNNs realized on resistive crossbar systems. We use RxNN (which is based on the popular Caffe [91] deep learning framework) to evaluate several large-scale DNNs with millions of neurons and billions of synaptic connections. Our evaluation shows that the accuracy degradation due to crossbar non-idealities can be significant, motivating a need for cross layer error mitigation and compensation schemes.

To address the accuracy degradation due to crossbar non-idealities, we also propose CxDNN, a hardware-software methodology to realize high accuracy DNNs on resistive crossbar systems. CxDNN is composed of a conversion algorithm, a fast re-training method, and a low-overhead hardware compensation scheme. The conversion algorithm takes any given floating-point DNN and converts its weights to conductances and activation values to voltages by determining appropriate scaling factors. Subsequently, CxDNN uses a fast re-training method to recover accuracy loss due to the conversion with very few iterations. We note that our re-training method is hardware instance independent and therefore needs to be performed only once overall (and not once per instance). Finally, CxDNN mitigates data-dependent and hardware-instance-specific errors using low-overhead error compensation circuits that post-process the crossbar outputs. We evaluate CxDNN using 6 state-of-theart DNNs on the ImageNet dataset. Our results show that CxDNN improves top-1 accuracy by 16%-49% and obtains classification accuracies comparable to a software fixed-point implementation, thereby alleviating non-idealities as an impediment to the use of resistive crossbar based in-memory computing fabrics.

#### 1.3.3 Non-Boolean Computing with CMOS-based memory cells

The use of lower precision to perform computations has emerged as a popular technique to enable complex Deep Neural Networks (DNNs) to be realized on energyconstrained platforms. In the quest for lower precision, studies to date have shown that ternary DNNs, which represent weights and activations by signed ternary values, represent a promising sweet spot, and achieve accuracy close to full-precision networks on complex tasks such as language modeling and image classification. We propose TiM-DNN, a programmable hardware accelerator that is specifically designed to execute state-of-the-art ternary DNNs. TiM-DNN supports various ternary representations including unweighted (-1,0,1), symmetric weighted (-a,0,a), and asymmetric weighted (-a,0,b) ternary systems. TiM-DNN is an in-memory accelerator designed using TiM tiles — specialized memory arrays that perform massively parallel signed vector-matrix multiplications on ternary values per access. TiM tiles are in turn composed of Ternary Processing Cells (TPCs), new bit-cells that function as both ternary storage units and signed scalar multiplication units. We evaluate an implementation of TiM-DNN in 32nm technology using an architectural simulator calibrated with SPICE simulations and RTL synthesis. TiM-DNN achieves a peak performance of 114 TOPs/s, consumes 0.9W power, and occupies  $1.96mm^2$  chip area, representing a 300X and 388X improvement in TOPS/W and TOPS/ $mm^2$ , respectively, compared to a state-of-the-art NVIDIA Tesla V100 GPU. In comparison to popular DNN accelerators, TiM-DNN achieves 55.2X-240X and 160X-291X improvement in TOPS/W and TOPS/ $mm^2$ , respectively. We compare TiM-DNN with a well-optimized near-memory accelerator for ternary DNNs across a suite of stateof-the-art DNN benchmarks including both deep convolutional and recurrent neural networks, demonstrating 3.9x-4.7x improvement in system-level energy and 3.2x-4.2x speedup.

#### 1.4 Thesis outline

We have organized the rest of the thesis as follows. Chapter 2 details the related efforts in the area of near- and in-memory computing and also presents the thesis contributions in their context. Chapter 3 provides the necessary background on the spintronic devices, resistive crossbar systems, and deep neural networks (DNNs). Chapter 4 proposes in-memory computing with STT-MRAM. Chapter 5 presents a fast, accurate, and scalable simulation framework to evaluate and re-train large-scale DNNs on resistive crossbar systems. Chapter 6 details hardware-software compensation schemes to mitigate the impact of crossbar non-idealities on DNNs realized using resistive crossbars. Chapter 7 proposes a new CMOS-based in-memory computing design for accelerating ternary DNNs. Finally, chapter 8 concludes the thesis.

### 2. RELATED WORK

The idea of closer integration of logic and memory has been explored at various levels to alleviate the fundamental processor-memory bottlenecks. There have been numerous research efforts that explore the possibility of near- and in-memory computing using the traditional CMOS memory technologies such as SRAM and DRAM, as well as emerging memory technologies, *viz.*, ReRAM, PCM, and Spintronic. These efforts are variedly referred to in the literature as logic-in-memory, computing-in-memory, and processing-in-memory. They can be broadly classified into two categories, as shown in Figure 2.1. We limit the scope of our discussion to approaches that improve the efficiency of active computation. For example, we do not discuss the embedding of non-volatile memory elements into a logic circuit [92–95] in order to enable the system to shut-down and wakeup efficiently for improved power management. In this chapter, we discuss the research efforts directed towards processing-in-memory using both CMOS and emerging memory technologies.

#### 2.1 Near-memory Computing

Near-memory computing refers to bringing logic or processing units closer to memory. Notwithstanding the closer integration, processing units still remain distinct from memory arrays. Near-memory computing has been explored at various levels of the memory hierarchy [4–8, 10–17]. Intelligent RAM (IRAM) [4] is an early example, which integrated a processor and DRAM in the same chip to improve the bandwidth between them. Embedding simple processing units within each page of the main memory [5] and within secondary storage [6] enables computations to be performed near memory. Application-specific examples of near-memory computation are: (i) memory that can generate interpolated values, enabling the evaluation of

Fig. 2.1.: Taxonomy of computing near/in memory

complex mathematical functions [15], and (ii) Deep Neural Network (DNN) accelerators [10, 96, 97]. Near-memory computing has gained significant interest in recent years, with industry efforts like Hybrid Memory Cube (HMC) [16] and High Bandwidth Memory (HBM) [17].

#### 2.2 In-memory Computing

In-memory computing [18–21, 24–27, 98] integrates logic operations into memory arrays, fundamentally blurring the distinction between processing and memory. In comparison to near-memory computing, a key advantage of in-memory computing is that it enables a much higher level of parallelism by enabling and computing on multiple memory rows simultaneously, thereby achieving superior performance and energy efficiency. We can classify previous proposals for in-memory computing based on whether they target application-specific or general-purpose computations, and based on the underlying memory technology that they consider.

#### 2.2.1 General-purpose in-memory computing

General-purpose examples of in-memory computing include evaluation of bitwise logic operations using emerging memories [21-23,26,99] and DRAM [24]. CRAM [20]that introduces an extra transistor (2T-1R) to enable evaluation of complex functions within the array is another example of general-purpose in-memory computing. The key challenge of general-purpose in-memory computing is to realize it without impacting the desirability of the resulting design as a standard memory (*i.e.*, density or efficiency of standard read and write operations). Due to these constraints, general-purpose in-memory computing designs are typically limited to performing a small number of simple operations.

### 2.2.2 Application-specific in-memory computing

Application-specific examples of in-memory computing include vector-matrix multiplication [27–30] and sum-of-absolute difference [19] computation. Ternary contentaddressable memory [18], ROM-embedded RAM [100], AC-DIMM [25] and Micron's automata processor [101] can also be viewed as examples of in-memory computing that target specific operations such as pattern matching or evaluation of transcendental functions. Next, we discuss examples of in-memory computing targeting Deep Neural Network (DNN) applications in more detail.

#### 2.2.3 In-memory computing for Deep Neural Networks (DNNs)

Deep neural networks (DNNs) have greatly advanced the state-of-the-art in machine learning tasks involving video, image, speech and natural language processing, and are currently used in several real-world products and services [1]. The high computation and memory requirements of DNNs often pose challenges to the computing platforms on which they are executed. Currently, GPUs and specialized accelerators like Google's TPU and Microsoft's Brainwave are the mainstays for DNN execution. However, the continuing increase in DNN complexity and amount of data processed has fueled an active interest in new hardware fabrics that can deliver further improvements in efficiency, and thereby enable the virtuous cycle of advances in deep learning algorithms and hardware to continue.

In recent years, several research efforts have focused on improving the energy efficiency and performance of DNNs at various levels of design abstraction [87–89,102–108]. In this subsection, we limit our discussion to efforts on in-memory computing for DNNs [28, 30, 109–117]. Table 2.1 classifies prior in-memory computing efforts based on the memory technology [CMOS and Non-Volatile Memory (NVMs)] and the targeted precision. One group of efforts [28, 30, 109, 110] has focused on in-memory DNN accelerators using emerging Non-Volatile memory (NVM) technology such as PCM and ReRAM. Although NVMs promise density and low leakage relative to CMOS, they still face several open challenges such as errors due to the device and circuit-level non-idealities, which we address in this dissertation. The other group of efforts [111–118] has focused on in-memory DNN accelerators using the mainstay CMOS technology.

#### ,

## 2.2.4 In-memory computing for DNN applications using CMOS-based memory cells

Efforts on SRAM-based in-memory accelerators can be classified into those that target binary [111–115] and high-precision [116–118] DNNs. Accelerators targeting binary DNNs [111–115] can execute massively parallel vector-matrix multiplication per array access. However, the restriction to binary networks is a significant limitation as binary networks (known to date) incur a large drop in accuracy. Efforts [116–

|                  |                        | In-memory Computing for DNN applications                                                              |                                                                                   |  |

|------------------|------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

| Weight Precision |                        | смоя                                                                                                  | NVM                                                                               |  |

| В                | inary                  | In-Mem Classifier [111],<br>Conv-RAM [112],<br>R Lui. et al. [113], XNOR-SRAM [114],<br>Xcel-RAM[115] | Binary-RRAM[110],<br>XNOR-RRAM[109],<br><b>RxNN, CxDNN</b> [This<br>dissertation] |  |

| Ternary          | Unweighted<br>(-1,0,1) | TiM-DNN [This dissertation]                                                                           | -                                                                                 |  |

| Ternary          | Weighted<br>(-a,0,b)   | TiM-DNN [This dissertation]                                                                           | -                                                                                 |  |

| > 2 bits         |                        | Neural Cache [116],<br>A Jaiswal et al. [117],<br>Compute-mem[118]                                    | RENO [28], PRIME[30],<br>PUMA [123]<br><b>RxNN, CxDNN</b> [This<br>dissertation]  |  |

Table 2.1.: Examples of In-memory Computing for DNN applications

118] that target higher precision (4-8 bit) DNNs require multiple execution steps (array accesses) to realize signed dot-product operations, wherein both weights and activations are signed numbers. For example, Neural cache [116] computes bitwise Boolean operations in-memory but uses bit-serial near-memory arithmetic to realize multiplications, requiring several array accesses per multiplication operation (and many more to realize dot-products).

## 2.2.5 In-memory computing for DNN applications using emerging memories

Resistive crossbars have witnessed significant research interest in recent years due to their ability to efficiently realize vector-matrix multiplications, *i.e.*, the primitive machine learning kernel [119–122]. In this subsection, we focus on prior works that target DNNs on resistive crossbar systems. These efforts can be broadly classified into specialized hardware accelerators [28–30,66–68,123], non-ideality mitigation schemes [69–78], and design tools for resistive crossbar systems [79–81,124].

**Specialized hardware accelerators.** Resistive crossbar based specialized hardware systems have been proposed for accelerating DNN inference [28–30,68,125] and training [66, 67] operations. These efforts focus on the evaluation of the proposed architecture using performance, energy, and area as their metrics. They either do not explicitly consider non-idealities or model only the limited-precision aspect of non-idealities.

Non-ideality mitigation schemes. We now discuss prior efforts that attempt to mitigate the effects of crossbar non-idealities. These efforts can be grouped into (i) methods that use (re-)training to compensate for errors [69, 71, 73, 75, 126–128], (ii) mapping to reduce computational errors [70, 74], (iii) closed-loop re-programming methods to overcome imperfect programming and drift in synaptic conductances [72, 76,78], and (iv) ECC schemes to reduce errors due to a specific device non-ideality [129] The focus of all these efforts is to evaluate and mitigate errors due to crossbar non-idealities. However, they are restricted to simple networks and small datasets since they lack a scalable simulation framework. Many of these efforts also lack a detailed crossbar model as they consider only a subset of crossbar non-idealities.

Training-based compensation [69,71,73,75,126] using software models of the crossbar is the most popular approach to compensating for non-idealities. However, retraining can only mitigate accuracy degradation to a limited extent. Further, it ties the network to the specific hardware instance and therefore is not scalable. For example, to create re-trained models for crossbar-based inference accelerators deployed in millions of IoT devices will correspondingly require millions of training runs. Another limitation of these efforts [69, 71, 73, 75, 126] is that they correct errors due to only a subset of crossbar non-idealities. For example, [126] can only mitigate errors due to driver resistance, source resistance, and chip-to-chip variations. It ignores other prominent non-idealities such as wire resistance, sneak paths, non-linear ADCs and DACs, and intra-chip process variations (each crossbar or synaptic device within a chip is uniquely impacted by process-variations). Finally, all (re-)training based prior efforts [69–73, 75, 76, 78, 126] are limited to small scale networks and data sets.

ECC scheme using AN codes have also been proposed to correct errors in resistive crossbars [129]. However, AN codes [130] can correct errors only in linear func-

tions realized using digital systems, wherein errors are discrete (at the bit-level) and can be quantified using the digital number representation (multiple bits). Although vector-matrix multiplications realized using digital systems are linear, the functions executed in resistive crossbars are not. For example, vector-matrix multiplications in resistive crossbars consist of several non-linear operations (viz., non-linear DACs and ADCs functions). The errors in resistive crossbars due to the cumulative effect of all non-idealities are analog and non-linear in nature. Therefore, ECC schemes cannot effectively mitigate errors in analog systems (experimental results shown in Section 6.3.5). Further, apart from assuming crossbar operations to be linear, another limitation of the prior effort [129] is that it only models errors due to a specific device non-ideality (random telegraph noise) and ignores circuit-level non-idealities, viz., wire resistances, sensing resistances, sneak paths, driver resistances, and non-linear ADCs and DACs.

**Design tools.** To aid design space exploration, prior efforts [79–81, 124] have proposed circuit-level macro models to evaluate crossbar systems. These efforts include (i) MNSIM [79], a simulation platform to evaluate inference accelerators designed using resistive crossbars, (ii) NeuroSim [124], a framework to evaluate crossbars systems designed for on-chip training, (iii) technological exploration tool to optimize resistive crossbar design space [80], and (iv) AutoNCS [81], a tool to optimize the utilization and efficiency of a resistive crossbar system. The primary focus of all these tools has been the performance, energy, and area evaluation of resistive crossbar systems to facilitate design space exploration. These tools also have simplistic accuracy/error models that are reasonable for design space exploration, but inadequate for evaluating application-level accuracy of DNNs.

#### 2.3 Thesis contributions

The primary contributions of this dissertation are different or complementary to the prior efforts in the following aspects:

Boolean Computing with Spin-Transfer Torque Magnetic RAM. Our work differs from application-specific in- and near-memory computing designs as we focus on embedding a broader set of operations (arithmetic, logic and vector operations) within memory. Our work also differs from efforts [21–23] that realize bitwise logic operations in several important aspects. First, we focus on in-memory computing for spintronic memory, which involves fundamentally different prospects and design challenges. For example, the proposed operations are not destructive to the contents stored in the accessed bit-cells (unlike [24]). On the other hand, the much lower ratio of on to off resistance in spintronic memory leads to lower sensing margins. Second, we use a different sensing and reference generation circuitry, which enables us to natively realize a wider variety of operations. For example, the proposed design requires only one array access (unlike two in the case of [21]) to perform bit-wise XOR operations. Third, our design goes beyond bitwise logic operations and realizes arithmetic as well as complex vector operations. Fourth, we propose architectural extensions (bus and ISA extensions) and data mapping techniques to enable in-memory computing within a general-purpose processor system. Finally, we address a key challenge associated with in-memory computing, viz., reliable operation under process variations. In contrast to the effort that uses 2T-1R STT-MRAM bit-cells [20], our proposal enables in-memory computation within a standard STT-MRAM array with no changes to the bit-cells. Moreover, unlike [20, 26] we do not restrict ourselves to device and circuit level considerations and also address the architectural challenges of in-memory computing.

Non-Boolean Computing: Framework for Evaluating Deep Neural Networks on Resistive Crossbars. Our work complements the prior efforts on hardware accelerators [28–30, 66–68] and non-ideality mitigation schemes [69–78]. We focus on the functional evaluation of large-scale DNNs, including winners from previous ImageNet challenges [131]. We address the need for a fast, scalable, and accurate framework for resistive crossbar systems to enable evaluation and re-training of largescale DNNs. Moreover, unlike simple error estimation model [79, 80], we focus on a more accurate model that captures the cumulative effects of all non-idealities including data-dependent errors, *i.e.*, the errors that depend on the weights programmed into, and inputs applied to the crossbar.

Non-Boolean Computing: Hardware-Software Compensation methods for Deep Neural Networks on Resistive Crossbar Systems. CxDNN complements and improves upon previous efforts by proposing a hardware-software methodology that scales to large DNNs, avoids hardware-instance-specific (re-)training, can correct errors due to a wider range of crossbar non-idealities (including both device and circuit-level non-idealities), and uses low-overhead compensation circuits to better alleviate dynamic and hardware instance specific errors. Other prior efforts [72,76,78] using closed-loop programming may be combined with CxDNN to specifically address programming errors.

Non-Boolean Computing with CMOS: Ternary in Memory accelerator for Deep Neural Networks. In contrast to previous proposals, TiM-DNN is the first specialized and programmable in-memory accelerator for ternary DNNs that supports various ternary representations including unweighted (-1,0,1), symmetric weighted (a,0,a), and asymmetric weighted (-a,0,b) ternary systems. TiM-DNN utilizes a new CMOS-based bit-cell (i.e., TPC) and enables multiple memory rows simultaneously to realize massively parallel in-memory signed vector-matrix multiplications with ternary values per memory access, enabling efficient realization of ternary DNNs. As illustrated in our experimental evaluation, TiM-DNN achieves 3.9x-4.7x improvement in system-level energy and 3.2x-4.2x speedup over a well-optimized near-memory accelerator. In comparison to the near-memory ternary accelerator [97], it achieves 55.2X improvement in TOPS/W.

## 3. BACKGROUND

In this chapter, we provide the necessary background information on the emerging memory technologies, the resistive crossbar system, and DNNs.

## 3.1 STT-MRAM

This section presents the STT-MRAM bit-cell structure and describe the basic read and write operations.

Fig. 3.1.: STT-MRAM bit-cell