# INTEGRATION OF FERROELECTRICITY INTO ADVANCED 3D GERMANIUM MOSFETS FOR MEMORY AND LOGIC APPLICATIONS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Wonil Chung

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2019

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Peide Ye, Chair

School of Electrical and Engineering

- Dr. Muhammad Ashraful Alam School of Electrical and Engineering

- Dr. Peter Bermel School of Electrical and Engineering

- Dr. Dana Weinstein School of Electrical and Engineering

## Approved by:

Dr. Dimitrios Peroulis

Head of the School Graduate Program

To my family and my wife, Jiwon

#### ACKNOWLEDGMENTS

First and foremost, I thank God Almighty for blessing me with all the motivations, wisdom, opportunities, courage, strength and faith that guided me along my life till now. I always pray I can be grateful in all circumstances and give thanks and praise for every breath I take as I commence towards the next chapter of my life. I am grateful to have such loving family members who prayed for me and trusted me when I started my journey as a researcher. It was miraculous for me to have met and married Jiwon. I thank her for her endless love and supports in every way.

As I entered the US back in 2015 and started my PhD life here at Purdue, I never thought that this very moment, thinking of whom I should express my gratitude to, would come so soon. Looking back to my life within the fences of 3 different universities, I was always blessed to meet inspiring people who not only shaped academic portion of me but also in various other ways.

Meeting Professor Peide Ye as my PhD advisor was a blessing to me. His insight and patience helped me stay motivated without becoming nervous. As an experiment-oriented graduate student, such considerate advice greatly affected the overall progress and results throughout my PhD period. His relentless pursuit of integrity, hardworking and novelty was an ideal model to me as a successful researcher. Every weekly group meeting clearly showed me how he was caring and interested in various fields of studies that each student was in charge of. His enthusiasm towards great researches motivated me tremendously.

Along with Prof. Ye, I also thank my committee members, Professor Muhammad Ashraful Alam, Peter Bermel and Dana Weinstein for their insightful comments and discussions during my exams. Prof. Alam's online courses & seminars and Prof. Weinstein's ECE606 were elaborate and carefully arranged to help me digest the materials. Prof. Bermel's detailed guidance as I was preparing for NEPTUNE project was very helpful.

In everyday experiments, collaborative help from the fellow lab-mates were truly precious. Specifically I would like to thank Dr. Heng Wu and Dr. Mengwei Si for their sincere comments and supports. Detailed studies carried out by Dr. Heng Wu helped me accelerate my GeOI-based studies and also towards the optimization of SOI processes as well. As a great friend and a sincere lab-mate, I was fortunate to have spent time in clean room with Dr. Mengwei Si. His innovative and bright comments were tremendously helpful. In addition, I thank all of my colleagues since my first day at Purdue, Dr. Jingyun Zhang, Dr. Chun-Jung Su, Dr. Wangran Wu, Dr. Yexin Deng, Dr. Yuchen Du, Dr. Ling-Ming Yang, Dr. Hong Zhou, Dr. Jingkai Qin, Dr. Hagyoul bae, Dr. Sami Alghamdi, Dr. Sanghoon Shin, Dr. Woojin Ahn, Dr. Kyunghun Han, Dr. Seung Seob Lee, Dr. Chang Keun Yoon, Dr. Doosan Back, Nathan Conrad, Gang Qiu, Jinhyun Noh, Adam Charnas, Xiao Lyu, Pai-Ying Liao, Dongqi Zheng, Chang Niu, Zhuocheng Zhang, Zehao Lin, Junkang Li and Yiming Qu. I'd also like to thank the overnight Birck-mates as well, Jiseok Kwon, Dongmin Pak, Yunjo Lee, Naeemul Islam and Abdullah Al Noman.

I express my gratitude to all of those I met who aided me achieve what I have in my hands now. Without hard-working and responsible Birck staffs, it would have been impossible for me to fabricate state-of-the-art devices. I thank Dr. Joon Hyeong Park, Dr. Yi Xuan, Bill Rowe, Dr. Justin Wirth, Jeremiah Shepard, Kenny Schwartz, Dave Lubelski, Dan Hosler, Richard Hosler, Francis Manfred, Dr. Rosa Diaz, Mary Jo Totten, Kyle Corwin, Nancy Black, Lorraine Fox, Danielle Houston, Victoria Roger, Brenda Meador and all other staffs at Birck and Purdue who generously gave me their helping hands.

Industry projects helped me learn how to collaboratively work as a team. Discussions with Dr. Nerissa Draeger, Dr. Katie Nardi of LAM research and Dr. Mark Rodder, Dr. Wei Wang of Samsung Advanced Logic Lab were of great help as I carried out respective projects. It was a great chance for me to learn not only academic but also industrial point of views on various topics. Collaboration with National Institute of Standards and Technology (NIST) was very pleasant experience in 2018. I appreciate Dr. Kin P. Cheung, Dr. Jason P. Campbell and Dr. Pragya R. Shrestha for warmly hosting us to their lab in Gaithersburg, MD for a week.

There are so many others who I simply couldn't list all of their names here including all of my sincere friends in Korea and all around the world. I hope I can keep undisturbed connections as I step out of Purdue. I will pursue a humble life as a helping hand to others in need. Thank you.

## TABLE OF CONTENTS

|    |      |                                                           | Page  |

|----|------|-----------------------------------------------------------|-------|

| LI | ST O | F TABLES                                                  | . ix  |

| LI | ST O | F FIGURES                                                 | . x   |

| SY | YMBC | LS                                                        | xviii |

| AI | BBRE | VIATIONS                                                  | . xxi |

| AI | BSTR | ACT                                                       | xxiv  |

| 1  | INT  | RODUCTION                                                 | . 1   |

|    | 1.1  | Devices with higher performance: Scaling                  | . 1   |

|    | 1.2  | Alternative channel material: Germanium and its challenge | . 1   |

|    |      | 1.2.1 Interface Engineering: Gate stack                   | . 3   |

|    |      | 1.2.2 Contact Engineering: Source and Drain               | . 4   |

|    | 1.3  | Better performance: Lower power and steeper slope         | . 5   |

|    |      | 1.3.1 Ferroelectric oxide and its switching               | . 9   |

|    |      | 1.3.2 Hysteresis-free operation in a NCFET                | . 10  |

|    |      | 1.3.3 Short channel effects in NCFET                      | . 12  |

|    | 1.4  | Possible application as a neuromorphic synapse            | . 13  |

|    | 1.5  | Thesis Outline                                            | . 16  |

| 2  | GE I | TEFET TOWARDS MEMORY APPLICATION                          | . 18  |

|    | 2.1  | Introduction                                              | . 18  |

|    | 2.2  | Ferroelectric $Hf_xZr_{1-x}O_2$ (HZO)                     | . 18  |

|    |      | 2.2.1 ALD-deposited HZO                                   | . 20  |

|    |      | 2.2.2 Dry etching of HZO                                  | . 26  |

|    | 2.3  | Germanium FeFET                                           | . 28  |

|    | 2.4  | Time Response of Polarization                             | . 35  |

|    | 2.5  | Stress analysis in ALD HZO                                | . 43  |

## Page

| 3  | GE   | NCFET TOWARDS STEEP-SLOPE LOGIC APPLICATION 47                |

|----|------|---------------------------------------------------------------|

|    | 3.1  | Introduction                                                  |

|    | 3.2  | Germanium NCFET                                               |

|    | 3.3  | Short channel effect in Ge NCFETs                             |

|    | 3.4  | Digital etching technique for smaller devices                 |

| 4  | GE   | FEFET TOWARDS NEUROMORPHIC COMPUTING                          |

|    | 4.1  | Introduction                                                  |

|    | 4.2  | Ge NW FeFET synaptic device                                   |

|    | 4.3  | Optimization of update pulses                                 |

|    | 4.4  | On-line learning simulation with Ge FeFET                     |

|    |      | 4.4.1 Linearity and asymmetry analysis                        |

|    |      | 4.4.2 Online learning accuracy of Ge FeFET synaptic device 89 |

| 5  | SUN  | IMARY AND OUTLOOK                                             |

|    | 5.1  | Summary                                                       |

|    | 5.2  | Outlook                                                       |

| RI | EFER | LENCES                                                        |

| V  | ΓA   |                                                               |

| ΡĮ | UBLI | CATIONS                                                       |

## LIST OF TABLES

| Tabl | le                                                                                                                                                                                                                                  | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1  | Atomic % of O, C, Si, Zr, Hf and Al with increasing etch time as shown in Fig. 2.4 (a).                                                                                                                                             | . 23 |

| 2.2  | Fabrication process of germanium ferroelectric FinFET in detail                                                                                                                                                                     | . 30 |

| 3.1  | Benchmark of device parameters extracted from various reported experi-<br>mental NCFETs at room temperature. Hysteresis is defined as $\Delta V_{T,NMOS} = V_{T,rev} - V_{T,for}$ and $\Delta V_{T,PMOS} = V_{T,for} - V_{T,rev}$ . |      |

| 3.2  | Etched Ge (nm) and etch rate (nm/s) as a function of etch window (nm).                                                                                                                                                              | . 65 |

| 4.1  | Fabrication process of germanium ferroelectric nanowire FET in detail                                                                                                                                                               | . 74 |

| 4.2  | Benchmark of reported works based on FeFET syanptic devices for online learning                                                                                                                                                     | . 93 |

## LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

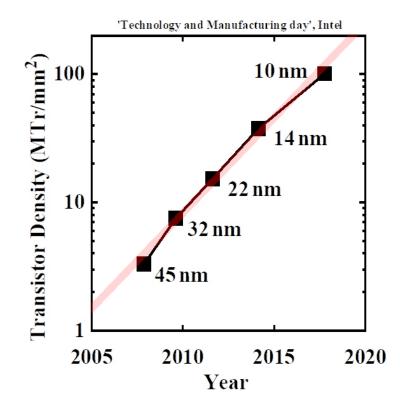

| 1.1  | Transistor density with respect to year. Density calculation is based on Mark Bohr's proposed method in Intel's 2017 Technology and Manufacturing day [1]                                                                                                                                                                                                                                                                        | . 2  |

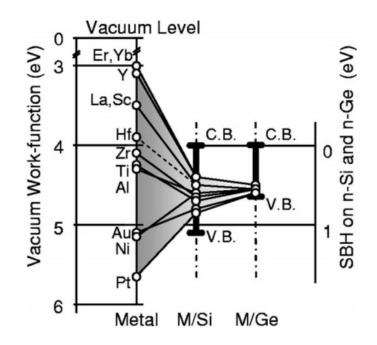

| 1.2  | Schottky barrier heights (SBH) extracted from n-Si and n-Ge versus var-<br>ious metal work functions. In case of n-Ge, strong pinning effect can be<br>seen [32]                                                                                                                                                                                                                                                                 | . 4  |

| 1.3  | (a) Recessed S/D structure enhances the electron tunneling efficiency by reducing barrier width $(W_{SB})$ which lowers the resistivity. (b) IV curves from TLM pads before and after S/D recess etching on n-Ge. (c) Linear scale representation of (b). (d) Measured resistance from the TLM pattern (inset) with Ni-nGe contact [37].                                                                                         | . 6  |

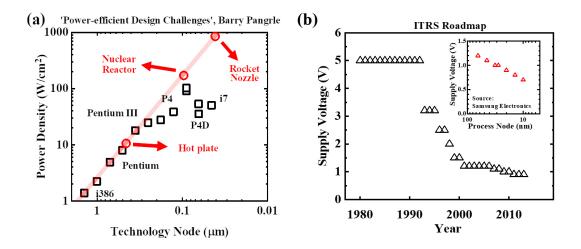

| 1.4  | (a) Power density with respect technology node has increased rapidly. (b) Supply voltage was not scaled accordingly. Inset graph shows most recent trend in supply voltages                                                                                                                                                                                                                                                      | . 7  |

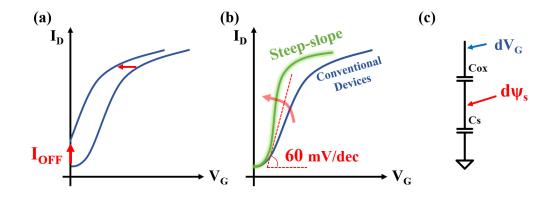

| 1.5  | (a) In conventional devices, reducing the supply voltage results in exponential increase in $I_{OFF}$ due to lower limit of SS (60 mV/dec at room temperature). As shown in (b), an ideal steep slope device exhibits lower SS (below 60 mV/dec at room temperature) and therefore can produce larger current with smaller voltage. (c) A simple capacitance network in a MOS transistor showing the body factor, $d\Psi_S/dV_G$ |      |

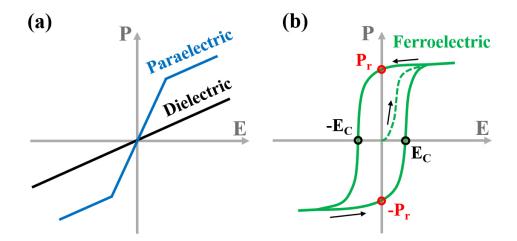

| 1.6  | Polarization as a function of electric field in a typical (a) dielectric and paraelectric and (b) ferroelectric material. Due to spontaneous polarization, ferroelectric material show remnant polarization $(P_r)$ even after the external electric field is removed. Electric field beyond $E_C$ is needed to switch the spontaneous polarization direction.                                                                   |      |

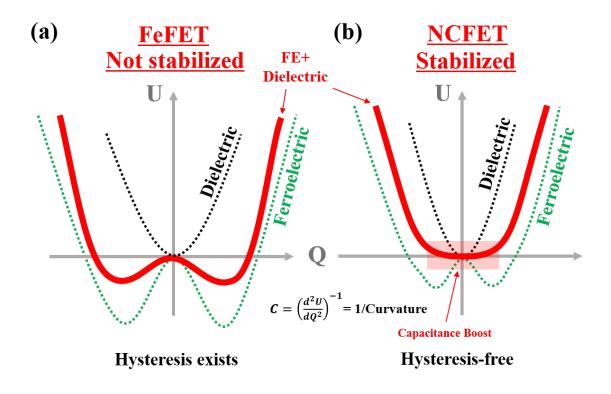

| 1.7  | Energy landscape (U) vs charge (Q) of a (a) FeFET and (b) NCFET.<br>If ferroelectric oxide layer in series with positive dielectric layer is not<br>stabilized appropriately, ferroelectric voltage hysteresis exists within the<br>overall gate oxide resulting in ferroelectric FET (FeFET) depicted in (a).<br>However, when the series capacitors are stabilized, hysteresis-free NCFET<br>cap be realized                   | 11   |

|      | can be realized.                                                                                                                                                                                                                                                                                                                                                                                                                 | . 11 |

| Figu | re P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | age  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

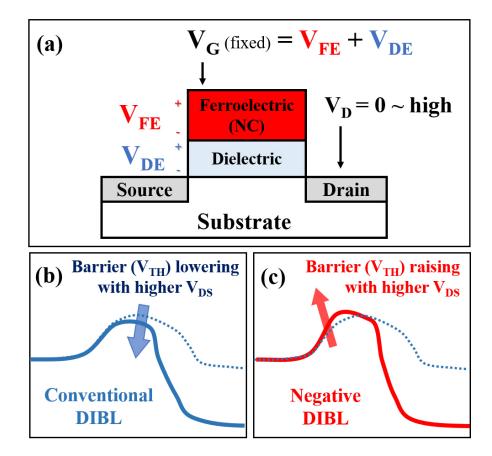

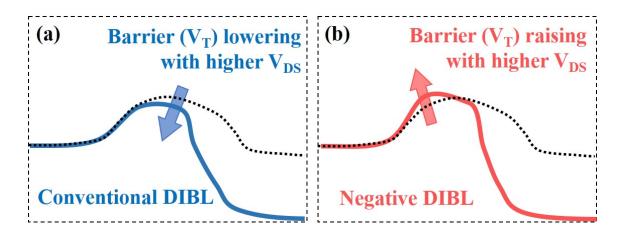

| 1.8  | (a) A simple series capacitance representation of a gate stack in a NCFET.<br>Due to negative capacitance and drain to channel capacitance coupling, increasing $V_D$ results in decrease in charge, increase in $V_{FE}$ , decrease in $V_{DE}$ and thus decrease in channel charge. Diagrams showing (b) DIBL in a conventional MOSFET and (c) negative DIBL in a NCFET                                                                                                                  | 12   |

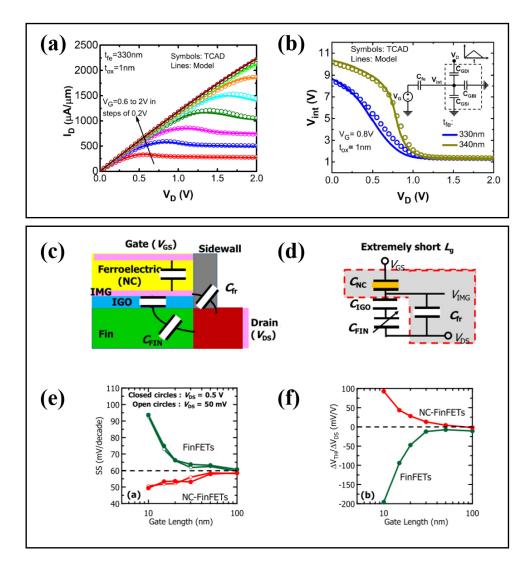

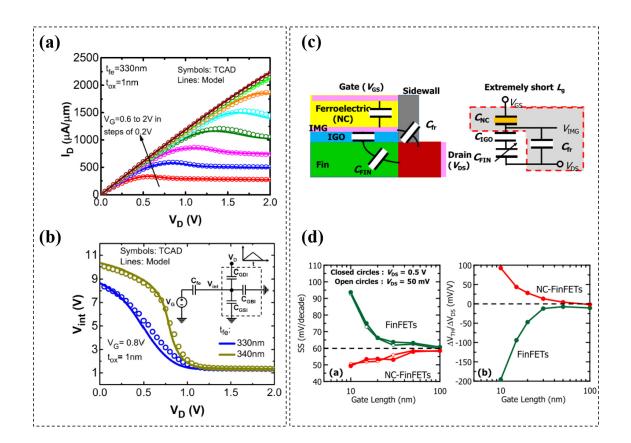

| 1.9  | (a) Negative differential resistance (NDR) can be observed with increasing $V_D$ [51]. (b) Such negative DIBL is due to drain to channel capacitance coupling and negative capacitance of $C_{FE}$ [51]. (c) and (d) show the effect of fringing capacitance ( $C_{fr}$ ) within a NCFET. With shorter channel lengths, $C_{fr}$ becomes more dominant and reduced $V_{IMG}$ causes the opposite trends in (e) SS and (f) $\Delta V_T / \Delta V_{DS}$ with respect to channel length [52] | ].14 |

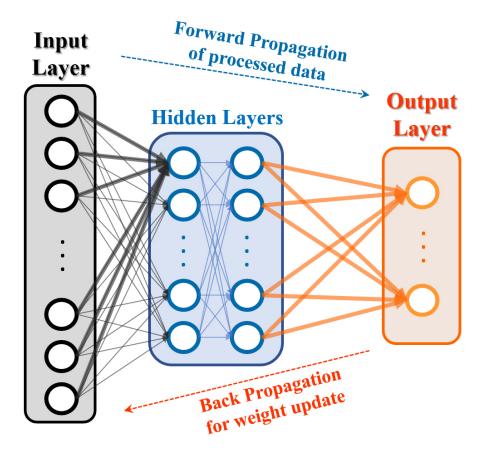

| 1.10 | A diagram that describes the operation of an online training scheme in<br>a deep neural network including the back propagation for the weight up-<br>dates. 2 hidden layers were depicted                                                                                                                                                                                                                                                                                                  | 15   |

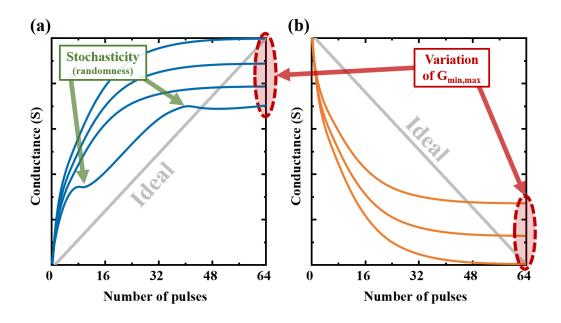

| 1.11 | Conductance profile during (a) potentiation and (b) depression process.<br>Ideally, conductance profile should be linearly proportional to the num-<br>ber of applied pulses. Non-ideal features such as stochasticity (random<br>conductance update) and variation in $G_{max}$ or $G_{min}$ is shown in both figures                                                                                                                                                                     | 5.16 |

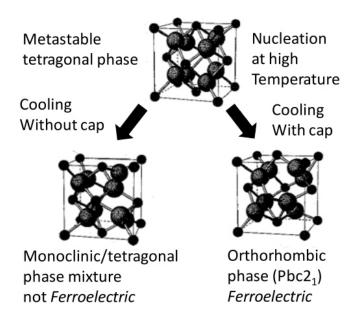

| 2.1  | Ferroelectricity induced due to transformation from tetragonal to orthorhom-<br>bic crystal structure in doped $HfO_2$ layer [73]                                                                                                                                                                                                                                                                                                                                                          | 19   |

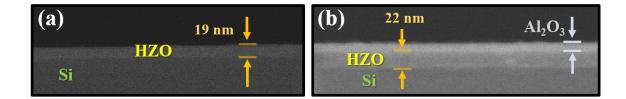

| 2.2  | (a) Deposited $Hf_xZr_{1-x}O_2$ at 250 °C. 120 cycles resulted in approximately 19 nm of HZO. (b) 156 cycles result in 22 nm which shares the same deposition rate                                                                                                                                                                                                                                                                                                                         | 20   |

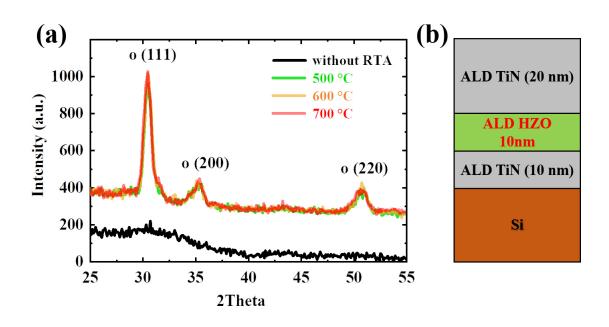

| 2.3  | <ul><li>(a) XRD peaks showing distinct difference in crystallographic structure in annealed HZO. Black curve shows as-dep HZO before RTA crystallization.</li><li>(b) Oxide stack analyzed in (a)</li></ul>                                                                                                                                                                                                                                                                                | 21   |

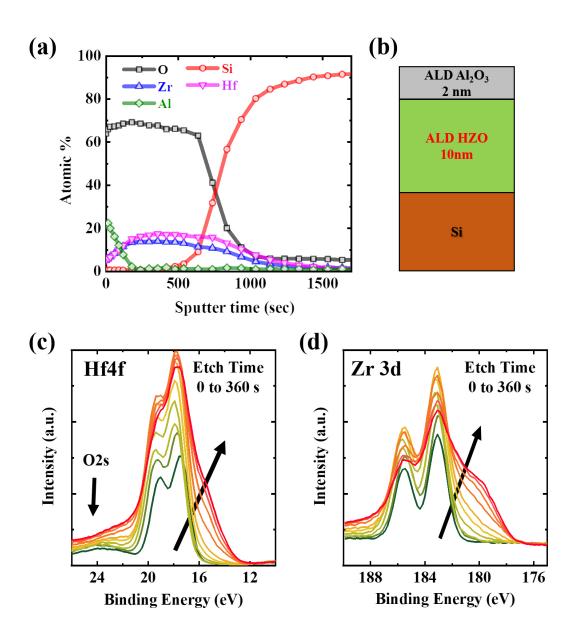

| 2.4  | (a) Atomic compositional ratio acquired by ion sputtering the sample (shown in (b)) for depth profiling using AR-XPS. (c) Hf4f and (d) Zr 3d XPS peaks as a function of etch time. It can be concluded that Hf:Zr=1:1 from (a) since during the first 120 seconds of sputtering, Hf:Zr=1:1 and slightly higher Hf % after 120 seconds could be due to increasing O2s peak in (c). Detailed % can be found in Table 2.1                                                                     | 22   |

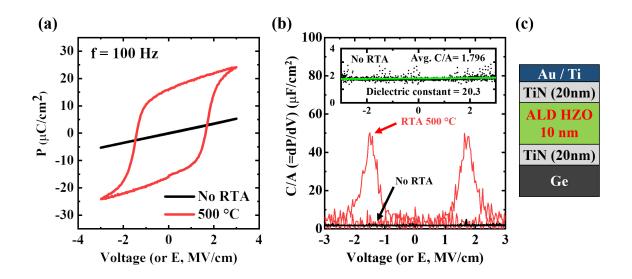

| 2.5  | Polarization - Electric field curve measured with ferroelectric tester. (a)<br>Polarization before and after RTA reveals clear transition from dielec-<br>tric HZO to ferroelectric HZO. (b) When the P is differentiated with V<br>(dP/dV), capacitance density ( $\mu$ F/cm <sup>2</sup> ) can be acquired. Inset shows the<br>capacitance density of the sample before RTA. (c) Structure of the ferro-<br>electric sample measured in this figure                                      | 24   |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                              | Page  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

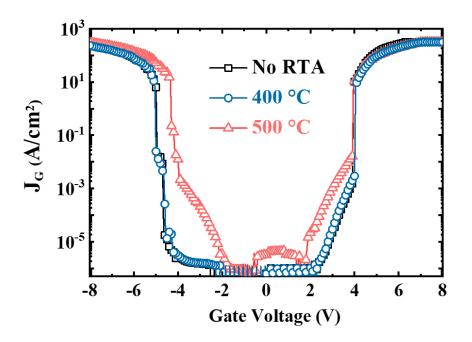

| 2.6  | Leakage current of the gate stack seen in Fig. 2.5 (c). RTA with higher temperature increases the leakage current. Breakdown voltage of HZO (10 nm) is extracted to be approximately $\pm 5$ V                                                                                                                                                                                                                  | . 25  |

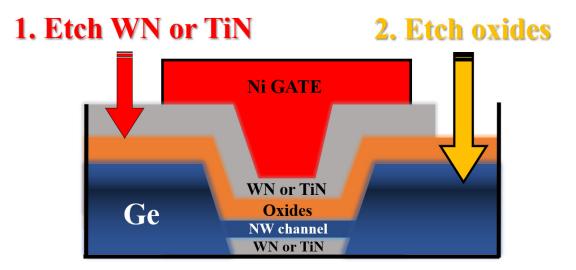

| 2.7  | Etching recipe needed for fabrication of ALD-deposited $Metal/HZO/Al_2O_3/$ gate stack. If step 1 can be highly selective, oxides can be used as an etch-stop layer.                                                                                                                                                                                                                                            |       |

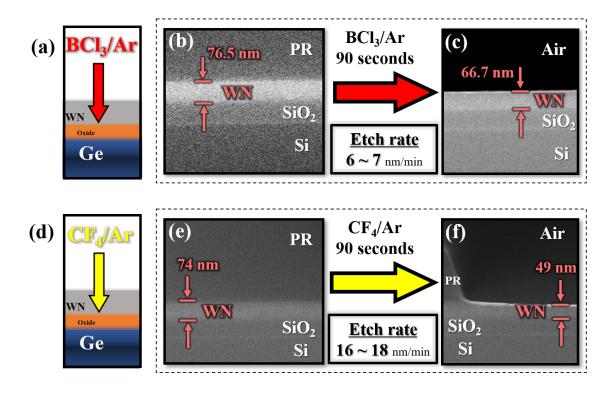

| 2.8  | (a)-(c) show the structure of the WN/oxide/Ge stack tested with $BCl_3/Ar$ recipe. (d)-(f) are tested with $CF_4/Ar$ recipe. Both gases etch WN film.                                                                                                                                                                                                                                                           | . 27  |

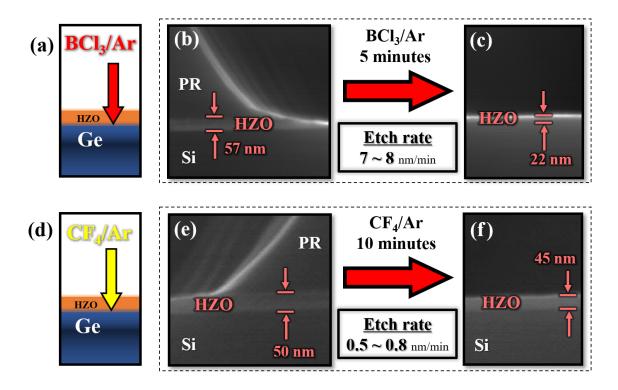

| 2.9  | (a)-(c) show the structure of the HZO/Ge stack tested with $BCl_3/Ar$ recipe. (d)-(f) are tested with $CF_4/Ar$ recipe. $CF_4/Ar$ recipe has significantly slower HZO etch rate                                                                                                                                                                                                                                 | . 28  |

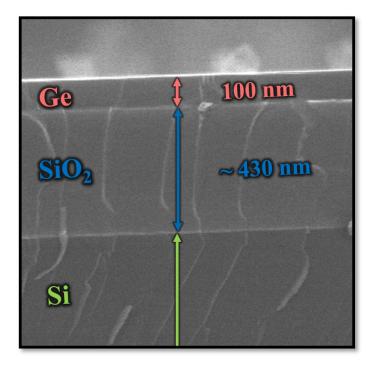

| 2.10 | GeOI wafer used for fabrication of germanium FeFETs. Top germanium layer thickness is 100 nm and the underlying SiO <sub>2</sub> has thickness of $\sim 430$ m                                                                                                                                                                                                                                                  | nm.29 |

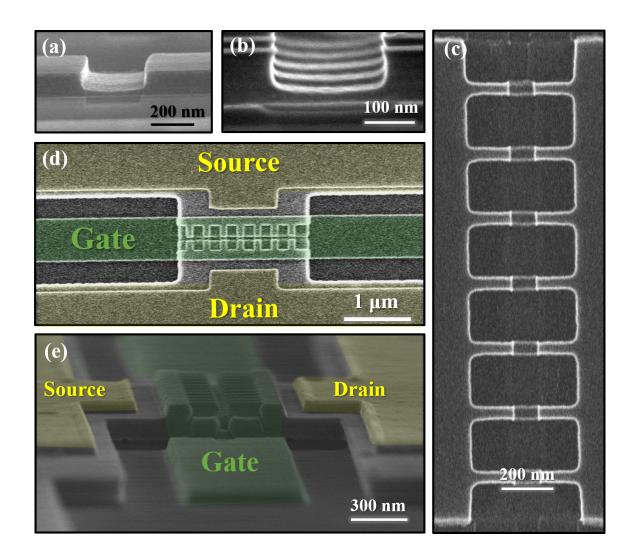

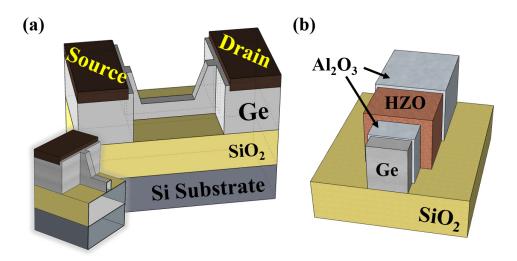

| 2.11 | (a) Recessed channel with fin height of approximately 22 nm. (b) Multiple parallel fins defined by $SF_6$ -based dry etching that was used for the channel recess. (c) Top-view of fabricated parallel fin structures shown in (b). (d) False-colored SEM image showing multiple parallel fins seen from top. Gate, source and drain metallization was done. (e) Side view of (d) after all fabrication process | . 31  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                 | . 01  |

| 2.12 | (a) Recessed channel with fin height of approximately 22 nm. (b) Multiple        |

|------|----------------------------------------------------------------------------------|

|      | parallel fins defined by $SF_6$ -based dry etching that was used for the channel |

|      | recess. (c) Top-view of fabricated parallel fin structures shown in (b). (d)     |

|      | False-colored SEM image showing multiple parallel fins seen from top.            |

|      | Gate, source and drain metallization was done. (e) Side view of (d) after        |

|      | all fabrication process                                                          |

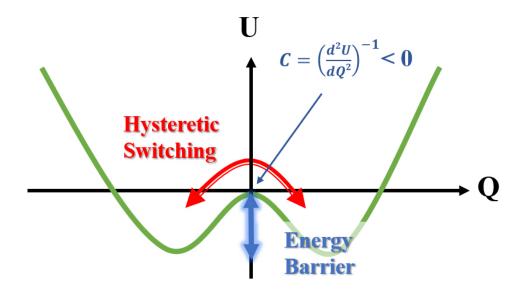

#### 2.13 Origin of voltage hysteresis in a ferroelectric material. Energy barrier is where the unstable negative capacitance $((d^2U/dQ^2)^{-1} < 0)$ region exists. 33

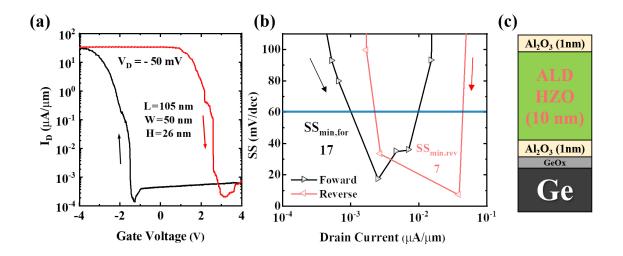

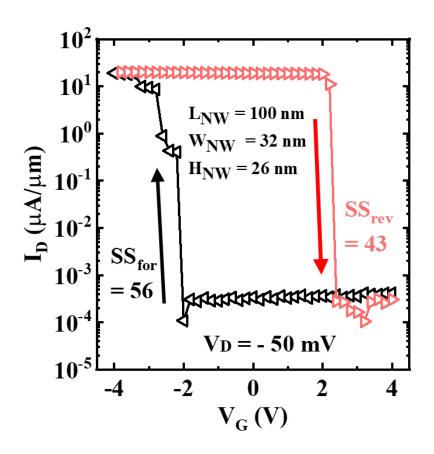

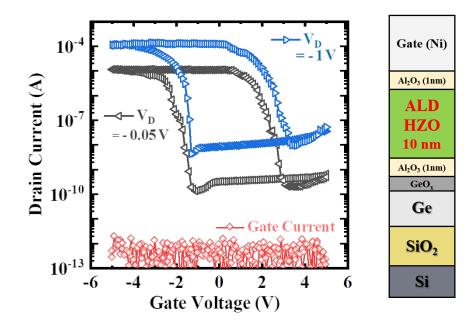

| 2.14 | (a) Transfer curve $(I_D - V_G)$ of a typical Ge FeFET at low $V_D = -50$ mV. |    |

|------|-------------------------------------------------------------------------------|----|

|      | Ferroelectric hysteresis of approximately -4 V (clockwise for PMOS) can       |    |

|      | be seen. (b) SS as a function of drain current.                               | 33 |

|      |                                                                               |    |

| 2.15 | $V_G-V_T$ was swept from -1.8 to 1 V for the reverse sweep and 1 to -1.8 V    |    |

|------|-------------------------------------------------------------------------------|----|

|      | for the forward sweep. Note that due to large voltage hysteresis, $V_{T,for}$ |    |

|      | and $V_{T,rev}$ is apart from each other by ~ 4 V                             | 34 |

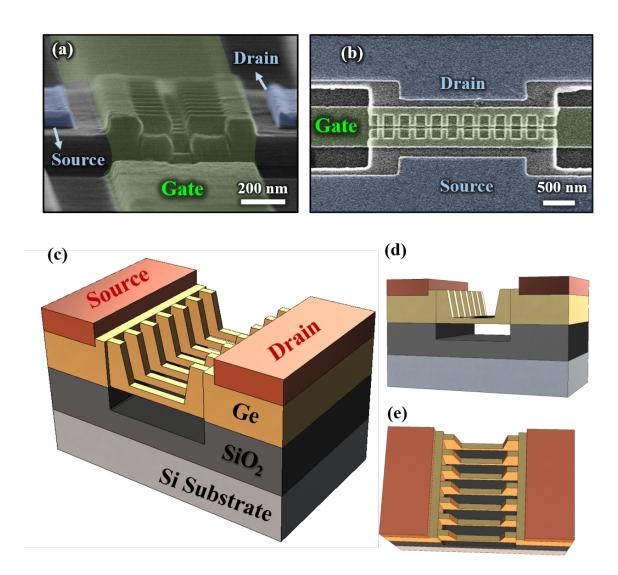

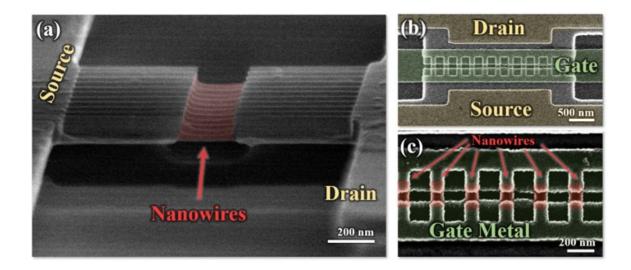

2.16 False-colored SEM images of fabricated germanium FE NWFETs viewed from (a) side and (b) top. Parallel nanowires form a single device. (c), (d) and (e) show the 3D structure of the fabricated devices from various

| re                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transfer curve $(I_D-V_G)$ of a Ge FeFET at low $V_D = -50$ mV used for time<br>response study. Ferroelectric hysteresis of approximately -4 V (clockwise<br>for PMOS) can be seen                                                                                                                                                                                                                          | . 36                                                                                                                                                                                                                                                                                                                                                                                                                                         |

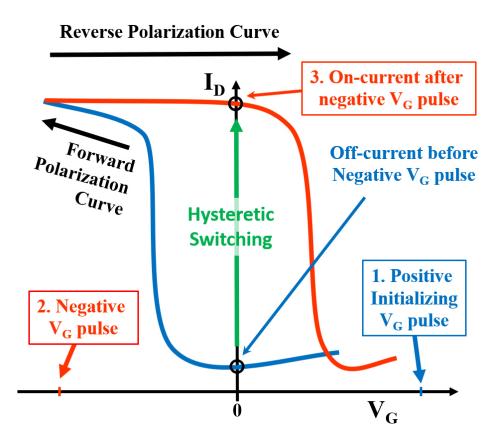

| Polarization switching in a ferroelectric oxide. Positive initialization assures the device to follow the forward polarization curve. Subsequent negative $V_G$ pulses with various pulse widths and levels cause polarization switching.                                                                                                                                                                   | . 37                                                                                                                                                                                                                                                                                                                                                                                                                                         |

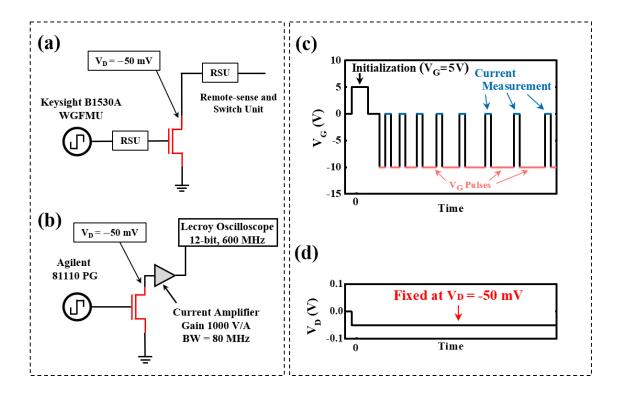

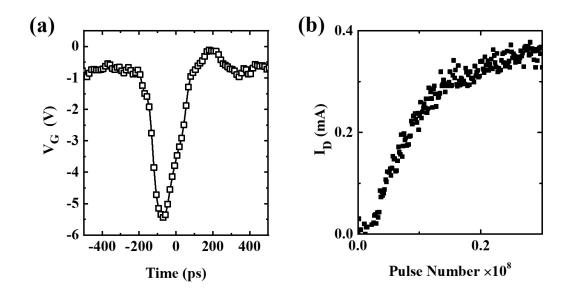

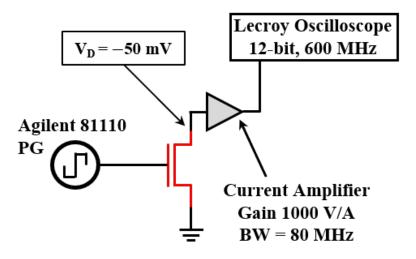

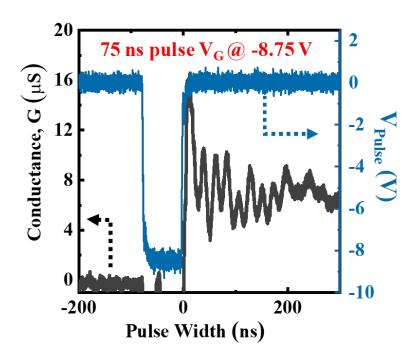

| (a) Measurement set-up used for pulse measurement on Ge FeFET. Wave-<br>form generator that generates pulses down to approximately 100 ns at<br>maximum of -5 V was used for low voltage measurements. (b) Ultrafast<br>measurement set-up for pulses as short as 3.6 ns and pulse level down to<br>-10 V. (c) and (d) show the pulses that were delivered to the gate and<br>drain of FeFETs, respectively | . 38                                                                                                                                                                                                                                                                                                                                                                                                                                         |

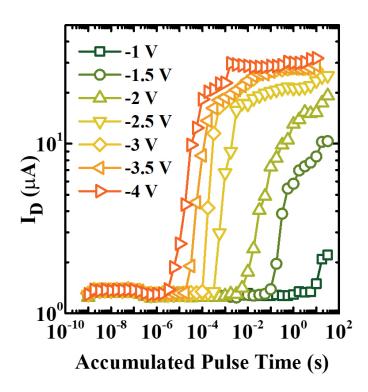

| Change in drain currents due to polarization switching using the low volt-<br>age set-up shown in Fig. 2.19 (a). Voltage level and pulse time was varied<br>and drain current was monitored after each pulse                                                                                                                                                                                                | . 39                                                                                                                                                                                                                                                                                                                                                                                                                                         |

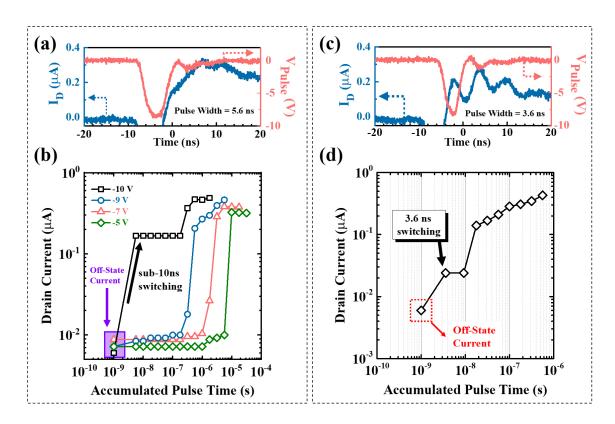

| (a) With a 5.6 ns gate pulse, drain current shows abrupt increase from the off-state. (b) As pulse time accumulates, the drain current continuously increases until it maximizes.                                                                                                                                                                                                                           | . 40                                                                                                                                                                                                                                                                                                                                                                                                                                         |

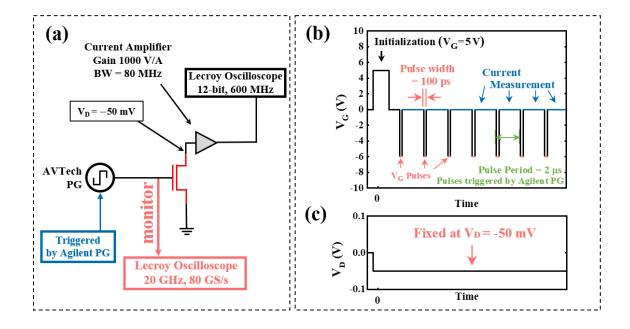

| (a) Measurement set-up used for generation and measurement of sub-<br>nanosecond pulses. (b) and (c) show the $V_G$ and $V_D$ profiles during the<br>measurement.                                                                                                                                                                                                                                           | . 41                                                                                                                                                                                                                                                                                                                                                                                                                                         |

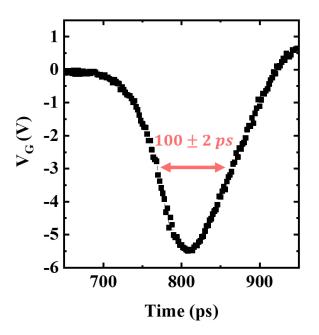

| (a) Measurement set-up used for generation and measurement of sub-<br>nanosecond pulses. (b) and (c) show the $V_G$ and $V_D$ profiles during the<br>measurement.                                                                                                                                                                                                                                           | . 42                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| More accurate measurement of generated 100 ps pulse with sampling scop                                                                                                                                                                                                                                                                                                                                      | e. 42                                                                                                                                                                                                                                                                                                                                                                                                                                        |

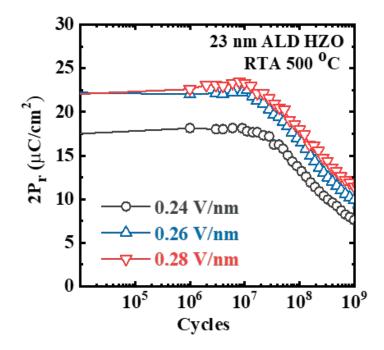

| Extracted remnant polarization $(P_r)$ using the typical Positive-up Negative-<br>down (PUND) measurement.                                                                                                                                                                                                                                                                                                  | . 44                                                                                                                                                                                                                                                                                                                                                                                                                                         |

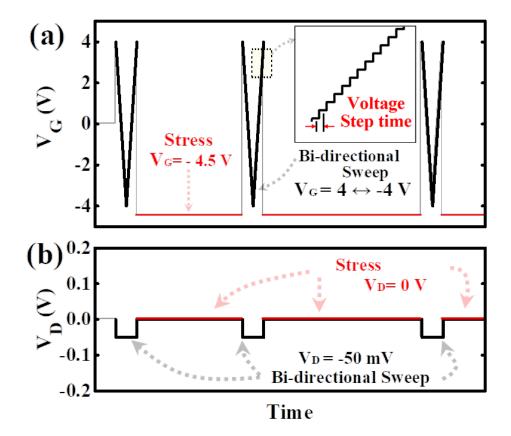

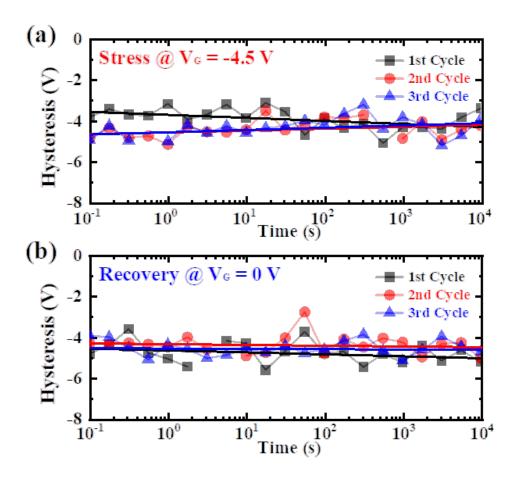

| Applied (a) $V_G$ and (b) $V_D$ versus time during the negative $V_G$ stress cycles. $V_G$ is kept at 0 V during recovery cycles                                                                                                                                                                                                                                                                            | . 45                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Hysteresis ( $V_{T,forward}$ - $V_{T,reverse}$ ) trend during 3 cycles (10 <sup>4</sup> seconds per cycle) of (a) negative stress and (b) recovery. $V_T$ was extracted from constant $I_D = 100 \text{ nA}/\mu\text{m.}$                                                                                                                                                                                   | . 46                                                                                                                                                                                                                                                                                                                                                                                                                                         |

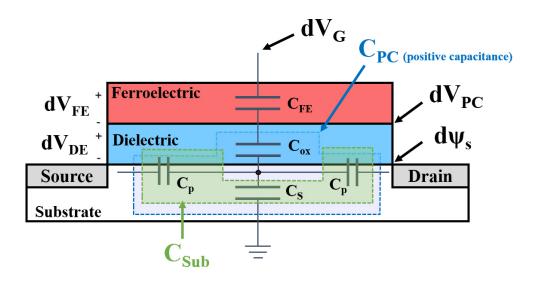

| Capacitance network in a NCFET.                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                             | Transfer curve $(I_D \cdot V_G)$ of a Ge FeFET at low $V_D = -50$ mV used for time<br>response study. Ferroelectric hysteresis of approximately -4 V (clockwise<br>for PMOS) can be seen Polarization switching in a ferroelectric oxide. Positive initialization as-<br>sures the device to follow the forward polarization curve. Subsequent<br>negative $V_G$ pulses with various pulse widths and levels cause polarization<br>switching |

| :   |

|-----|

| XIV |

|     |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

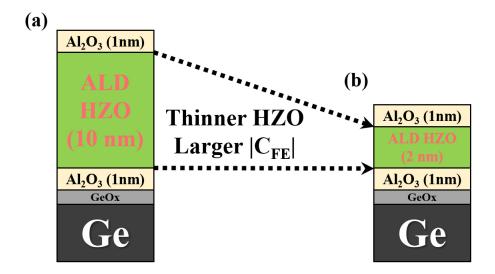

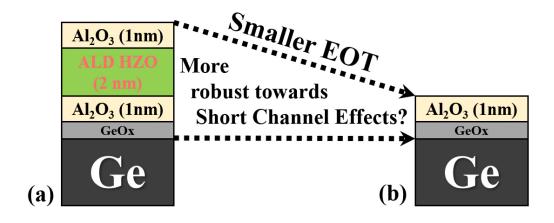

| 3.2  | (a) Germanium FeFET with large voltage hysteresis fabricated in the pre-<br>vious section. (b) HZO can be thinned down to obtain the stabilized con-<br>dition for hysteresis-free and sub-60mV/dec operation by accessing the<br>benefits of NCFET                                                                                                                                                                                                              | . 49 |

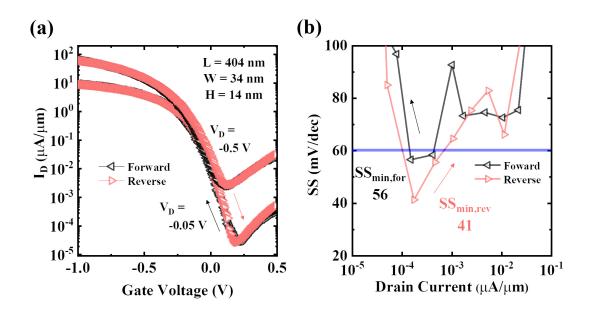

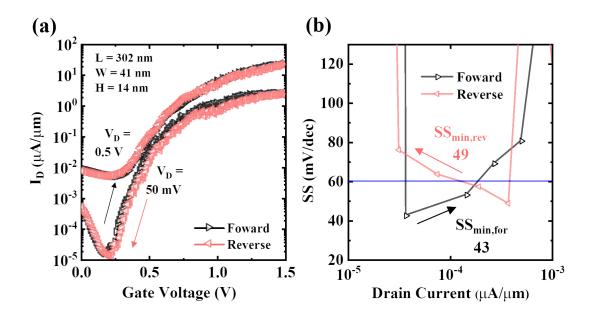

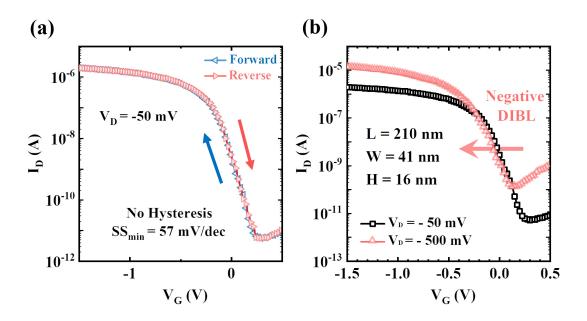

| 3.3  | (a) Transfer curve of a germanium NC pFinFET. Forward and reverse sweep are both shown at two different $V_D$ values. (b) Extracted SS as a function of drain current.                                                                                                                                                                                                                                                                                           | . 50 |

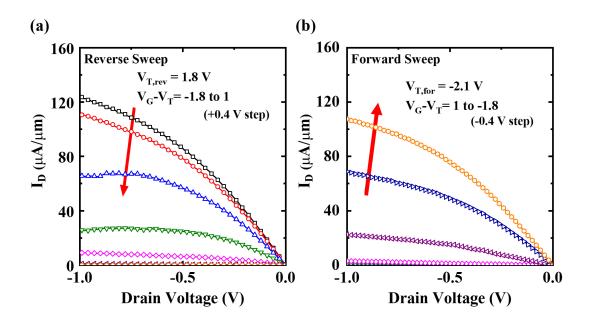

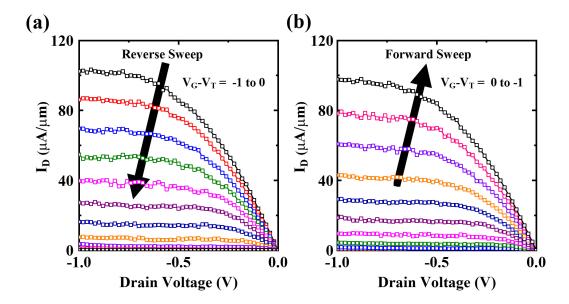

| 3.4  | Output curves $(I_D-V_D)$ swept in the (a) reverse and (b) forward direction. $V_G-V_T$ was swept from -1 to 0 V for the reverse sweep and 0 to -1 for the forward sweep.                                                                                                                                                                                                                                                                                        | . 50 |

| 3.5  | (a) Hysteresis-free transfer curve of a germanium NC nFinFET swept in<br>both forward and reverse direction at two different drain voltages. (b)<br>Extracted SS as a function of drain current.                                                                                                                                                                                                                                                                 | . 53 |

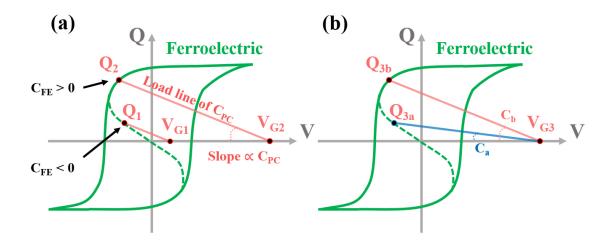

| 3.6  | Stabilization of NC within the gate stack can be realized with a series-<br>connected positive capacitance $(C_{PC})$ represented as load lines. (a) Larger $V_G$ ( $V_{G2} > V_{G1}$ ) will push the Q-point out of $C_{FE} < 0$ region. (b) Larger $C_{PC}$ will also push the Q-point out of NC regime                                                                                                                                                        |      |

| 3.7  | Reported studies discussing the negative DIBL stemming from the nature<br>of NC in ferroelectric oxide. (a) and (b) show negative DIBL due to<br>increase voltage drop across ferroelectric oxide [51]. (c) and (d) show the<br>effect of fringing capacitance with channel length scaling in a NCFET.<br>Shorter channel length increases the dominance of $C_{fr}$ within the gate<br>stack and the drain's coupling through $C_{fr}$ to the NC increases [52] |      |

| 3.8  | Potential distribution from source via channel to drain in a (a) conven-<br>tional FET and (b) NCFET. In NCFET, with an increase in $V_D$ , negative<br>(reverse) DIBL can be observed [42], [51]                                                                                                                                                                                                                                                                |      |

| 3.9  | Gate stacks of (a) germanium NC FinFETs and (b) reported germanium FinFETs using the same fabrication process and equipment [15]                                                                                                                                                                                                                                                                                                                                 | . 57 |

| 3.10 | (a) Transfer curves showing negligible hysteresis and sub-60mV/dec SS measured from one of the germanium NC pFinFETs. (b) Negative DIBL can also be seen where higher drain voltage increased the $V_T$ instead of reducing it as in typical DIBL                                                                                                                                                                                                                |      |

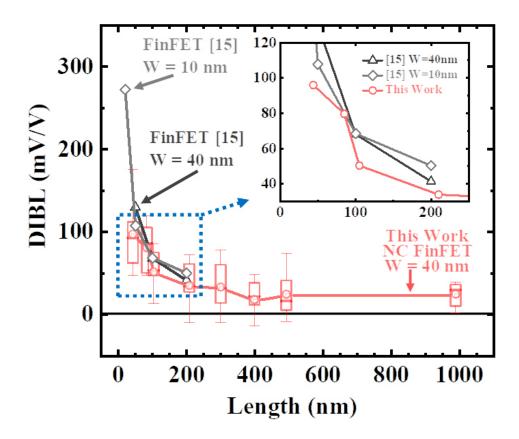

| 3.11 | DIBL as a function of channel length for both NCFETs and reference<br>devices [15] show increasing DIBL with length scaling. However, inset<br>graph which enlarges the blue-boxed region shows that NCFETs have<br>smaller DIBL than reference devices                                                                                                                                                                                                          | . 58 |

xv

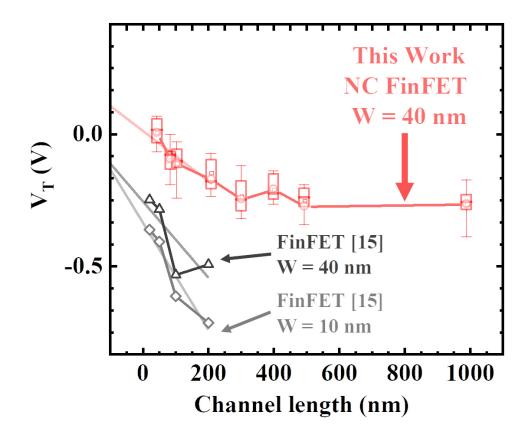

| 3.12 | Extracted $V_T$ monitored with scaling channel lengths of NC FinFETs and<br>reported conventional FinFETs [15]. $V_T$ roll-off is less severe as seen from<br>linear-fitted lines under L = 200 nm regime                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.13 | SS as a function of channel length in NCFETs and reference devices [15].<br>SS was reduced significantly in NCFETs. SS levels that go sub-60 mV/dec<br>limit in NC FinFETs can be visible                                                                                                                   |

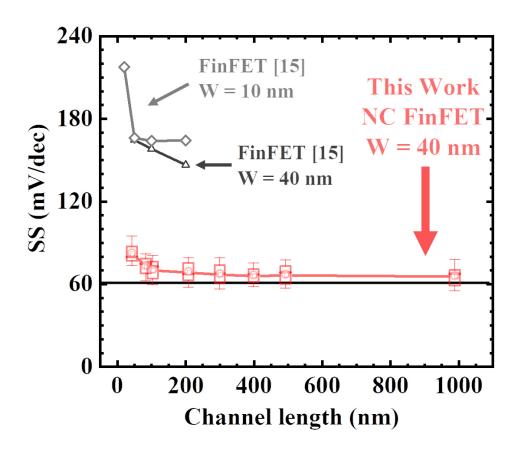

| 3.14 | <ul><li>(a) Minimum developed trench from direct e-beam lithography (VISTEC VB6) using ZEP 2.4 e-beam resist.</li><li>(b) Top view of the trench 61</li></ul>                                                                                                                                               |

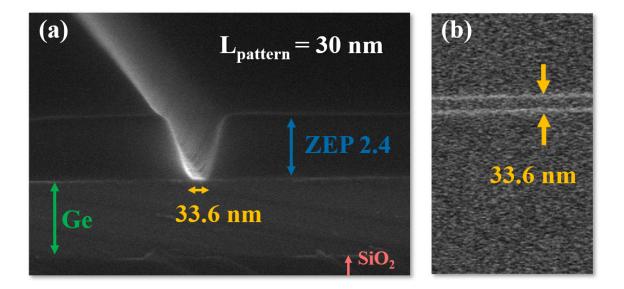

| 3.15 | Germanium dry etch profile with identical $SF_6$ recipe. Etch test on patterned trench window for (a) 20 seconds and (b) 35 seconds. (c) Etch test on GeOI wafer without forming etch window. Etch rate without etch window shows significantly higher rate                                                 |

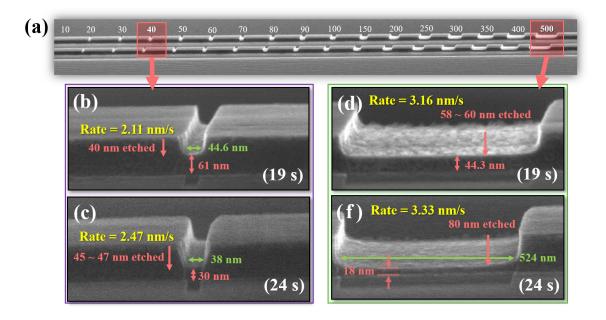

| 3.16 | (a) Etched Ge trench with different etch window ranging from 20 to 500 nm. (b) and (c) show etched profile of 40 nm long trench after 19 seconds and 24 seconds of etching, respectively. (d) and (f) are the etched profile of 500 nm long trench. Note that larger etch windows have higher etch rate. 63 |

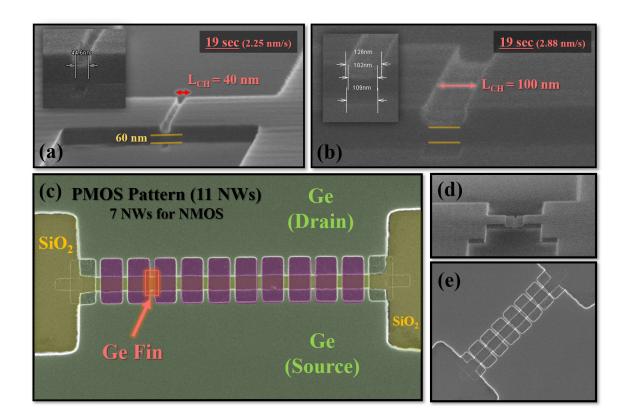

| 3.17 | SEM images after channel length of (a) 40 nm and (b) 100 nm were defined.<br>Etch rate is consistent with values from Table 3.2. (c) Top-view of false-<br>colored SEM image after the fin definition with the same $SF_6$ dry etching.<br>(d) and (e) show views from different angles                     |

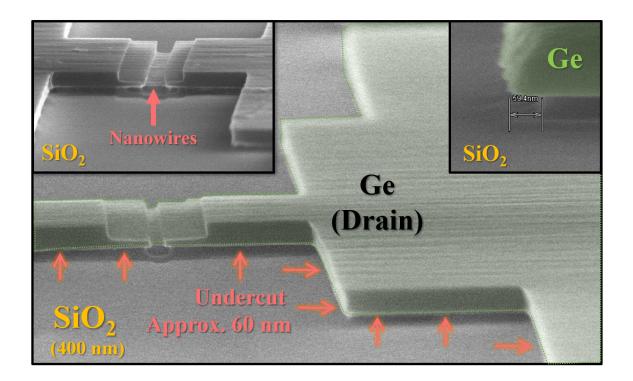

| 3.18 | False-colored SEM images after nanowire release with HF (4 %) cyclic etching. Undercut of approximately 60 nm is visible                                                                                                                                                                                    |

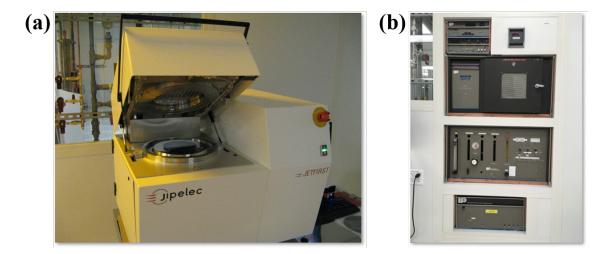

| 3.19 | (a) Jipelec rapid thermal annealing machine. (b) Branson plasma etching system $(Ar/O_2)$                                                                                                                                                                                                                   |

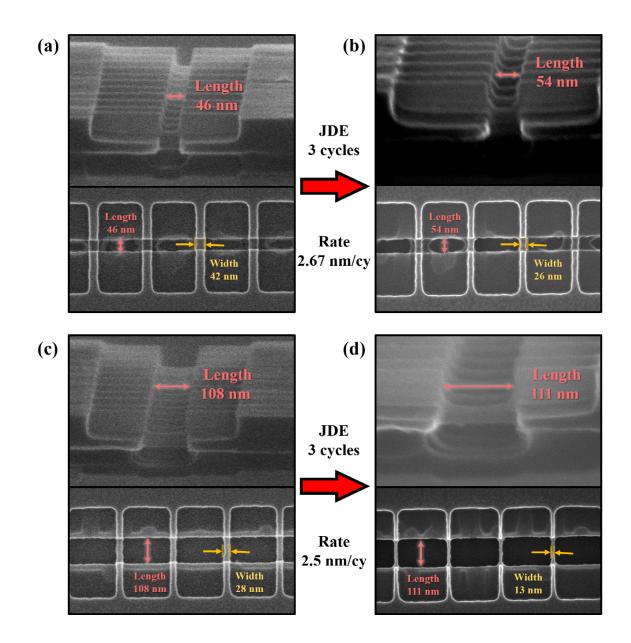

| 3.20 | SEM images of germanium nanowires $(L = 46 \text{ nm}, W = 42 \text{ nm})$ (a) before<br>and (b) after 3 cycles of Jipelec digital etching (JDE). Another nanowire<br>(L = 108  nm, W = 28  nm) is shown (c) before and (d) after the same JDE<br>process                                                   |

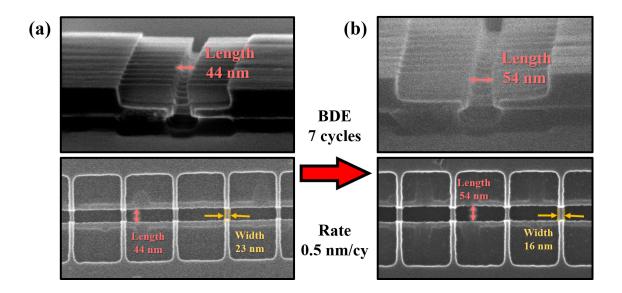

| 3.21 | SEM images of germanium nanowires $(L = 44 \text{ nm}, W = 23 \text{ nm})$ (a) before<br>and (b) after 3 cycles of Branson digital etching (BDE). The etch rate for<br>BDE is more precise than JDE in Fig. 3.20                                                                                            |

| 4.1  | An artistic interpretation of synapses and neurons in human brain [100] 70                                                                                                                                                                                                                                  |

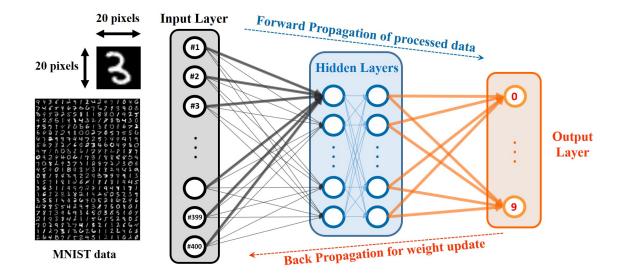

| 4.2  | A brief network schematic of a deep neural network (DNN) with 400 input neurons, 10 output neurons and 2 hidden layers                                                                                                                                                                                      |

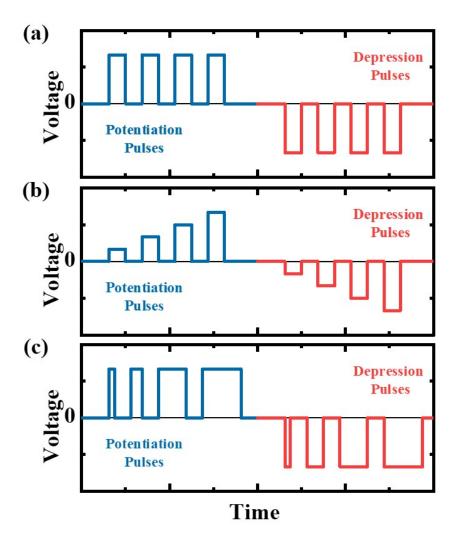

| 4.3  | Various possible update pulses for e-NVM synaptic devices. (a) Identical pulses, (b) Variable pulse levels and (c) variable pulse widths                                                                                                                                                                    |

| Figure                                                                                                          |                                                                                                                         | age                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                 |                                                                                                                         | 75                                                                                                                      |

| step # 7 in Table 4.1. Top view SEM images after step # 12 in Table 4.1                                         |                                                                                                                         | 76                                                                                                                      |

|                                                                                                                 |                                                                                                                         | 76                                                                                                                      |

| Measurement set-up for real time conductance update probing                                                     |                                                                                                                         | 77                                                                                                                      |

|                                                                                                                 |                                                                                                                         | 77                                                                                                                      |

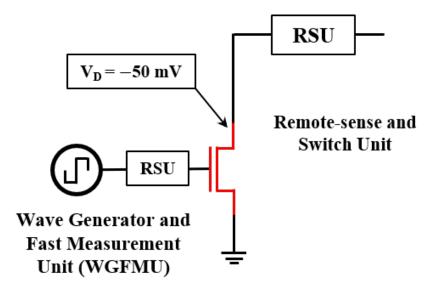

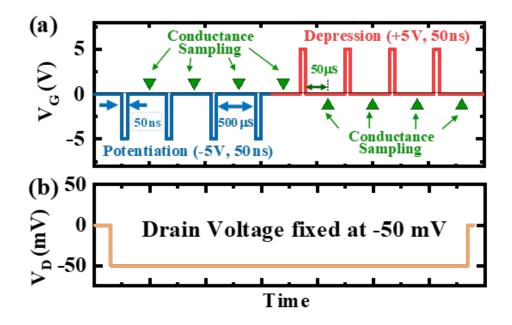

| Measurement set-up for optimization of consecutive potentiation and de-<br>pression using fast measurement unit |                                                                                                                         | 78                                                                                                                      |

| - • • • • • • • • • • • • • • • • • • •                                                                         |                                                                                                                         | 79                                                                                                                      |

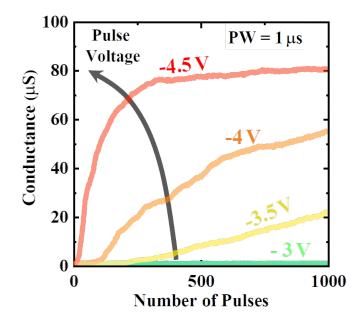

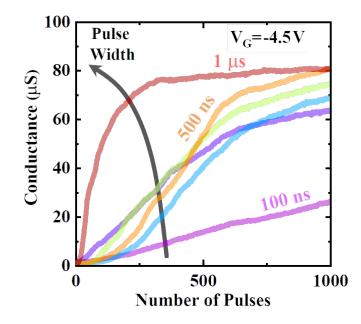

| Potentiation profile with fixed $V_G = -4.5$ V but varying pulse widths.                                        |                                                                                                                         | 79                                                                                                                      |

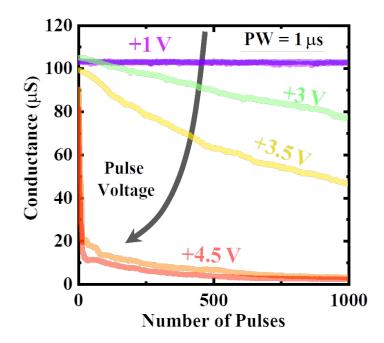

| Depression profiles with fixed pulse width of 1 $\mu$ s                                                         |                                                                                                                         | 80                                                                                                                      |

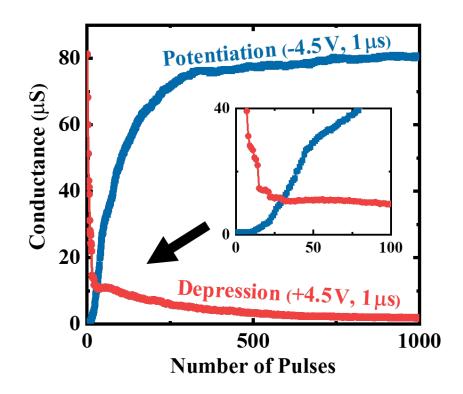

|                                                                                                                 |                                                                                                                         | 81                                                                                                                      |

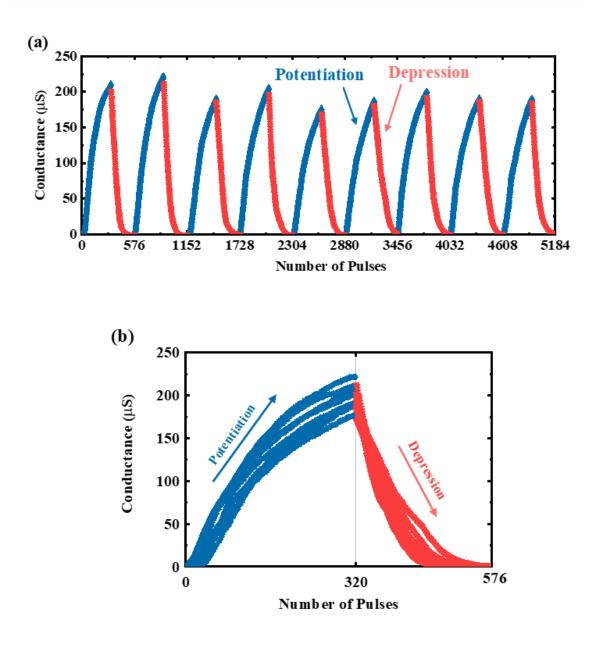

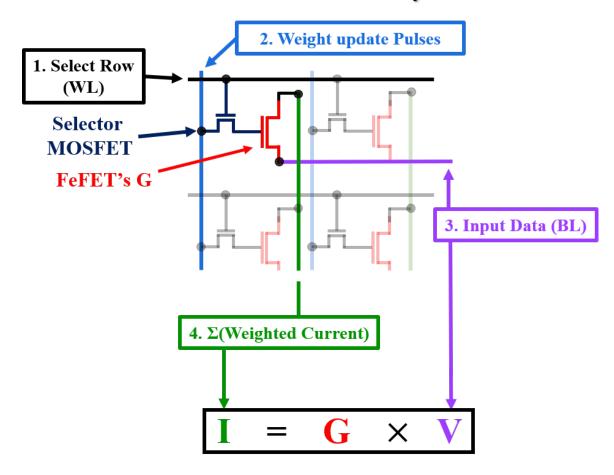

| pulses for the fabricated Ge FE pNWFET (L = 105 nm, W = 32 nm, H                                                |                                                                                                                         | 82                                                                                                                      |

| tiation (-5 V, 50 ns, 320 pulses) and depression (+5 V, 50 ns, 256 pulses).                                     |                                                                                                                         | 8/                                                                                                                      |

|                                                                                                                 |                                                                                                                         |                                                                                                                         |

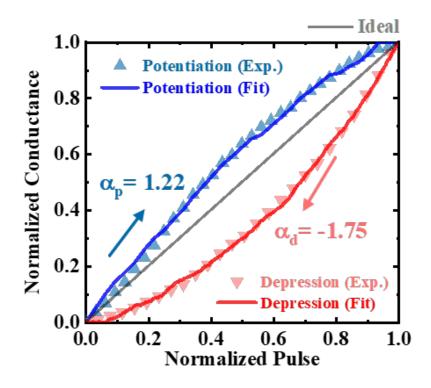

| Curve fitting procedure using MATLAB to extract A coefficients for po-                                          |                                                                                                                         |                                                                                                                         |

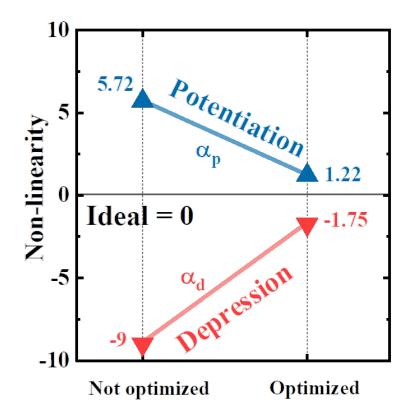

| imentally measured conductance profiles. $\alpha_p = 1.22$ and $\alpha_d = -1.75$ give                          |                                                                                                                         | 88                                                                                                                      |

| tance profiles acquired using optimized (Fig. 4.18) and not optimized                                           |                                                                                                                         | 89                                                                                                                      |

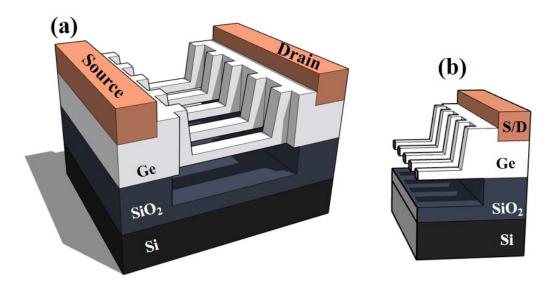

|                                                                                                                 | (a) 3D structure of the Ge synaptic nanowire device. (b) Cross-sectional view of nanowires before step # 7 in Table 4.1 | (a) 3D structure of the Ge synaptic nanowire device. (b) Cross-sectional view of nanowires before step # 7 in Table 4.1 |

| Figure                                                                                                                                                                                                                                                                                           |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

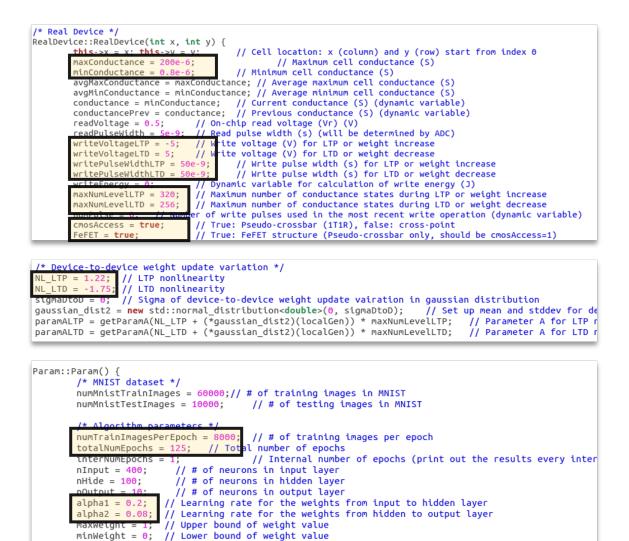

| 4.20 Major parameters that needs to be updated in the simulation code                                                                                                                                                                                                                            | . 90 |

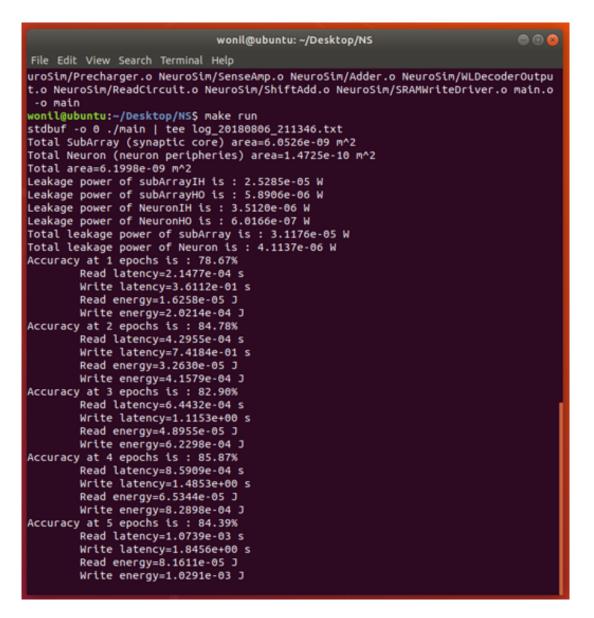

| 4.21 Screenshot taken in the middle of running the online learning simulation.                                                                                                                                                                                                                   | . 91 |

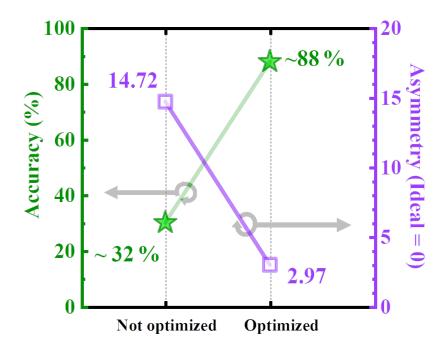

| 4.22 Improvement in simulation accuracy after 125 epochs of training totalling<br>1 million MNIST images (cropped to 20 by 20 pixels)                                                                                                                                                            | . 92 |

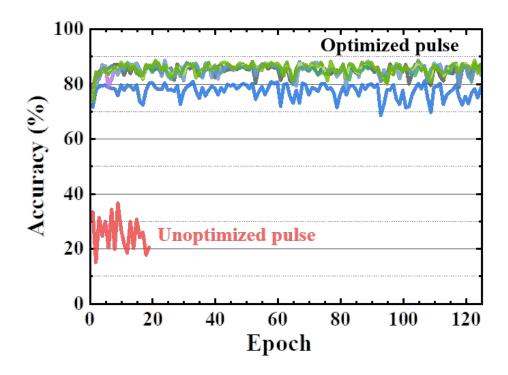

| 4.23 Simulated online learning accuracy throughout 125 epochs of training 1<br>million MNIST dataset. Various combinations of learning rates $\alpha_1$ , $\alpha_2$<br>were tested for conductance profile acquired using the optimized pulse.<br>Un-optimized pulse (red) yields low accuracy. | . 94 |

## SYMBOLS

| $\alpha_p$   | Potentiation non-linearity coefficient |

|--------------|----------------------------------------|

| $lpha_d$     | Depression non-linearity coefficient   |

| C            | Capacitance                            |

| $C_{ox}$     | Oxide capacitance                      |

| $C_p$        | Parasitic capacitance                  |

| $C_{fr}$     | Fringing capacitance                   |

| $C_{eff}$    | Effective capacitance                  |

| $C_{FE}$     | Ferroelectric capacitance              |

| $C_{PC}$     | Positive capacitance                   |

| $C_S$        | Substrate capacitance                  |

| $D_{it}$     | Interface trap density                 |

| D            | Displacement field                     |

| $E_C$        | Coercive field                         |

| $E_F$        | Fermi Level                            |

| $E_i$        | Intrinsic fermi level                  |

| $\epsilon_r$ | Relative permittivity                  |

| $g_m$        | Transconductance $(dI_D/dV_G)$         |

| $g_{max}$    | Maximum transconductance               |

| G            | Conductance                            |

| $G_{max}$    | Maximum conductance                    |

| $G_{min}$    | Minimum conductance                    |

| $H_{NW}$     | Nanowire height                        |

| IC           | Integrated circuit                     |

| $I_G$        | Gate leakage current                   |

| $I_{OFF}$      | Off current                                       |

|----------------|---------------------------------------------------|

| $I_{ON}$       | On current                                        |

| $J_G$          | Gate leakage current density                      |

| k              | dielectric constant                               |

| $k_B$          | Boltzmann constant                                |

| $l_0$          | Critical length                                   |

| $L_{NW}$       | Nanowire length                                   |

| $\lambda$      | Mean free path                                    |

| $\mu$          | Carrier mobility                                  |

| $ ho_C$        | Contact resistivity                               |

| $\psi_s$       | Surface potential                                 |

| P              | Polarization                                      |

| $P_r$          | Remnant polarization                              |

| q              | Elementary charge                                 |

| Q              | Charge                                            |

| R              | Resistance or Channel back scattering coefficient |

| $R_S$          | Source series resistance                          |

| $R_{SD}$       | Source/Drain resistance                           |

| $R_{sh}$       | Sheet resistance                                  |

| $R_D$          | Drain series resistance                           |

| T              | Transmission coefficient                          |

| $V_D$          | Drain voltage                                     |

| $V_{DD}$       | CMOS drive voltage                                |

| $V_{FB}$       | Flat band voltage                                 |

| $V_{FE}$       | Voltage across ferroelectric oxide                |

| $V_G$          | Gate voltage                                      |

| $v_{inj}$      | Source injection velocity                         |

| $V_T (V_{TH})$ | Threshold voltage                                 |

| $W_{NW}$       | Nanowire width                                    |

- $W_{SB}$  Schottky barrier width

- U Gibbs free energy

- $\chi$  Electric susceptibility

## ABBREVIATIONS

xxi

| ALD        | Atomic Layer Deposition                 |

|------------|-----------------------------------------|

| AM         | Accumulation Mode                       |

| $BE_{sat}$ | Saturation Ballistic Efficiency         |

| BDE        | Branson Digital Etching                 |

| BJT        | Bi-polar Junction Transistor            |

| BOX        | Buried Oxide                            |

| CMOS       | Complementary Metal Oxide Semiconductor |

| CNL        | Charge Neutrality Level                 |

| DIBL       | Drain Induced Barrier Lowering          |

| DNN        | Deep Neural Network                     |

| e-NVM      | Emerging Nonvolatile Memory             |

| EOT        | Equivalent Oxide Thickness              |

| FeFET      | Ferroelectric Field Effect Transistor   |

| FeRAM      | Ferroelectric Random Access Memory      |

| FinFET     | Fin Field Effect Transistor             |

| FLP        | Fermi Level Pinning                     |

| GAA        | Gate All-Around                         |

| GeOI       | Germanium on Insulator                  |

| HKMG       | High-k Metal Gate                       |

| ICP        | Inductive-coupled plasma                |

| IM         | Inversion Mode                          |

| JDE        | Jipelec Digital Etching                 |

| JLFET      | Junctionless FET                        |

| L-K        | Landau-Khalatnikov                      |

| MIGS          | Metal Induced Gap States                                   |

|---------------|------------------------------------------------------------|

| MLP           | multilayer perceptron                                      |

| MOSFET        | Metal-Oxide-Semiconductor Field Effect Transistor          |

| MRAM          | Magnetic Random Access Memory                              |

| NBTI          | Negative Bias Temperature Instability                      |

| NC            | Negative Capacitance                                       |

| NCFET         | Negative Capacitance Field Effect Transistor               |

| NDR           | Negative Differential Resistance                           |

| NW            | Nanowire                                                   |

| NWFET         | Nanowire Field Effect Transistor                           |

| PBTI          | Positive Bias Temperature Instability                      |

| PCM           | Phase Change Memory                                        |

| PCRAM         | Phase Change Random Access Memory                          |

| PDA           | Post Deposition Annealing                                  |

| PMA           | Post Metallization Annealing                               |

| PG            | Pulse Generator                                            |

| RRAM          | Resistive Random Access Memory                             |

| RSU           | Remote-sense and Switch Unit                               |

| RTA           | Rapid Thermal Annealing                                    |

| SBH           | Schottky Barrier Height                                    |

| SCE           | Short Channel Effect                                       |

| SEM           | Scanning Electron Microscope                               |

| S/D           | Source and Drain                                           |

| SOI           | Silicon-on-Insulator                                       |

| $\mathbf{SS}$ | Subthreshold Slope (or Subthreshold Swing)                 |

| TCAD          | Technology Computer-Aided Design                           |

| TNL           | Trap Neutrality Level                                      |

| TLM           | Transfer Length Measurement (or Transmission Line Measure- |

|               | ment)                                                      |

- WGFMU Waveform Generator and Fast Measurement Unit

- XPS X-ray Photoelectron Spectroscopy

- XRD X-ray diffraction

#### ABSTRACT

Chung, Wonil Ph.D., Purdue University, December 2019. Integration of Ferroelectricity into Advanced 3D Germanium MOSFETs for Memory and Logic Applications. Major Professor: Peide D. Ye.

Germanium-based MOS device which is considered as one of the promising alternative channel materials has been studied with well-known FinFET, nanowire structures and HKMG (High-k metal gate). Recent introduction of ferroelectric (FE) Zr-doped HfO<sub>2</sub> (Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub>, HZO) has opened various possibilities both in memory and logic applications.

First, integration of FE HZO into the conventional Ge platform was studied to demonstrate Ge FeFET. The FE oxide was deposited with optimized atomic layer deposition (ALD) recipe by intermixing  $HfO_2$  and  $ZrO_2$ . The HZO film was characterized with FE tester, XRD and AR-XPS. Then, it was integrated into conventional gate stack of Ge devices to demonstrate Ge FeFETs. Polarization switching was measured with ultrafast measurement set-up down to 100 ps.

Then, HZO layer was controlled for the first demonstration of hysteresis-free Ge negative capacitance (NC) CMOS FinFETs with sub-60mV/dec SS bi-directionally at room temperature towards possible logic applications. Short channel effect in Ge NCFETs were compared with our reported work to show superior robustness. For smaller widths that cannot be directly written by the e-beam lithography tool, digital etching on Ge fins were optimized.

Lastly, Ge FeFET-based synaptic device for neuromorphic computing was demonstrated. Optimum pulsing schemes were tested for both potentiation and depression which resulted in highly linear and symmetric conductance profiles. Simulation was done to analyze Ge FeFET's role as a synaptic device for deep neural network.

### 1. INTRODUCTION

#### 1.1 Devices with higher performance: Scaling

It is not enough to emphasize the importance of semiconductor technology in modern society since it has tremendously influenced all aspects of human lives. Introduction of Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) has replaced its predecessor, the Bi-polar Junction Transistors (BJT). Integration of Silicon platform with exponential technological advance in fabrication process yielded in unprecedented leap in processing capability of modern CPUs and memory devices. Abiding by the famous Moore's law, density of transistor has doubled approximately every 2 years reaching hundreds of millions per  $mm^2$  as shown in Fig. 1.1 [1].

Until now, the performance upgrades were possible mainly by scaling down the device sizes. Channel length, gate oxide thickness, implantation depths and other various device parameters were scaled down to yield higher on-current, better gate controllability and thus better performance metrics. With smaller physical dimensions, various non-ideal effects such as short-channel effects or increased leakage currents became problematic.

#### 1.2 Alternative channel material: Germanium and its challenge

Faced with the physical limitations in device dimensions, More than Moore (MtM) strategies are being discussed nowadays to continue the legacy of the successful guideline in the upcoming years [2–4]. Evidently, scaling alone cannot serve as the only winning strategy. Another aspect that needs to be considered is possibility of incorporating different materials into conventional silicon platform. Silicon has been successfully serving the microelectronic industry ever since its emergence, but it is not widely known that the first transistor developed in 1948 at Bell Labs were based on germanium substrate [5]. However due to its inferior interface quality and difficulties in fabrication processes, germanium was not used for the mainstream industries.

Fortunately, germanium is equipped with superior electron and hole (electron: 1900  $cm^2/V \cdot s$ , hole: 3900  $cm^2/V \cdot s$ ) mobility than Silicon (electron: 1500  $cm^2/V \cdot s$ , hole: 450  $cm^2/V \cdot s$ ). Therefore, if appropriate fabrication and implementation strategies could be developed, germanium transistor might have its chance to exhibit better performance than the conventional silicon devices. It is also noteworthy to mention that silicon and germanium both are in the same group IV (periodic table) which gives

Fig. 1.1. Transistor density with respect to year. Density calculation is based on Mark Bohr's proposed method in Intel's 2017 Technology and Manufacturing day [1].

higher process compatibility within the current mainstream CMOS process technology.

However, there are several issues that must be resolved for germanium to show off its advantages such as high-quality contact formation, stable gate stack formation with good interface quality and integration of afore-mentioned technologies into a single working device without compromising the each other.

#### **1.2.1** Interface Engineering: Gate stack

Unlike the blessed SiO<sub>2</sub> which is a perfect material as a gate insulator on Si substrate (excellent insulator, high break down field, well-studied oxidation behavior and low interface trap density with Si), germanium oxide (GeO<sub>2</sub>) is not only volatile beyond certain temperature (~ 430 °C) [6,7] but also hygroscopic [8]. GeO<sub>2</sub> reacts with Ge in the interface through redox reaction ( $GeO_2 + Ge = 2GeO$ ) and GeO (g) diffuses through GeO<sub>2</sub> [6]. Diffusion of GeO (g) into the high-k oxide is not preferred since it degrades the overall gate stack's performance in terms of leakage current and EOT (Equivalent oxide thickness). Furthermore the dielectric constant of GeO<sub>2</sub> is not high enough (approximately 4 ~ 6 [9,10]) when compared to widely used high-k dielectrics (> 20). Therefore, it is important to form a stable gate stack that would not deteriorate the gate stack but still yield decent EOT and interface quality.

Although it is possible to achieve extreme EOT (~ 0.6 nm) using GeO<sub>x</sub>-free gate stack [11], more widely adapted strategy in forming the gate oxide stack in germanium transistors is inserting ultrathin GeO<sub>x</sub> layer in between the Ge channel and the main gate dielectric (usually high-k oxide) through post-oxidation [12, 13]. With superior interface quality, gate stacks with ultrathin GeO<sub>x</sub> layer has proven to show good device performances [14–16]. Based on the common goal of improving the overall gate stack's performance, various oxides were integrated into germanium devices such as HfO<sub>2</sub>, ZrO<sub>2</sub>, Y, Y<sub>2</sub>O<sub>3</sub>, YScO<sub>3</sub>, La<sub>2</sub>O<sub>3</sub> and LaLuO<sub>3</sub> [11, 16–22]. Also various integration methods such as vacuum annealing [11], Si interfacial layer passivation [23–25], Ge

Fig. 1.2. Schottky barrier heights (SBH) extracted from n-Si and n-Ge versus various metal work functions. In case of n-Ge, strong pinning effect can be seen [32].

(oxy)nitridation [26, 27], sulfur passivation [28, 29], high pressure  $O_2$  oxidation and plasma (or  $O_3$ ) post oxidation (PPO or OPO) [16, 30] were studied for improved results.

#### 1.2.2 Contact Engineering: Source and Drain

Contact engineering is also a critical part in germanium devices due to inferior metal-nGe contact arising from strong fermi level pinning (FLP). In metal-nGe contact, the location of charge neutrality level (CNL) is only 0.1 eV above the valence band edge and the pinning factor (S) is extracted to be only 0.05 [31–33]. As shown in Fig. 1.2, even if various metals with different work functions are contacted with n-Ge, SBH is almost constant [32]. This results in degraded drain current due to high barrier in Ge NMOS. Exact mechanism behind fermi-level pinning is not clear yet but MIGS (metal induced gap states) or effect of electric dipole are thought to be the possible reasons behind it. MIGS theory claims that the decay of metal's electron wave function tail into the substrate causes the FLP and therefore inserting an insulating layer in between the metal and the germanium substrate is helpful in mitigating FLP since it pushes away the metal's electron wave function from the interface [32, 34]. It also implies that FLP should be weakly related to the interface characteristics as it is only caused by the incoming metal electron wave function. Another suspected origin for the FLP is the effect of electric dipole [35, 36]. By varying the interface dipole characteristics, it was reported that SBH was alleviated significantly [35].

One strategy to alleviate the FLP in metal-nGe junction is by reducing the barrier width as shown in Fig. 1.3 (a). Reducing the barrier width increases the tunneling efficiency instead of modulating the barrier height. Etching the top surface (approx. 12 nm) of nGe with BCl<sub>3</sub>/Ar based inductive-coupled plasma (ICP) etch recipe after ion implantation and making a contact at the recessed location helped enhance the contact properties. Sheet resistance ( $R_{SH}$ ) was found to be similar but contact resistance ( $R_C$ ) was reduced by approximately 80 % [37].

#### **1.3** Better performance: Lower power and steeper slope

Although the device dimension scaling has successfully served as an effective way to improve the device performances over the last few decades, it wasn't too efficient in reducing the supply voltage of the devices as shown in Fig. 1.4 (a), (b). Unfortunately, supply voltage ( $V_{DD}$ ) is directly related to the power consumption of the integrated circuit (IC) chips.

$$DynamicPower \propto C_{eff} \times V_{DD}^2 \times f \tag{1.1}$$

$$StaticPower \propto V_{DD}^2 \times I_{OFF} \tag{1.2}$$

Power consumption consists of 2 different powers (dynamic and static power) which can be expressed in (1.1) and (1.2) where  $C_{eff}$  is the effective capacitance, f

Fig. 1.3. (a) Recessed S/D structure enhances the electron tunneling efficiency by reducing barrier width ( $W_{SB}$ ) which lowers the resistivity. (b) IV curves from TLM pads before and after S/D recess etching on n-Ge. (c) Linear scale representation of (b). (d) Measured resistance from the TLM pattern (inset) with Ni-nGe contact [37].

is the working frequency of the chip and  $I_{OFF}$  is the off-current. The reason why the  $V_{DD}$  has not been scaled accordingly is related to the lower limit of subthreshold slope (SS) at room temperature.

Fig. 1.4. (a) Power density with respect technology node has increased rapidly. (b) Supply voltage was not scaled accordingly. Inset graph shows most recent trend in supply voltages.

Fig. 1.5. (a) In conventional devices, reducing the supply voltage results in exponential increase in  $I_{OFF}$  due to lower limit of SS (60 mV/dec at room temperature). As shown in (b), an ideal steep slope device exhibits lower SS (below 60 mV/dec at room temperature) and therefore can produce larger current with smaller voltage. (c) A simple capacitance network in a MOS transistor showing the body factor,  $d\Psi_S/dV_G$ .

The SS having the lower limit of 60 mV/dec at room temperature is often referred to as *Boltzmann's tyranny* because no matter how the transistor was fabricated, the absolute minimum SS can't be further scaled below the limit as long as the transistor operates under the thermionic-emission-based-MOS mechanism. In other words, if the slope is stuck at certain value, it is impossible to suppress the  $I_{OFF}$  increase with respect to reduction in operating voltage as shown in Fig. 1.5 (a). The goal of steep-slope devices would to result in a transfer curve as depicted in Fig. 1.5 (b). A simple capacitance network in a typical MOS transistor shown in Fig. 1.5 (c) includes  $\Psi_S$ ,  $C_S$  and  $C_{ox}$  which are surface potential, semiconductor capacitance and oxide capacitance, respectively. SS then can be expressed as,

$$SS = m \times n = \left[ \left( \frac{d\Psi_S}{dV_G} \right) \times \left( \frac{dlog_{10}I_D}{d\Psi_S} \right) \right]^{-1}$$

(1.3)

$$m = \left(\frac{d\Psi_S}{dV_G}\right)^{-1} = \left(\frac{C_{ox}}{C_{ox} + C_S}\right)^{-1} = 1 + \frac{C_S}{C_{ox}} > 1$$

(1.4)

$$n = ln10 \times \frac{k_B T}{q} \approx 60 mV/dec \tag{1.5}$$