# SPINTRONIC DEVICES AND ITS APPLICATIONS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Mei-Chin Chen

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

May 2020

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Kaushik Roy, Chair

School of Electrical and Computer Engineering

Dr. Anand Raghunathan

School of Electrical and Computer Engineering

Dr. Vijay Raghunathan

School of Electrical and Computer Engineering

Dr. Zhihong Chen

School of Electrical and Computer Engineering

# Approved by:

Dr. Venkataramanan Balakrishnan

Head of the School Graduate Program

This thesis is dedicated to my family and friends.

#### ACKNOWLEDGMENTS

First and foremost, I would like to express my sincere gratitude to my Ph.D. advisor, Prof. Kaushik Roy, for his patient guidance, encouragement, and support throughout my doctoral studies at Purdue University. The inspiration he gave has played significant part in shaping me over the past several years. At every stage he has motivated and encouraged me whenever I felt down and lost. I appreciate him for countless insightful discussions which help me approach complex research problems and organize my thoughts clearly and efficiently. I am truly fortunate to have him as my advisor, his enthusiasm and instruction are pivotal in making this dissertation possible.

I would also like to thank all of my doctoral dissertation committee members, Prof. Anand Raghunathan, Porf. Vijay Raghunathan, and Prof. Zhihong Chen, for providing valuable comments and suggestions to improve my research.

This dissertation would not have been possible without the help and support of the senior colleagues in Nanoelectronics Research Lab (NRL, Purdue University). I would take this opportunity to acknowledge the tremendous help and inspiration I have received from Dr. Xuanyao Fong (National University Singapore) and Dr. Yusung Kim (Intel Corp.). They have helped me built fundamental knowledge of spintronic device physics as well as circuit design. I like to thank all the former members of NRL members, especially, Dr. Karthik Yogendra (IBM), Dr. Abhronil Sengupta (Penn State University), Dr. Yong Shim (Intel Corp.), Dr. Zubair AL Azim (Intel Corp.), Dr. Akhilesh Jaiswal (University of Southern California), Dr. Parami Wijesinghe (Intel Corp.), and Gopalakrishnan Srinivasan (MediaTek). I would also like to thank all the current NRL members for their support, especially, Saima Sharmin, Amogh Agrawal, Aayush Ankit, Bing Han, Minsuk Koo, Chankyu Lee, Efstathia Soufleri, and others I might have accidentally missed out.

Finally and most importantly, I would like to express my greatest gratitude to my parents for their endless love and everlasting support these years. Lastly, special thanks go to my sisters who bring joy to my life every single day.

# TABLE OF CONTENTS

|    |      |                 |                                                       | Page |

|----|------|-----------------|-------------------------------------------------------|------|

| LI | ST O | F TAB           | LES                                                   | . ix |

| LI | ST O | F FIGU          | URES                                                  | X    |

| ΑI | BSTR | ACT             |                                                       | xiv  |

| 1  | INT  | RODU            | CTION                                                 | 1    |

| 2  | BAS  | IC OP           | ERATION OF SPIN-BASED DEVICES                         | 5    |

|    | 2.1  | Two-T           | Terminal Magnetic Tunnel Junction                     | 5    |

|    |      | 2.1.1           | Tunneling Magnetoresistance Ratio (TMR)               | 8    |

|    |      | 2.1.2           | Spin-Transfer Torque (STT) and magnetization dynamics | 9    |

|    |      | 2.1.3           | Spin-Orbit Torque (SOT)                               | 11   |

|    | 2.2  | Latera          | al Spin Valve                                         | 12   |

|    | 2.3  | Magne           | etic Skyrmion                                         | 13   |

| 3  | DON  | MINO-S          | STYLE SPIN-ORBIT TORQUE-BASED SPIN LOGIC              | . 16 |

|    | 3.1  | Introd          | luction                                               | 16   |

|    | 3.2  | SOT I           | Based Domino Style Spin Logic                         | 17   |

|    |      | 3.2.1           | Preset (Set to Hard Axis)                             | . 19 |

|    |      | 3.2.2           | Evaluation                                            | 19   |

|    | 3.3  | Four-I          | Phase Pipelined SOT-DSL                               | 20   |

|    | 3.4  | Model           | ling and Simulation Frame Work                        | 22   |

|    | 3.5  | Result          | and Discussion                                        | 23   |

|    | 3.6  | Concl           | usion                                                 | 26   |

| 4  |      | CHE MI<br>NOTRA | EMORY DESIGN WITH MAGNETIC SKYRMIONS IN A LONG        |      |

|    | 4.1  | Introd          | luction                                               | 29   |

|    | 4 2  | Skyrm           | nion-based Memory                                     | 31   |

|   |      |         | Pa                                                            | age |

|---|------|---------|---------------------------------------------------------------|-----|

|   |      | 4.2.1   | Nucleation of a skyrmion (Write operation)                    | 32  |

|   |      | 4.2.2   | Motion of skyrmions (Shift operation)                         | 33  |

|   |      | 4.2.3   | Detection of the presence of a skyrmion (Read operation)      | 34  |

|   | 4.3  | Multi-  | bit Skyrmion Cell Design                                      | 36  |

|   | 4.4  | Array   | Organization                                                  | 40  |

|   | 4.5  | Exper   | imental Methodology                                           | 42  |

|   |      | 4.5.1   | Simulation framework                                          | 43  |

|   |      | 4.5.2   | Experimental setup                                            | 44  |

|   | 4.6  | Result  | s and Discussions                                             | 45  |

|   |      | 4.6.1   | Device and circuit level results                              | 45  |

|   |      | 4.6.2   | System level results                                          | 46  |

|   | 4.7  | Conclu  | usion                                                         | 50  |

| 5 |      |         | C SKYRMION FOR SPINTRONIC DEEP LEARNING SPIK-<br>ON PROCESSOR | 52  |

|   | 5.1  | Introd  | uction                                                        | 52  |

|   | 5.2  | Deep S  | Spiking Neural Networks                                       | 55  |

|   | 5.3  | Under   | lying Physics of the Proposed Spintronic Device               | 56  |

|   | 5.4  | Propo   | sed Device as Synapse and Neuron                              | 57  |

|   |      | 5.4.1   | Skyrmion-based synapse                                        | 57  |

|   |      | 5.4.2   | Skyrmion-based neuron                                         | 60  |

|   |      | 5.4.3   | All spin neuromorphic architecture                            | 62  |

|   | 5.5  | Simula  | ation Framework and Results                                   | 63  |

|   | 5.6  | Conclu  | usion                                                         | 66  |

| ĵ | ISIN | G CON   | MPUTATION BASED BI-PRIME FACTORIZATION                        | 68  |

|   | 6.1  | Introd  | uction                                                        | 68  |

|   | 6.2  | Ising r | model                                                         | 70  |

|   | 6.3  | Under   | lying physics of the proposed Ising cell                      | 72  |

|   |      | 6.3.1   | Device operation                                              | 76  |

|    |      |        |                                                                                     | Р | age |

|----|------|--------|-------------------------------------------------------------------------------------|---|-----|

|    |      | 6.3.2  | Modeling and Simulation                                                             |   | 78  |

|    | 6.4  | Proble | em mapping and results                                                              |   | 81  |

|    |      | 6.4.1  | Neighboring and external interactions of biprime factorization in Ising formulation |   | 84  |

|    | 6.5  | Conclu | ısion                                                                               |   | 87  |

| 7  | SUM  | IMARY  | ,<br>                                                                               |   | 88  |

| RI | EFER | ENCES  | 5                                                                                   |   | 90  |

| VI | ТА   |        |                                                                                     |   | gg  |

# LIST OF TABLES

| Tabl | le                                                                                                                                                                                                                                             | Pa | age |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 3.1  | SOT-DSL parameters                                                                                                                                                                                                                             |    | 28  |

| 4.1  | Comparison of high- $K$ materials used in the present simulations                                                                                                                                                                              |    | 34  |

| 4.2  | Read voltage difference between the read MTJ and the reference MTJ without the presence of a skyrmion for different nanotrack width and the corresponding skyrmion radius. The reliable spacing between consecutive skyrmions is also compared |    | 36  |

| 4.3  | Bias voltage conditions for various operations                                                                                                                                                                                                 |    | 38  |

| 4.4  | Material parameters used for simulation                                                                                                                                                                                                        |    | 44  |

| 4.5  | System configuration                                                                                                                                                                                                                           |    | 45  |

| 5.1  | Material parameters used in simulation                                                                                                                                                                                                         |    | 65  |

| 6.1  | Material parameters used in simulation                                                                                                                                                                                                         |    | 80  |

# LIST OF FIGURES

| Figu | ire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pa | age |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

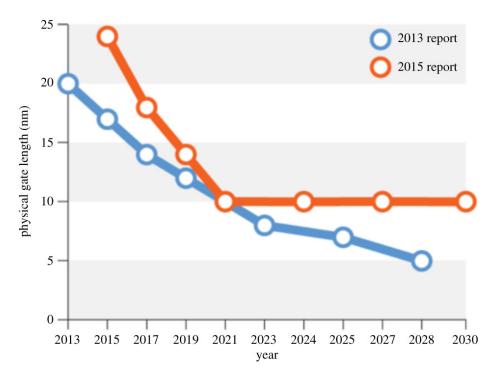

| 1.1  | The most recent prediction from ITRS suggests transistor scaling will end in 2021 (adapted from [2])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 2   |

| 1.2  | All additional approaches to further performance will approximately end in 2025 due to the end of the road-map for improvements in semiconductor lithography. (adapted from [2])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 2   |

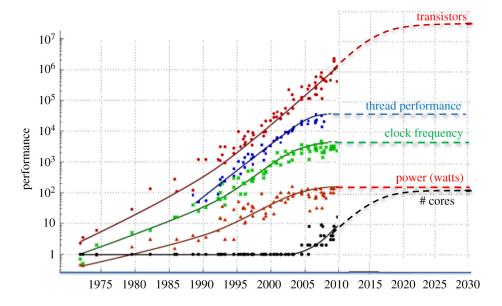

| 1.3  | Three potential paths forward to realize continued performance improvements for digital electronics technology (adapted from [2])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 3   |

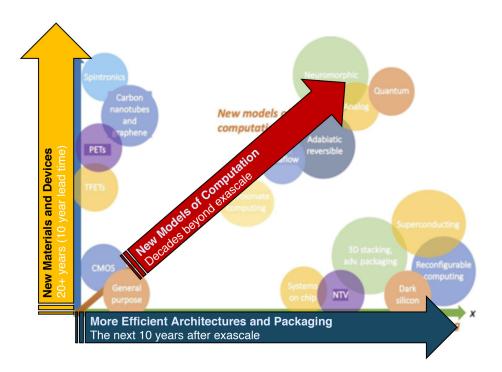

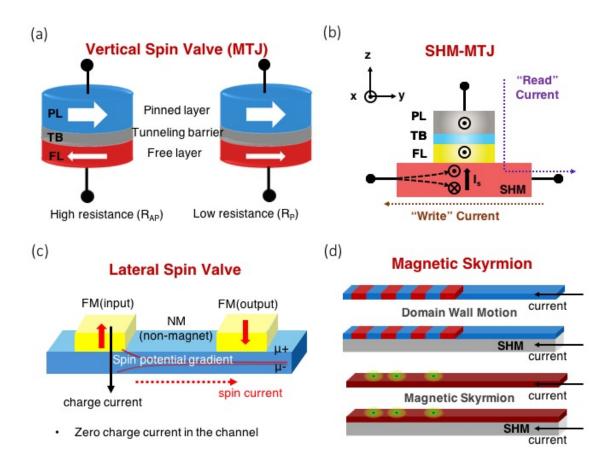

| 2.1  | (a) Vertical Spin Valve: A magnetic tunnel junction (MTJ) consists of a thin tunneling oxide sandwiched between two ferromagnets, namely the free layer (FL) and the pinned layer (PL). (b) 3 terminal SHM-MTJ: Device with MTJ on the top of the spin Hall metal (SHM) layer. When an injected charge current flows through the SHM, a spin-orbit torque is generated and exert a torque on the adjacent nanomagnet owing to the spin Hall effect (SHE). (c) Lateral spin valve consists of one input and one output nanomagnet connected by a non-magnetic channel. By injecting a charge current flowing through the input nanomagnet, the output nanomagnet can potentially be switched owing to non-local spin torque. The magnitude of the input spin current exponentially decreases with the connected channel length. (d) Magnetic skyrmion: Similar to domain wall motion (DWM) based device, a sequence of skyrmions can be stored in a long nanotrack and driven by either injecting a charge current to the long ferromagnetic (FM) layer or to the SHM underneath the FM layer |    | 7   |

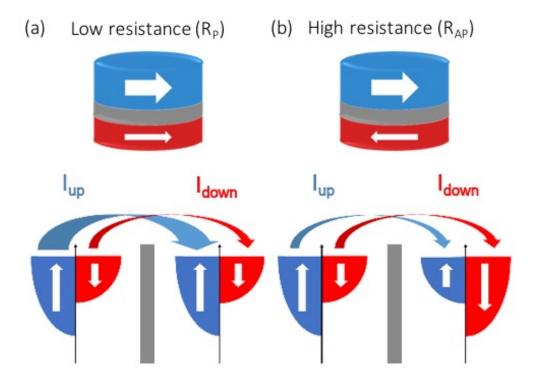

| 2.2  | A simplified structure of the Magnetic Tunnel Junction (MTJ) in (a) Parallel (P) and (b) Anti-parallel (AP) configuration with corresponding band diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 8   |

| 2.3  | Torques acting on a single-domain magnet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 11  |

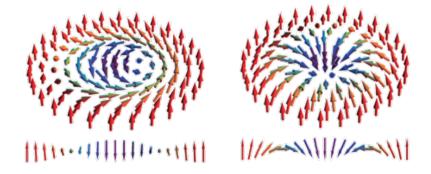

| 2.4  | Schematic of a chiral skyrmion (left) and a Neel skyrmion (right). The magnetization is pointing down in the center and pointing up on the edges. The magnetization rotates by $2 \pi$ along a diameter around an axis perpendicular to the diameter. [48]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 14  |

|      | pendicular to the diameter, [40]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •  | T.4 |

| Figu | ire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

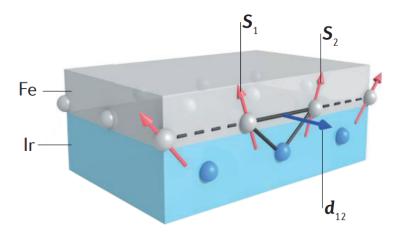

| 2.5  | Sketch of a DMI at the interface between a ferromagnetic metal (grey) and a metal with a strong SOC (blue). The direction of the DMI vector $D_{12}$ is perpendicular to the plane of the triangle (black solid line), composed of two magnetic sites (grey) and an atom with strong SOC (blue). [48]                                                                                                                                                                                                                                                   | . 15  |

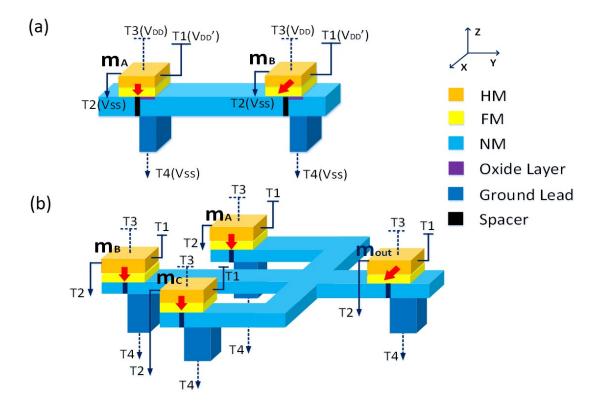

| 3.1  | (a) SOT buffer/inverter (b) SOT-DSL majority gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 18  |

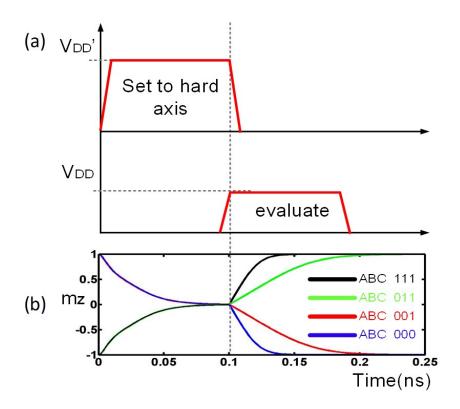

| 3.2  | (a) SOT buffer/inverter (b) SOT-DSL majority gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 20  |

| 3.3  | Pipeline operation of several stages of SOT-DSL concatenated using spin channels (dash line). Black boxes represent one stage of SOT-DSL (see Fig. 3.1). Input and output magnets (red boxes) are connected by spin channel.                                                                                                                                                                                                                                                                                                                            |       |

| 3.4  | Operation of four phase pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 22  |

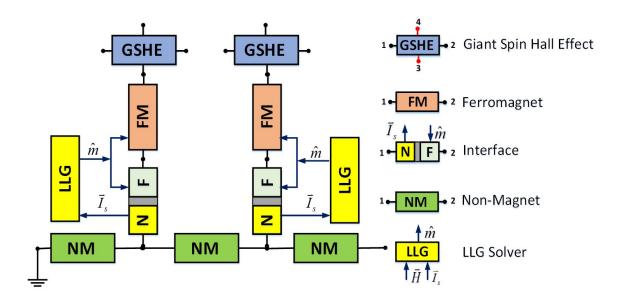

| 3.5  | Spin circuit model for SOT-DSL showing a lateral spin valve in contact with spin hall metal (SHM).                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 23  |

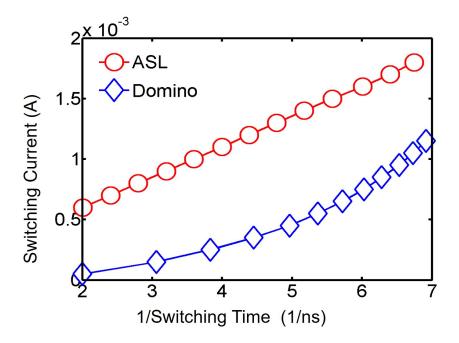

| 3.6  | Required input charge current for evaluation of ASL and SOT-DSL with increasing frequency of operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 24  |

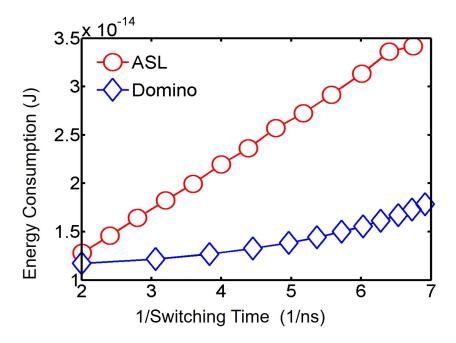

| 3.7  | Total energy consumption vs. frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 26  |

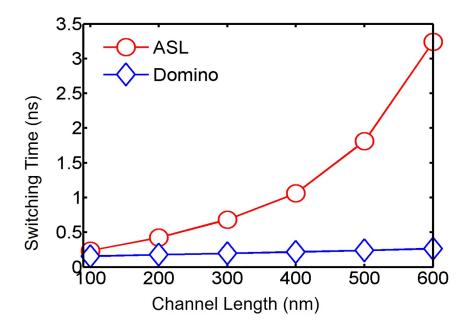

| 3.8  | Switching time with increasing spin channel length for ASL and SOT-DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | L. 27 |

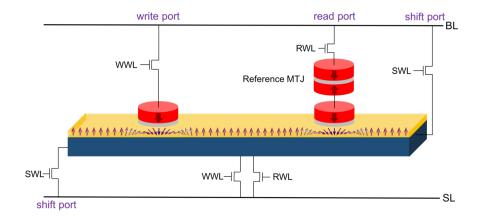

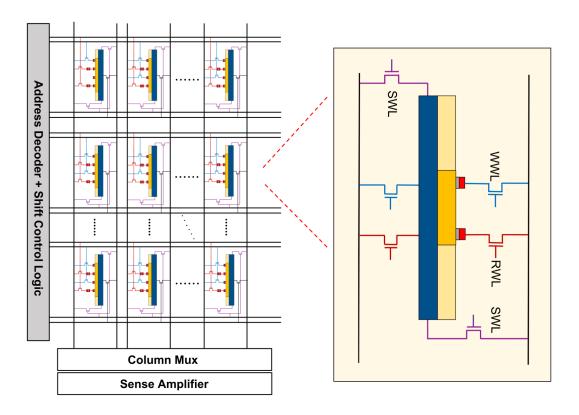

| 4.1  | Schematic of MS-based device and bit-cell. The proposed device structure can perform read/write/shift operations. A skyrmion can be nucleated in the nanotrack (yellow layer) by injecting a spin-polarized current through the left MTJ. The motion of skyrmions can be driven by utilizing vertical injection of a spin current generated from a charge current flowing through the Spin-Hall Metal (SHM) layer (blue layer). The presence of a skyrmion can be detected by sensing the voltage difference between the read MTJ and the reference MTJ | . 32  |

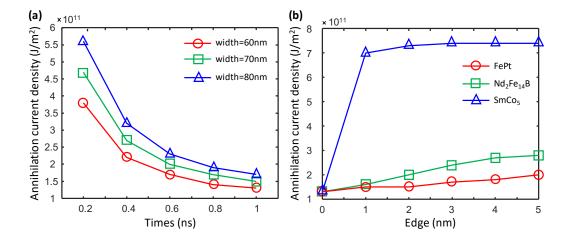

| 4.2  | (a) Critical annihilation current density versus various shift operation time. (b) Critical annihilation current density in a 1 $ns$ shift operation versus various high- $K$ materials with different width. The annihilation current density is less sensitive to the width of the high- $K$ materials with higher anisotropy constant                                                                                                                                                                                                                |       |

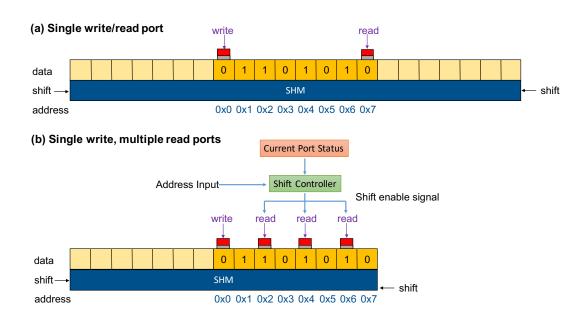

| 4.3  | Logical view of a multi-bit MS-based cell with (a) single write/read port or (b) single write and multiple read ports. A sequence of bits are stored in the nanotrack                                                                                                                                                                                                                                                                                                                                                                                   | . 38  |

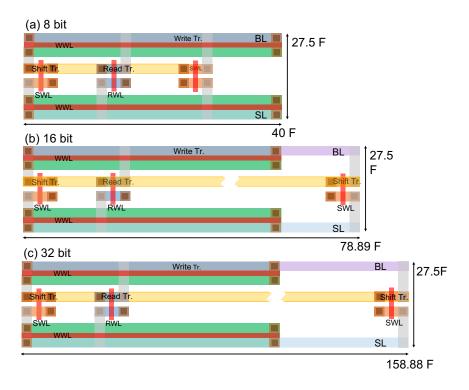

| 4.4  | Layout of a 8/16/32-bit MS cell with single write/read port at the 45nm technology node (F)                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 40  |

| Figu | re P                                                                                                                                                                                                                                                                                                                                                                                                                  | age      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

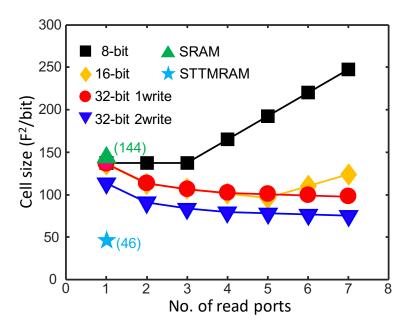

| 4.5  | Bit-cell area comparison for different multi-bit designs                                                                                                                                                                                                                                                                                                                                                              | 41       |

| 4.6  | The memory array organization of skyrmion based multi-bit cells                                                                                                                                                                                                                                                                                                                                                       | 42       |

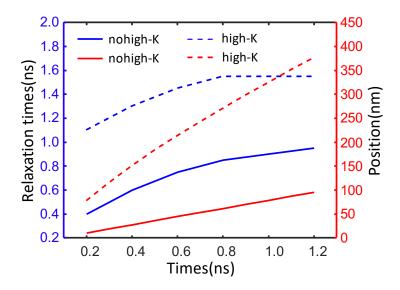

| 4.7  | Relaxation times and final position comparison under a current of 1.44 $\times$ $10^{-5}$ A and $5.76 \times 10^{-5}$ A. High- $K$ materials are adhered under the current of $5.76 \times 10^{-5}$ A to avoid skyrmions from annihilation from edges.                                                                                                                                                                | 46       |

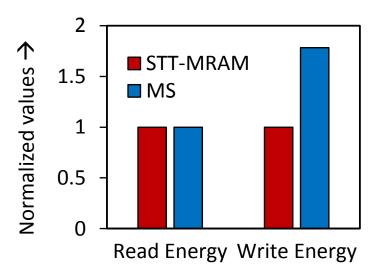

| 4.8  | Array-level comparison of read and write energies with iso-area STT-MRAM                                                                                                                                                                                                                                                                                                                                              | Л47      |

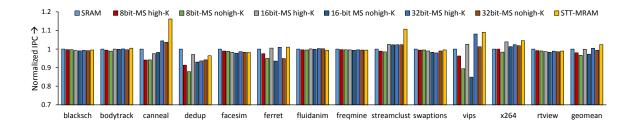

| 4.9  | L2 cache performance comparison across different memory technologies                                                                                                                                                                                                                                                                                                                                                  | 48       |

| 4.10 | Energy trends across different memory technologies                                                                                                                                                                                                                                                                                                                                                                    | 50       |

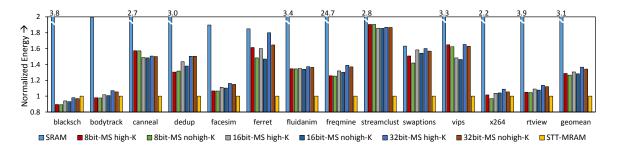

| 5.1  | Illustration of a biological neuron network. A biological pre-neuron receives, processes and transmits information to a post-neuron via synapse                                                                                                                                                                                                                                                                       | 54       |

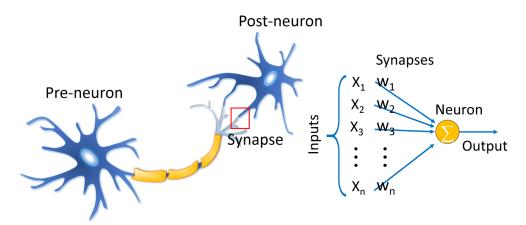

| 5.2  | Skyrmion-based synaptic device structure and the corresponding schematic. A vertical injection of a spin-polarized current is utilized to drive a skyrmion in the nanotrack. Notches with high- $K$ material are attached at both sides of the read position to prevent skyrmion displacement. Besides, high- $K$ materials are attached at both upper and lower boundaries to avoid skyrmion annihilation from edges | 58       |

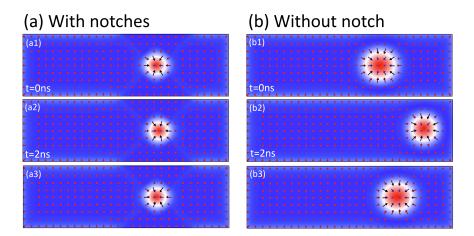

| 5.3  | Motion of a skyrmion under a read current of 56 $\mu A$ in a nanotrack w/(with) and w/o(without) notches. (a1) and (b1) show the initial position of a skyrmion under the read MTJ. (a2) and (b2) represent the final position after 2 $ns$ under the read current. (a3) and (b3) are the results of 1 $ns$ relaxation time after turning the read current OFF                                                        | 59       |

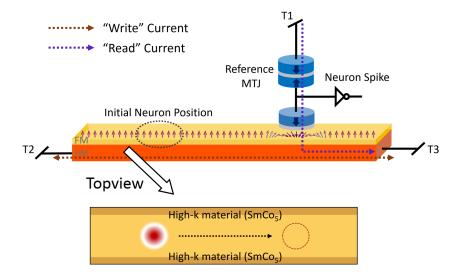

| 5.4  | Device structure of the proposed spintronic spiking neuron and the top view of the nanotrack. High- $K$ materials with a width of $1\ nm$ are attached to both edges for better skyrmion confinement. The width of the nanotrack is $60\ nm$ , and the length is $200\ nm$                                                                                                                                            | 61       |

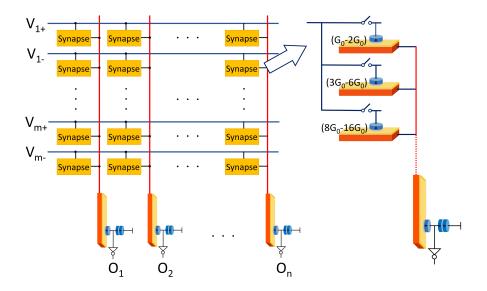

| 5.5  | Hardware mapping of an All-Spin Deep Spiking neural architecture. Skyrmion based synapses in the crossbar array encode the synaptic weight, and provide a corresponding synaptic current to the interfaced skyrmion-based neurons                                                                                                                                                                                     | n-<br>62 |

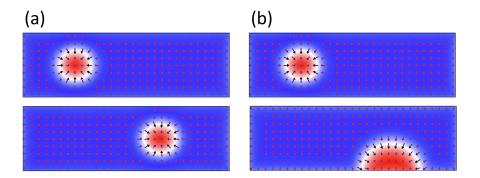

| 5.6  | (a) shows the motion of a skyrmion under a current magnitude of 70 $\mu A$ for 2 $ns$ and 0.5 $ns$ relaxation time with high- $K$ materials adhered on both edges. (b) shows a skyrmion is annihilated in 2 $ns$ under a current of 50 $\mu A$ for 2 $ns$ without the aid of high- $K$ materials                                                                                                                      | 65       |

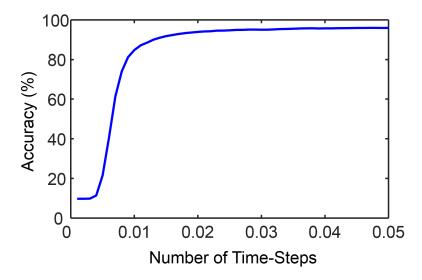

| 5.7  | Temporal variation of the classification accuracy of the "All-Spin" skyrmionic SNN as a function of the number of time-steps                                                                                                                                                                                                                                                                                          | 67       |

| Figu | are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

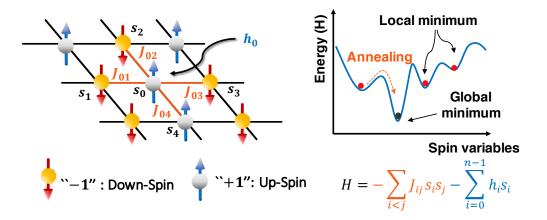

| 6.1  | (a) Ising model (b) Energy profile and annealing process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 72  |

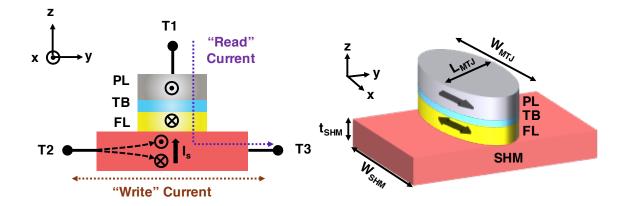

| 6.2  | Three-terminal SHM-MTJ device, with a SHM underlying an in-plan magnetic anisotropy (IMA) MTJ. The magnetization of the FL can be written by injecting a current through the SHM, and read by sensing the resistance of the MTJ. Write/read operation can be optimized separately as the write/read path is decoupled, and hence, the design is more flexible in such three-terminal device                                                                                                                                                                                                                                    | . 73  |

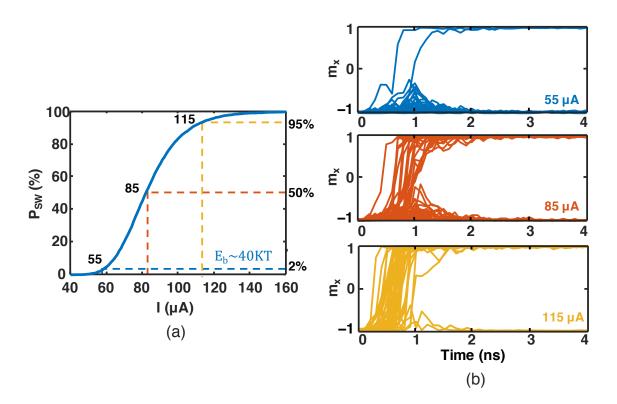

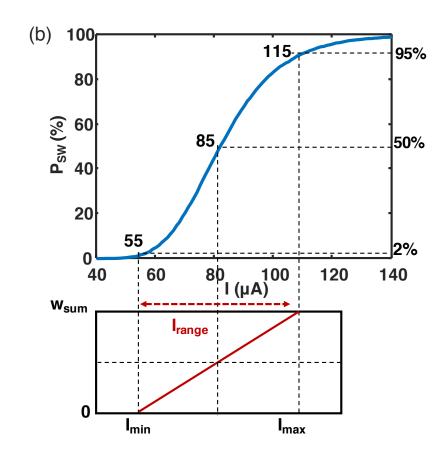

| 6.3  | (a) Switching probability of an MTJ in response to a current pulse flowing through the SHM. $10^4$ simulations were performed for each current step. The current with different magnitude (varies from 40 $\mu$ A to 160 $\mu$ A with 1 $\mu$ A per step) is applied for 1 $ns$ , and followed by a 1 $ns$ relaxation time. (b) Magnetization switching from -1 to +1 under an input current of 55 $\mu$ A, 85 $\mu$ A and 115 $\mu$ A for 1 $ns$ . For better visualization, only 50 out of $10^4$ simulations are plotted here, and the results are obtained from Fig.6.3.                                                   | (a)75 |

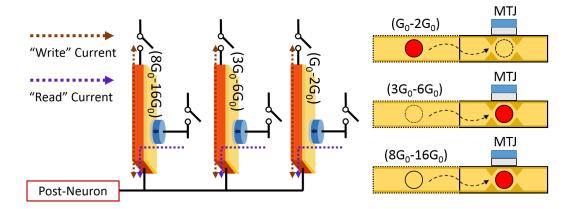

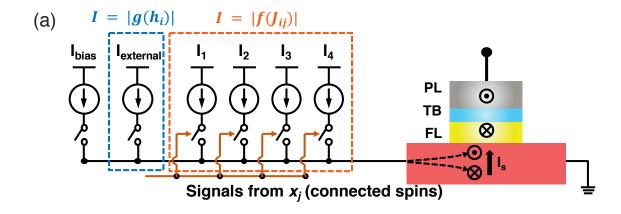

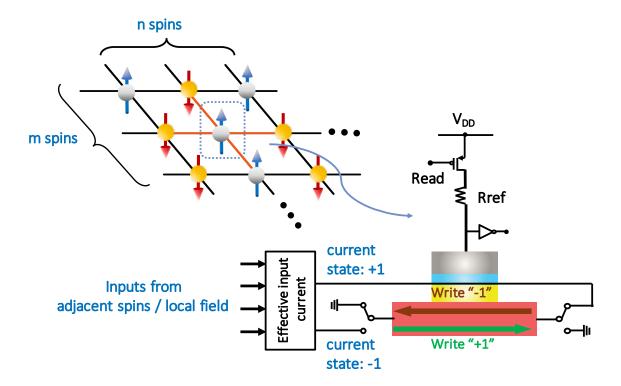

| 6.4  | (a) The evolution of a particular spin $(s_i)$ is determined by the final effective force from all the adjacent neighbors and its local field. This updating process is mapped to current-dependent switching probability of the magnetization of the FL. To control the amount of total current flowing through the SHM, multiple current sources and switches are introduced. The magnitude of each current source from a neighboring spin $(s_j)$ and the local field $(h_i)$ , depends on the value of $ J ,  h $ , respectively. (b) Magnetization switching probability can be controlled by the amount of input current | . 77  |

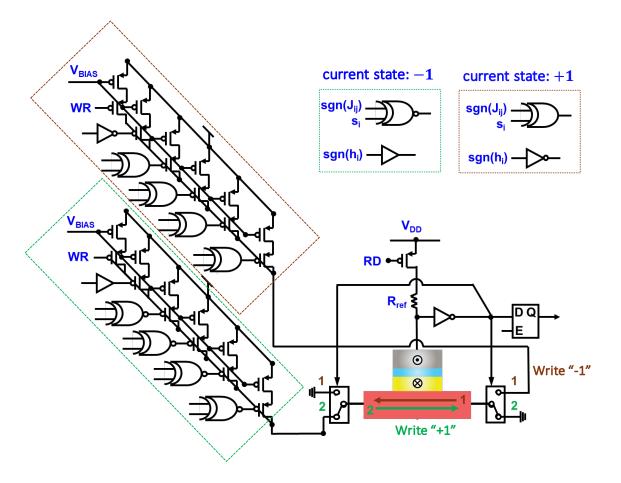

| 6.5  | The proposed device-circuit configuration for single Ising model. Peripheral CMOS logic gates are used to perform the updating process. An inverter in series with other transistors and reference resistors is used to convert the spin state to binary voltage value                                                                                                                                                                                                                                                                                                                                                         | . 79  |

| 6.6  | Hardware implementation of an Ising model based on the proposed SHM-MTJ devices as a computational unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 82  |

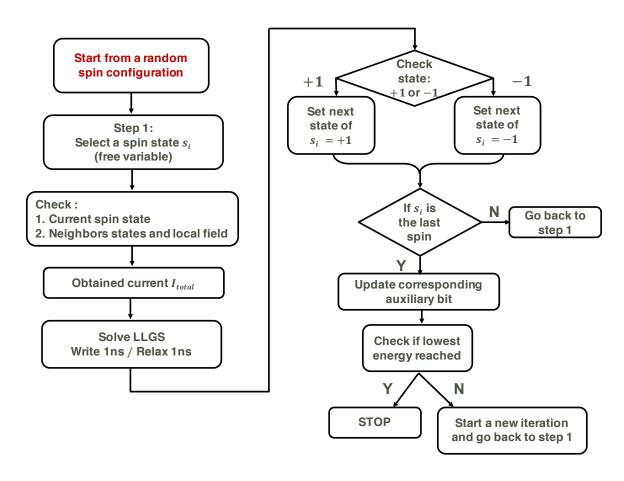

| 6.7  | The process of spin updates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 85  |

| 6.8  | Simulation result of our proposed Ising cell to solve biprime factorization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 86  |

#### ABSTRACT

Chen, Mei-Chin Ph.D., Purdue University, May 2020. Spintronic Devices and Its Applications. Major Professor: Kaushik Roy.

Process variations and increasing leakage current are major challenges toward memory realization in deeply-scaled CMOS devices. Spintronic devices recently emerged as one of the leading candidates for future information storage due to its potential for non-volatility, high speed, low power and good endurance. In this thesis, we start with the basic concepts and applications of three spintronic devices, namely spin orbit torque (SOT) based spin-valves, SOT-based magnetic tunnel junctions and the magnetic skyrmion (MS) for both logic and machine learning hardware.

We propose a new Spin-Orbit Torque based Domino-style Spin Logic (SOT-DSL) that operates in a sequence of Preset and Evaluation modes of operations. During the preset mode, the output magnet is clocked to its hard-axis using spin Hall effect. In the evaluation mode, the clocked output magnet is switched by a spin current from the preceding stage. The nano-magnets in SOT-DSL are always driven by orthogonal spins rather than collinear spins, which in turn eliminates the incubation delay and allows fast magnetization switching. Based on our simulation results, SOT-DSL shows up to 50% improvement in energy consumption compared to All-Spin Logic. Moreover, SOT-DSL relaxes the requirement for buffer insertion between long spin channels, and significantly lowers the design complexity. This dissertation also covers two applications using MS as information carriers. MS has been shown to possess several advantages in terms of unprecedented stability, ultra-low depinning current density, and compact size. We propose a multi-bit MS cell with appropriate peripheral circuits. A systematic device-circuit-architecture co-design is performed to evaluate the feasibility of using MS-based memory as last-level caches for general purpose pro-

cessors. To further establish the viability of skyrmions for other applications, a deep spiking neural network (SNN) architecture where computation units are realized by MS-based devices is also proposed. We develop device architectures and models suitable for neurons and synapses, provide device-to-system level analysis for the design of an All-Spin Spiking Neural Network based on skyrmionic devices, and demonstrate its efficiency over a corresponding CMOS implementation.

Apart from the aforementioned applications such as memory storage elements or logic operation, this research also focuses on the implementation of spin-based device to solve combinatorial optimization problems. Finding an efficient computing method to solve these problems has been researched extensively. The computational cost for such optimization problems exponentially increases with the number of variables using traditional von-Neumann architecture. Ising model, on the other hand, has been proposed as a more suitable computation paradigm for its simple architecture and inherent ability to efficiently solve combinatorial optimization problems. In this work, SHE-MTJs are used as a stochastic switching bit to solve these problems based on the Ising model. We also design an unique approach to map bi-prime factorization problem to our proposed device-circuit configuration. By solving coupled Landau-Lifshitz-Gilbert equations, we demonstrate that our coupling network can factorize up to 16-bit binary numbers.

#### 1. INTRODUCTION

For over the past five decades, the incessant down-scaling of the complementary metal-oxide-semiconductor (CMOS) has driven the evolution of the semiconductor industry. The number of on-chip transistors on a die increased significantly following Moore's law, with the scaling of CMOS technology [1]. The reduction in the size of each transistor, increased integration density, lower of supply voltage and an increase in clock frequency, albeit with increase in power density, has contributed to higher processing capabilities as well as enhanced performance with more functionalities. However, further reducing the device feature size beyond 5nm may lead to significant impact on reliability, process variations, cost, and lifetime of transistors owing to potential thermal damage, increased leakage (Fig. 1.1 [2]). Moreover, as shown in Fig. 1.2, the classical technology driver, whose trend has followed Moore's Law for the past five decades, is predicted to flatten by 2025 [2]. Hence, in order to foster continued technology scaling in the absence of traditional Moore's Law, research has started in earnest to search for alternative device physics and material replacement. Moreover, for applications such as vision, optimization, pattern recognition, image/signal processing, and data classification, where the implementation in traditional von-Neumann architecture consisting of Boolean logic and memory circuits based on CMOS technology, turn out to be inefficient. This inefficiency in resources (which result in higher area requirement) and power is owing to the fundamental mismatch between the computational units and the underlying hardware.

Numerous potential solutions have been investigated to continue the performance scaling benefits. Fig. 1.3 depicts three different directions that could potentially advance the performance beyond the end of scaling limitation. In the near-term, research will be focus on developing advanced packaging and specialized architecture using existing computational units. In the mid-term, multiple beyond-CMOS devices,

Fig. 1.1. The most recent prediction from ITRS suggests transistor scaling will end in 2021 (adapted from [2]).

Fig. 1.2. All additional approaches to further performance will approximately end in 2025 due to the end of the road-map for improvements in semiconductor lithography. (adapted from [2])

such as graphene, carbon nanotubes, and Spintronics would be introduced to enhance the performance by creating more efficient underlying logic devices. The last direction represents using beyond CMOS technology to open new computing paradigms for non-conventional computing models such as neural network, probabilistic learning, and quantum computing, which aims to solve problems not well addressed by digital computing [2].

In order to bridge the performance gap and to keep with this scaling trend, this research exploits Spintronic devices to store data and implement computational units, exploring applications such as neural computing and combinatorial optimization. Due to the inherent non-volatility, good compatibility with the CMOS [3–6], spintronic devices are promising candidates for both storage and data processing.

The dissertation is organized as follows: The basics operation principles of various spin-based devices as storage elements are reviewed in Chapter 2. In Chapter

Fig. 1.3. Three potential paths forward to realize continued performance improvements for digital electronics technology (adapted from [2]).

3, we propose Spin-Orbit Torque based high-performance Domino-style Spin Logic (SOT-DSL). In Chapter 4 and 5, we move our focus to magnetic skrymion (MS), a recent exciting development in the field of spintronics for its remarkably high stability, extremely compact size, and ultra-low depinning current density. We propose the usage of MS as more robust information storage in cache memories (Chapter 4)—more specifically, a multi-bit MS cell is designed as last-level cache for general purpose processors. A device-to-system co-design is performed to evaluate the feasibility of our proposal. Moreover, we explore MS as computational units in deep spiking neural network (Chapter 5) by investigating MS-based synapses and neurons, and performing a systematic device-circuit-architecture co-design for digit recognition with the MNIST handwritten digits dataset. In Chapter 6, we introduce spintronic device as stochastic computational units to implement Ising spin model to solve bi-prime factorization. We demonstrated that our network can factorize up to 16-bit binary numbers. Finally, we summarize and conclude this dissertation in Chapter 7.

#### 2. BASIC OPERATION OF SPIN-BASED DEVICES

This chapter provides a brief overview of several spintronic device structures, which have been widely used as storage elements or to perform specific logic functionalities. Fig. 2.1 depicts the spin-based devices whose basic functionalities will be covered in this section, including two-terminal magnetic tunnel junction (MTJ), three-terminal MTJ in which the magnetization switching is based on spin orbit torque (SOT), lateral spin valve (LSV), and magnetic skyrmion (MS).

#### 2.1 Two-Terminal Magnetic Tunnel Junction

Magnetic tunnel junction (MTJ) is a basic storage element in almost all spintorque based memories. As shown in Fig. 2.1(a), in the simplest description, an MTJ consists of a thin tunneling barrier (AlO or MgO) sandwiched by two ferromagnetic layers. These two layers are called the pinned layer (PL) and the free layer (FL), respectively. Normally, the PL is magnetically fixed by exchange interaction with an adjacent anti-ferromagnetic (AFM) layer so that it can be used as a reference layer. On the other hand, the magnetization of FL responds to external stimuli (such as magnetic field or spin-polarized current) and rotates freely between a direction either parallel (P) or anti-parallel (AP) to that of the PL. An MTJ presents a low resistance state ( $R_P$ ) and a high resistance state ( $R_{AP}$ ) for P and AP configuration, respectively [See Fig. 2.2]. These two extremely stable resistance state can be used to store binary information, and the stability of the nanomagnet in the presence of thermal noise is determined by energy barrier,  $E_B$ , and can be expressed as [7]

$$E_B = K_{u2}V \tag{2.1}$$

where  $K_{u2}$  is uni-axial anisotropy, and V is the volume of the magnet. Note that the energy barrier between two stable states are formed without application of any external voltage. Hence, a nanomagnet inherently non-volatile with no leakage power consumption. Moreover, the energy barrier between P and AP configuration is designed small enough to ensure easy writeability, but large enough to sustain thermal stability. In the absence of thermal agitation, the lifetime of information safely stored in a nanomagnet exponentially increases with the magnitude of the energy barrier, and can be expressed as

$$t_{lifetime} = \tau_0 \exp(E_B) \tag{2.2}$$

where  $1/\tau_0$  is the attempt frequency of the order of 1ns. For instance, a barrier height of  $40K_BT$  corresponds to a nanomagnet lifetime of  $\sim 7.4$  years [7].

Depending on the direction of the "easy" axis, MTJs can be simply categorized into either Perpendicular Magnetic Anisotropy (PMA) MTJ, or In-plane Magnetic Anisotropy (IMA) MTJ. Both IMA and PMA MTJs are thin-film magnets, the magnetization of which tends to point within the film owing to shape anisotropy. For IMA materials, the shape anisotropy dominates the resultant anisotropy of the nanomagnet, and hence, the "easy axis" is in-plane direction. Nanomagnets with elliptical cross-section is commonly used in this case, as the "easy axis" is in the direction of the longer axis [8–10]. On the contrary, the magnetocrystalline anisotropy is dominant in PMA nanomagnets. In order to lower the overall energy of the system, magnetization favors out-of-plane direction, and we refer the out-of-plane direction as "easy" axis direction [8,11,12]. Hence, PMA nanomagnets are usually of circular cross-sectional area.

The most important physical mechanism, namely, the Tunneling Magnetoresistance Ratio (TMR) and the spin-transfer torque (STT) effect will be qualitatively discussed in the following sections.

Fig. 2.1. (a) Vertical Spin Valve: A magnetic tunnel junction (MTJ) consists of a thin tunneling oxide sandwiched between two ferromagnets, namely the free layer (FL) and the pinned layer (PL). (b) 3 terminal SHM-MTJ: Device with MTJ on the top of the spin Hall metal (SHM) layer. When an injected charge current flows through the SHM, a spin-orbit torque is generated and exert a torque on the adjacent nanomagnet owing to the spin Hall effect (SHE). (c) Lateral spin valve consists of one input and one output nanomagnet connected by a non-magnetic channel. By injecting a charge current flowing through the input nanomagnet, the output nanomagnet can potentially be switched owing to non-local spin torque. The magnitude of the input spin current exponentially decreases with the connected channel length. (d) Magnetic skyrmion: Similar to domain wall motion (DWM) based device, a sequence of skyrmions can be stored in a long nanotrack and driven by either injecting a charge current to the long ferromagnetic (FM) layer or to the SHM underneath the FM layer.

Fig. 2.2. A simplified structure of the Magnetic Tunnel Junction (MTJ) in (a) Parallel (P) and (b) Anti-parallel (AP) configuration with corresponding band diagram.

#### 2.1.1 Tunneling Magnetoresistance Ratio (TMR)

The resistance of an MTJ is determined by the relative magnetization of two ferromagnetic layers. The Tunneling Magneto-resistance Ratio (TMR), defined by

$$TMR = \frac{R_{AP} - R_P}{R_P} \times 100\%,$$

(2.3)

measures the resistance difference of an MTJ between P and AP configurations. The TMR effect was first experimentally demonstrated in 1995 [1,13], and the demonstration of TMR effect up to 604 % at room temperature has been reported in 2008 [14]. TMR depends on the quality of well-crystallized MgO and interfaces [15]. High TMR ratio represents a larger gap in the resistance between the two states, and vice versa. Electrons flowing through an MTJ carry either up-spin (majority spin) or down-spin

(minority spin) [See Fig. 2.2]. In the absence of spin scattering or spin-flip processes during the tunneling process, the flow of electron carrying spin-up  $(I_{up})$  and spindown  $(I_{down})$  can be treated as decoupled current paths, and the total charge current is  $I_{up}+I_{down}$ . The tunneling current of the majority and the minority current depends on the available free electrons state in the two ferromagnetic layers and the band matching of the interface. Suppose an MTJ is in the P configuration with a good band matching between the majority/minority density of states of the FL and PL, a low resistance is observed since there are sufficient states to accommodate all the available electrons for conduction. On the contrary, for an MTJ in the AP configuration, the majority (minority) spin in the FL (PL) is the minority (majority) spin in the PL (FL). This results in a large resistance as the majority/minority tunneling current is limited by either the availability of carriers in one contact or the empty states in the other contact. Note that since the mechanism of electron transport in an MTJ is the tunneling effect, the resistance of an MTJ  $(R_{MTJ})$  depends on the thickness of the tunneling oxide as well as the applied voltage across the MTJ, which can be formulated using the Non-Equilibrium Green's Function based transport simulation framework [16].

#### 2.1.2 Spin-Transfer Torque (STT) and magnetization dynamics

In a ferromagnetic material, the density of states for spin-up and spin-down electrons are different. Hence, a ferromagnet reorients the flow of unpolarized current to its magnetization by exerting a spin transfer torque. The opposite scenario was theoretically predicted by Slonczewski and Berger in 1998 [17,18]— that is, when the polarized spin current is injected into a ferromagnet, the injected spin will exert a torque to the magnetization of the ferromagnet as well. To conserve the total angular momentum of the system, the change in the angular momentum of the spin current is equivalent to the change in the ferromagnet. In other words, the angular momentum lost by injected electrons (ferromagnet) must be absorbed by the ferromagnet (in-

jected electrons). This angular momentum transfer is called the spin-transfer torque (STT) effect and can be expressed as [19,20]

$$\tau_{STT} = \gamma \frac{\hbar}{2} \frac{\eta I}{q} \frac{1}{M_s V} (m \times m_p \times m)$$

(2.4)

where m is the normalized magnetization vector;  $m_p$  is the fixed layer polarization;  $\gamma$  is the Gilbert gyromagnetic ratio; and  $M_{sat}V$  is the total saturation magnetization.

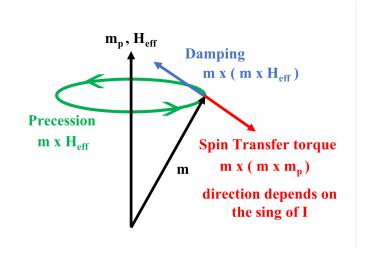

To understand the magnetic dynamics of the free layer, we need to take the spintransfer torque from the injected spin polarized current, the applied magnetic field, magnetic anisotropies, damping, and thermal fluctuations into consideration. As shown in Fig. 2.3, the precession of the magnetization is owing to an applied magnetic field, whereas the damping torque moves the magnetization toward the effective field direction. The spin-transfer torque can enlarge the damping torque, or exploit a torque in the opposite direction from the damping depending on the direction of injected current. The magnetization dynamics of the FL under an external stimuli, such as a magnetic field or spin current, at zero temperature can be obtained by solving Landau-Lifshitz-Gilbert-Slonczewski (LLGS) equation. [21, 22]

$$\frac{d\widehat{m}}{dt} = -\gamma(\widehat{m} \times H_{eff}) + \alpha(\widehat{m} \times \frac{d\widehat{m}}{dt}) + \frac{I_s}{qN_s}(\widehat{m} \times \sigma \times \widehat{m}), \tag{2.5}$$

where  $\gamma = \frac{2\mu_B\mu_0}{\hbar}$  is the Gilbert gyromagnetic ratio for electron;  $\widehat{m}$  is the unit vector of the FL;  $\alpha$  is the Gilbert damping ratio;  $H_{eff}$  is the effective magnetic field incorporating the shape anisotropy for an elliptical disk;  $N_s = \frac{M_s V}{\mu_B}$  is the number of spins in the FL occupying a definite volume V;  $M_s$  is the saturation magnetization;  $\mu_B$  is the Bohr magneton; and  $\mu_0$  is the magnetic permeability.

At non-zero temperature, the magnetization switching dynamics of an MTJ is influenced by thermal noise, which is accounted as a random thermal field and can be factored into the LLGS equation by augmenting  $H_{eff}$  with a thermal field  $H_{thermal}$ , expressed as

$$H_{thermal} = \sqrt{\frac{\alpha}{1 + \alpha^2} \frac{2K_B T}{\gamma \mu_0 M_s V \delta_t}} G_{0,1}$$

(2.6)

where  $G_{0,1}$  is a Gaussian distribution with zero mean and unit standard deviation;  $K_B$  is the Boltzmann constant; T is the temperature; and  $\delta_t$  is the simulation time step. Hence, an MTJ exhibits stochastic switching during "write" operation in the presence of thermal noises.

Fig. 2.3. Torques acting on a single-domain magnet.

# 2.1.3 Spin-Orbit Torque (SOT)

In a two terminal MTJ, FM layers serve as a spin polarizer, and the spin current is generated by passing a charge current through an FM layer. Hence, the efficiency of the generated spin current is limited by the polarization strength of the FM layer. Recently, a novel and efficient way to generate spin current has been experimentally demonstrated on I/FM/SHM (I:insulator, FM: ferromagnetc, and SHM: spin Hall metal) multilayer structures, and have opened up the possibility of much greater spin injection efficiencies owing to strong spin-orbit coupling (SOC) [23]. Spin orbit torque (SOT) can be generated at the interface of FM/SHM when a charge current passes through the underlying SHM. Specifically, efficient magnetization switching [24–30], domain wall motion [31–34], and spin-torque oscillations [35–37] were experimentally observed, which established this process as a more efficient method for magnetization switching.

Two possible mechanisms have been proposed to explain the SOT phenomenon, namely the Rashba model with broken spatial inversion symmetry [33, 38], and the spin Hall effect (SHE) [39, 40]. In this dissertation, we consider SHE to be the dominant underlying physical phenomenon. In Fig. 2.1(b), electrons with opposite spin polarization scatters on the top and bottom surfaces of SHM when passing a "write" current through the HM. The spin current,  $I_s$ , is generated by a charge current flowing through the SHM underlayer, and can be expressed as

$$I_s = \theta_{sh} \frac{A_{MTJ}}{A_{SHM}} I_e \tag{2.7}$$

where  $A_{MTJ}$  and  $A_{SHM}$  are the cross sectional areas of the MTJ and SHM, respectively, and  $\theta_{sh}$  is the spin-Hall angle [39]. It is worth noting that spin current generated from SHM can potentially provide energy-efficient "write", as the spin injection efficiency can be larger than 100 % and is not limited by the polarization of the PL. Moreover, the polarization of the generated spin current is in-plane direction owing to SHE, and thereby SOT induced magnetization reversal is only possible for IMA MTJ [24, 25, 27].

#### 2.2 Lateral Spin Valve

Figure 2.1(c) depicts a lateral spin valve (LSV) structure, consisting of an input and output nanomagnet connected by a non-magnetic channel. By injecting electrons through the input nanomagnet, electrons are spin polarized with the same magnetization of the input nanomagnet and accumulate underneath the input nanomagnet. Owing to the gradient of spin potential difference between the two sides, a spin current diffuses from the input to the output nanomagnet, and exerts a non-local spin-torque to the output nanomagnet. As a result, stored information can be transmitted from input to output nanomagnet. The non-magnetic channel here serves as a conduit for information transfer through the use of non-local spin injection. Owing to the spin-flip process in the channel, the magnitude of the injected spin current decays

exponentially with the distance between two nanomagnets. Therefore, material with larger spin-flip length would be chosen in the LSV structure [41,42].

#### 2.3 Magnetic Skyrmion

Figure 2.1(d) depicts multiple data bits stored in a sequence of magnetic domains, separated by domain walls, within a nanowire. DWM-based caches [43–46] have shown significant improvement in performance (with higher packing density and better energy efficiency) over other spintronic devices. However, the motion of domain walls might be pinned by the presence of defects [47], raising concerns about the feasibility of DWM-based applications. Magnetic skyrmions, on the other hand, have recently emerged as a promising alternative for future information carrier [48–51]. As shown in Fig. 2.1(d), similar to a DWM based device, a sequence of skyrmions can be stored in a long nanotrack, and driven by either injecting a current through the long nanotrack or through the SHM underneath the long nanotrack.

Magnetic skyrmions have been shown to possess several benefits over DWM based devices in terms of stability, density, and are less limited by imperfectness of the material. Specifically, its topological properties prevent the motion of skyrmions from being pinned at defect sites in a magnetic layer, and thus make them a more robust information carrier. The swirling structure of a skyrmion is characterized by the topological number defined by

$$S = \frac{1}{4\pi} \int m \cdot \left( \left( \frac{\partial m}{\partial x} \right) \times \left( \frac{\partial m}{\partial y} \right) dx dy \right)$$

(2.8)

as the integral of the solid angle and counts how many times m(r) = m(x, y) wraps the unit sphere, m is the normalized magnetization. The topological number for a FM state (S = 0) is different from a skyrmion state (S = 1), thereby a skyrmion cannot be continuously deformed to an FM state or other magnetic state. A topological barrier is inherently built between an FM and a skyrmion state, and thus skyrmions are topologically protected and possess relatively stable structures.

As shown in Fig. 2.4, depending on the spin configuration, the whirling structure can be a chiral skyrmion, or Neel skyrmion, and its state can be explained by the presence of Dzyaloshinskii-Moriya Interaction (DMI) [52,53] – the DMI between two atomic spins  $S_1$  and  $S_2$  with a neighboring atom can be expressed as  $H_{DM} = -D_{1,2} \cdot (S_1 \times S_2)$  where  $D_{1,2}$  is the Dzyaloshinskii-Moriya (DM) vector [48,49, 54–57]. Skyrmion lattices were first observed experimentally in B20 compounds (noncentrosymmetric bulk magnetic materials) such as MnSi, FeCoSi and FeGe, whose non-centrosymmetric crystal structure gives rise to bulk Dzyaloshinskii-Moriya Interaction (DMI) [54]. Recently, interfacial DMI have been predicted from a 3-site indirect exchange mechanism between two atomic spins  $S_1$  and  $S_2$  with a neighboring atom having a large spin-orbit coupling (SOC) [58]. As shown in Fig. 2.5, an interfacial DMI is generated at the interface between a thin FM layer and a SHM layer having strong SOC. This mechanism generates a DMI for the interface spins  $S_1$ and  $S_2$  with the DMI vector. A general advantage of skyrmions in thin films is that several parameters, such as the magnetic anisotropy and the DMI strength can be adjusted experimentally, can be modified by ion irradiation and diluted by increasing the film thickness [58], respectively.

Fig. 2.4. Schematic of a chiral skyrmion (left) and a Neel skyrmion (right). The magnetization is pointing down in the center and pointing up on the edges. The magnetization rotates by 2  $\pi$  along a diameter around an axis perpendicular to the diameter. [48]

Fig. 2.5. Sketch of a DMI at the interface between a ferromagnetic metal (grey) and a metal with a strong SOC (blue). The direction of the DMI vector  $D_{12}$  is perpendicular to the plane of the triangle (black solid line), composed of two magnetic sites (grey) and an atom with strong SOC (blue). [48]

# 3. DOMINO-STYLE SPIN-ORBIT TORQUE-BASED SPIN LOGIC

#### 3.1 Introduction

In quest for non-volatile and power-efficient logic styles, has started in earnest to use *spin* rather than *charge* as state variables for computation. A well-known example is the nano-magnetic logic (NML) [59] where information between clocked nano-magnets propagates through dipolar field rather than charge. Since no charge transfer occurs during the computation process, logic operations with fundamentally low energy cost can be achieved [60]. However, high energy consumption for the clocking scheme, restrictions in the number of fan-ins, and scaling challenges are some of the key obstacles to the achievement of energy-efficient digital logic circuits [60]. As a result, several approaches to reduce the clocking energy are under investigation, for example, magnets covered with enhanced permeability dielectric (EPD) films have been proposed to concentrate the external field [61].

All spin logic (ASL) [62], based on lateral spin valve and non-local spin transfer torque effect, employs nano-magnets to store information and uses pure spin current to propagate information. As a result, ASL eliminates the energy inefficiency of NML stemming from the generation of the clocking field. Moreover, ASL provides low voltage operation, high logical efficiency, and high integration density compared to its CMOS counterparts [62]. However, the operating speed of ASL is severely limited by the incubation delay of the magnetization switching. When a nano-magnet (described by the direction of its magnetization m) is interacting with the spin current ( $I_S$ ), only the transverse component of the spin current ( $m \times m \times I_S$ ) is absorbed by the nano-magnet. Therefore, when m and  $I_S$  are close to collinear, spin absorption is minimal and hence, the torque acting on the nano-magnet is close to zero. For switching

to occur, considerable amount of time is required for m to sufficiently deviate from its easy-axis and absorb enough spin current. Consequently, high speed design is significantly challenging for ASL. In order for spin-based logic to provide the same level of performance as todays charge-based digital logic, there is a strong demand for a new spin-based logic device and logic style that allows higher speed of operation.

In this chapter, we propose Spin-Orbit-Torque based Domino style Spin Logic (SOT-DSL), a device structure well-suited for higher performance logic applications. SOT-DSL operates by first presetting the output magnet to its hard-axis using energyefficient spin orbit torque [63] prior to the evaluation mode. During the evaluation mode, information from the preceding nano-magnet is transmitted to the output magnet in the form of pure spin current. Note that the polarization of the spin current and the magnetization of the output magnet are orthogonal to each other. Therefore, when spin signal interacts with the output magnet, spin current absorption is maximal, and thus it exerts a larger torque on the magnet. Therefore, incubation delay can be eliminated and the proposed SOT-DSL is able to perform magnetization switching with much smaller input spin current while operating at higher speed. In addition, the proposed SOT-DSL can be concatenated with the addition of clock signals and can implement any set of Boolean functions. The rest of the chapter is organized as follows. Section 3.2 describes the structure and operation of our proposed SOT-DSL. Section 3.3 presents a four-phase pipelined operation required for the concatenation of SOT-DSL devices. The simulation framework used in this work is then discussed in Section 3.4. The results of our simulation and evaluation are presented in Section 3.5. Finally, Section 3.6 concludes this chapter.

## 3.2 SOT Based Domino Style Spin Logic

The device structure of SOT-DSL consists of a lateral spin valve with perpendicularly magnetized ferromagnets (FM) in contact with spin Hall metal (SHM), as shown in Fig. 3.1. The role of SHM is to drive the FM underlayer to its hard-axis

Fig. 3.1. (a) SOT buffer/inverter (b) SOT-DSL majority gate.

by utilizing spin current generated from spin Hall effect (SHE). The non-magnetic (NM) channel serves as a conduit for information transfer through the use of non-local spin injection. To ensure unidirectional information flow, the transmitting side of the FM/NM interface has high polarization (high-P) and receiving side has low polarization (low-P) with ground lead placed closer to the transmitting side [62]. The operation of SOT-DSL consists of two modes: Preset and evaluation. In order to provide these two operations, each unit of SOT-DSL is equipped with four terminals: terminal 1 and 2 (T1, T2 in Fig. 3.1) are used during preset, and terminal 3 and terminal 4 (T3, T4 in Fig. 3.1) are used during evaluation. The following subsections describe each of the two-step operation in detail.

#### 3.2.1 Preset (Set to Hard Axis)

During the preset mode, a charge current is passed through the SHM layer to set the magnetization of output magnet into its hard axis. In the example shown in Fig. 3.1, charge current flowing through SHM in y direction (T1 to T2) generates +x directed spin current in z-direction in the bulk of SHM. The transverse component of spin current is absorbed by the FM underneath the SHM and aligns the magnetization of FM into +x (hard axis). Note that, in contrary to easy-axis switching where the spin current needs to overcome the damping torque of the nano-magnet ( $\sim \alpha H_{ani}$ , where  $\alpha$  is the Gilbert damping parameter and  $H_{ani}$  is the anisotropy field), hardaxis switching requires the spin current to overcome the anisotropy field of the nanomagnet ( $\sim H_{ani}$ ). Therefore, the required spin current for hard-axis switching is typically larger than easy-axis switching with typical  $\alpha$  values much less than 1. However, the charge current  $(I_e)$  flowing through the SHM and the corresponding spin current $(I_s)$  can be expressed as  $I_S = \frac{A_{FM}}{A_{SHM}} \theta_{SH} [1 - sech(\frac{t_{SHM}}{\lambda_{sf}})] I_e$  [64]. Using simulation parameters listed in Table 3.1, we can obtain  $I_S \cong 2.2I_e$ . Therefore, spin current generated by SHE in our proposed structure has injection efficiency much larger than 100%, and hence, hard-axis switching can be performed with low energy cost.

#### 3.2.2 Evaluation

Spin information from input magnet is transmitted to the next magnet during the evaluation step. Charge current injected from T3 of SHM to T4 develops a non-equilibrium spin potential underneath the transmitting side, which in turn generates pure spin current along the NM spin channel. In the proposed SOT-DSL device structure, the magnetization of output magnets are initialized to its hard axis direction (+x or x) prior to the evaluation step. Hence, a small spin current is sufficient to switch the output magnets into their easy-axis direction. Also note that the polarity of the voltage applied across the T3 and T4 can result in an accumulation of either the

spins in the direction of FM or the opposite spins. Therefore, the structure shown in Fig. 3.1(a) can operate as an inverter when a positive voltage is applied, and operate as a buffer when a negative voltage is applied.

Just like ASL, SOT-DSL has analog characteristic of current mode switching. Thus, multiple magnets can be connected together to implement functions like majority evaluation, as shown in Fig. 3.1(b), whose magnetization switching behavior is shown in Fig. 3.2. Moreover, such majority gate can be used to implement NOR/OR and NAND/NOR by fixing one of its inputs and applying appropriate voltages [65].

## 3.3 Four-Phase Pipelined SOT-DSL

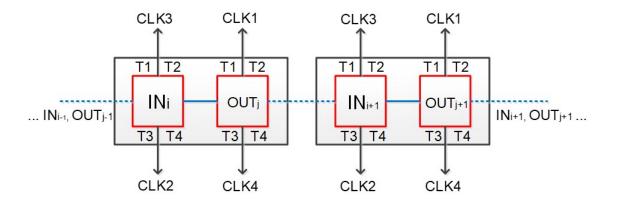

Fig. 3.3 shows multiple stages of SOT-DSL concatenated using spin channels. Each black box represents a logic block, and red boxes are input or output magnets.

Fig. 3.2. (a) SOT buffer/inverter (b) SOT-DSL majority gate.

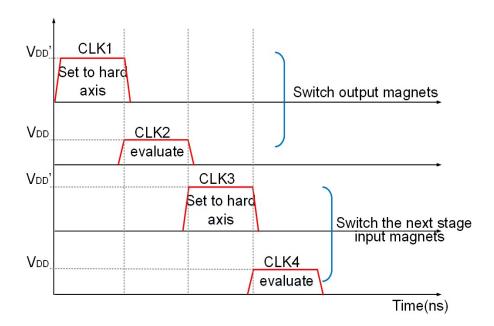

SHM above OUT magnets are connected to CLK1 and CLK4 whereas SHM above IN magnets are connected to CLK2 and CLK3. The operation is as follows: preset/evaluation, preset/evaluation, like a domino stack. As shown in Fig. 3.4, CLK1 and CLK3 are asserted to preset magnets to their hard axes (input current flows from T1 to T2, see Fig. 3.1) whereas CLK2 and CLK4 are asserted during logic evaluation (input current flows from T3 to T4, see Fig. 3.1). For each operation cycle, spin information stored in IN<sub>i</sub> magnets is transmitted to the IN<sub>i+1</sub> magnets. Since magnets are nonvolatile, extra latches or flip-flops are not required to implement pipeline operation.

Note that in Fig. 3.3, CLK1 presets the magnetizations of  $OUT_j$  magnets into their hard axes. Concurrently, CLK2 is asserted to pass spin information from  $IN_i$  magnets to their corresponding  $OUT_j$  magnets. This constitutes one stage in the logic pipeline. Similarly, spin information is passed to the next stage by asserting CLK3 which presets the  $IN_{i+1}$  magnet to its hard axis, and then asserting CLK4 to pass spin information from the  $OUT_j$  magnet to the  $IN_{i+1}$  magnets. The operation of each  $OUT_j$  magnet goes through a phase sequence of preset $\rightarrow$ to be evaluated $\rightarrow$ float $\rightarrow$ evaluate.

Fig. 3.3. Pipeline operation of several stages of SOT-DSL concatenated using spin channels (dash line). Black boxes represent one stage of SOT-DSL (see Fig. 3.1). Input and output magnets (red boxes) are connected by spin channel.