## VERTICAL TRIGATE METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR IN 4H - SILICON CARBIDE

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Rahul Padavagodu Ramamurthy

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2020

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Professor Dallas T. Morisette, Chair

School of Electrical and Computer Engineering

Professor James A. Cooper

School of Electrical and Computer Engineering

Professor Mark S. Lundstrom

School of Electrical and Computer Engineering

Professor Scott.D.Sudhoff

School of Electrical and Computer Engineering

#### Approved by:

Dr. Dimitrios Peroulis

Head of the School Graduate Program

To Amma and Appa, For you believe in me, I believe in myself...

#### ACKNOWLEDGMENTS

The journey to obtain this PhD has been a long and eventful one, the successful completion of which would not be possible without the involvement and support of many people. Hence, I would like to acknowledge several individuals each of whose contribution has made a significant impact in the culmination of this thesis.

First, I would like to thank Professor Dallas Morisette, for taking the chance with me as his first doctoral student, a gamble I hope this thesis justifies. The work that is represented here is only made possible because of the extraordinary support and exceptional guidance Prof. Dallas has provided. In addition to this, the opportunity to work on a number of very challenging and diverse problems has made for an intellectually stimulating and enjoyable PhD experience. I am also thankful to Prof Dallas for fostering and providing the resources to investigate some of the 'crazy' ideas I knocked on his door with. I will miss the countless hours spent in his office discussing out-of-the-box ideas and various aspects of solid-state physics.

I would also like to thank Professor James A. Cooper, Jr., for his outstanding technical guidance and valuable advice throughout this work. It has been an honor to work so closely with someone I so deeply admire and respect. The numerous insightful and thought-provoking discussions have not only added value to this project but also made me a better researcher. Thanks, are due to Professor Mark Lundstrom and Professor Scott Sudhoff for serving on my PhD committee and providing useful suggestions and inputs at critical junctures of this project.

I would like to thank Professor Michael Capano, Professor Sarit Dhar, Professor Len Feldman, Dr. Carl Johnson for the opportunity to collaborate on a number of interesting and challenging projects. I would like to express my gratitude to the staff members at the Birck Nanotechnology Centre, most notably Dan Hosler, Dave Lubelski, Kenny Schwartz, Bill Rowe, Jeremiah Shepard and Tim Miller for their assistance and co-operation during the intensive lab work required for this project. My colleagues and fellow graduate students for the lively conversations, advice and for keeping me sane through the many all-nighters we spent in the lab. I would like to specially acknowledge two people, Naeem Islam for being an integral part of the work described in this thesis and Dr. Noah Opondo for his partnership in implementing innovative solutions to numerous difficult problems. I have been fortunate to make many good friends and I thank them for making my life at Purdue a wonderful experience.

This achievement was made possible by the everlasting support and guidance by my parents, Medha Ramamurthy and P.B Ramamurthy. My sister Ashwini and brother-in-law Vikram for their constant encouragement. Finally, and most importantly, a special tribute goes out to my beautiful wife and soul mate, Krishnakali Chaudhuri who I was fortunate to meet along this journey. It has been your encouragement, support and endless patience through the vicissitudes of graduate life that has made this dream a reality.

## TABLE OF CONTENTS

|    |      | Pa                                            | age |

|----|------|-----------------------------------------------|-----|

| LI | ST O | F TABLES                                      | ix  |

| LI | ST O | F FIGURES                                     | х   |

| AI | BSTR | ACT                                           | xxv |

| 1  | INTI | RODUCTION                                     | 1   |

|    | 1.1  | Power Semiconductor Device                    | 2   |

|    | 1.2  | Silicon Carbide                               | 7   |

|    | 1.3  | Current Status of SiC Technology              | 10  |

|    |      | 1.3.1 Material Growth                         | 10  |

|    |      | 1.3.2 Power Devices                           | 11  |

| 2  | POW  | VER MOSFETs - THE SiC WORKHORSE               | 14  |

|    | 2.1  | Evolution                                     | 14  |

|    | 2.2  | Design of Power MOSFETs                       | 15  |

|    |      | 2.2.1 Unipolar Figure of Merit                | 15  |

|    |      | 2.2.2 SiC Power MOSFETs                       | 17  |

|    | 2.3  | Challenges and Limitations of SiC MOSFETs     | 27  |

|    | 2.4  | Current State-of-the-Art MOSFETs              | 30  |

|    | 2.5  | Need for innovation in the low voltage regime | 32  |

| 3  | THE  | TRIGATE SiC MOSFET                            | 34  |

|    | 3.1  | Channel Resistance Reduction - Approach       | 34  |

|    | 3.2  | Trigate Power DMOSFET - Concept               | 36  |

|    |      | 3.2.1 Performance Benefit                     | 39  |

|    | 3.3  | Trigate DMOSFET Performance Optimization      | 42  |

|    |      | 3.3.1 Trigate Trench Height                   | 43  |

|    | 3.4  | JFET Width Optimization                       | 48  |

vii

|   |     | 3.4.1  | Current Spreading Layer (CSL) Thickness and Doping $\ . \ . \ .$                        | . 49 |

|---|-----|--------|-----------------------------------------------------------------------------------------|------|

|   | 3.5 | Trigat | e Device Design and Mask Layout                                                         | . 52 |

| 4 | FAB | RICAT  | TION OF SIC TRIGATE MOSFETS                                                             | . 68 |

|   | 4.1 | Proces | ss technology development                                                               | . 70 |

|   |     | 4.1.1  | High energy ion implantation and masking                                                | . 71 |

|   |     | 4.1.2  | Sub-micron Gate Trenches                                                                | . 93 |

|   |     | 4.1.3  | Gate Stack                                                                              | . 97 |

|   |     | 4.1.4  | Ohmic Contacts                                                                          | 126  |

|   | 4.2 | Integr | ation into unified trigate MOSFET process                                               | 130  |

|   |     | 4.2.1  | Trigate Gen-1 Fabrication                                                               | 134  |

|   |     | 4.2.2  | Trench Etch                                                                             | 142  |

|   |     | 4.2.3  | Gate stack and Metal Contacts                                                           | 144  |

|   |     | 4.2.4  | Trigate Gen-2 Fabrication                                                               | 160  |

| 5 | ELE | CTRIC  | CAL CHARACTERIZATION OF TRIGATE DMOSFETS                                                | 168  |

|   | 5.1 | On-sta | ate Device Performance                                                                  | 169  |

|   |     | 5.1.1  | Measurement of Total Specific On-Resistance                                             | 170  |

|   |     | 5.1.2  | Specific On-Resistance vs. JFET Width                                                   | 175  |

|   |     | 5.1.3  | Specific Channel Resistance                                                             | 180  |

|   |     | 5.1.4  | Trigate MOSFET resistance reduction                                                     | 187  |

|   |     | 5.1.5  | Gate leakage current and oxide breakdown field $\ . \ . \ . \ .$                        | 190  |

|   | 5.2 | Blocki | ing Voltage Measurement                                                                 | 193  |

|   |     | 5.2.1  | Comparison of trigate $R_{on,sp}$ to state-of-the-art planar DMOS-<br>FETs and UMOSFETs | 194  |

|   | 5.3 | Param  | neter Extraction From PCMs and Test Structures                                          | 196  |

|   |     | 5.3.1  | Specific contact resistance                                                             | 197  |

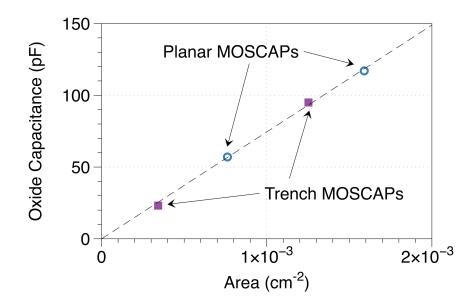

|   |     | 5.3.2  | Gate oxide thickness on planar and trench sidewall surfaces                             | 201  |

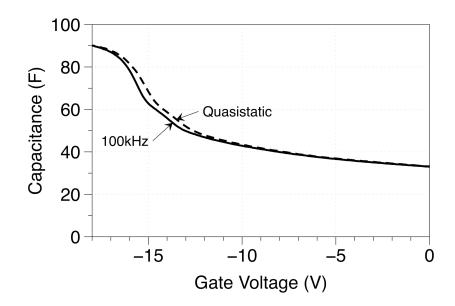

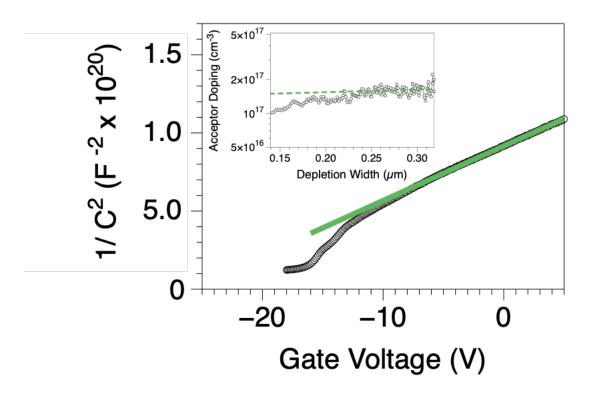

|   |     | 5.3.3  | P-base doping                                                                           | 204  |

|   |     | 5.3.4  | Effective and Field-Effect Mobility                                                     | 205  |

|   |      | 5.3.5   | Interface Trap Density                                                   | 216 |

|---|------|---------|--------------------------------------------------------------------------|-----|

| 6 | FUI  | URE V   | WORK                                                                     | 221 |

|   |      | 6.0.1   | Increase in channel length                                               | 222 |

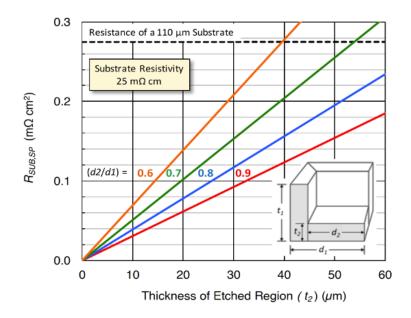

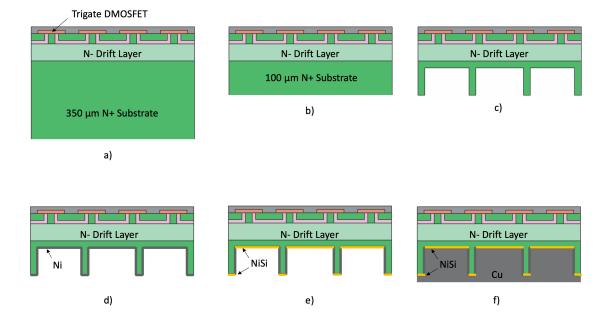

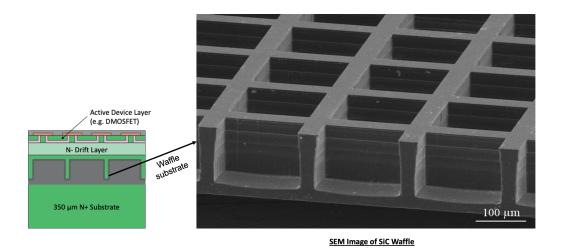

|   |      | 6.0.2   | Substrate resistance reduction using a waffle substrate $\ldots$ .       | 225 |

|   | 6.1  | Yield   | Improvement                                                              | 232 |

|   |      | 6.1.1   | Elimination of p+ contact polysilicon post $\ldots \ldots \ldots \ldots$ | 232 |

|   |      | 6.1.2   | Addition of edge-termination testers                                     | 235 |

|   |      | 6.1.3   | Reduced area devices                                                     | 236 |

|   |      | 6.1.4   | Field Oxide                                                              | 237 |

| А | Trig | ate Ger | n-1 Run Sheet                                                            | 244 |

| В | Trig | ate Ger | n-2 Run Sheet                                                            | 272 |

| R | EFER | ENCE    | S                                                                        | 297 |

Page

## LIST OF TABLES

| Tabl | e                                                                                                                                                                                                     | Pa | ıge |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 1.1  | Physical properties of important power semiconductors [12, 18–20]                                                                                                                                     | •  | 6   |

| 1.2  | Major extended defects in SiC epitaxial layers                                                                                                                                                        | •  | 10  |

| 2.1  | Optimal drift region design equations                                                                                                                                                                 | •  | 25  |

| 3.1  | Variation of JFET width and contact length within die                                                                                                                                                 | •  | 55  |

| 3.2  | List of test structures in process control module region of the trigate mask layout                                                                                                                   |    | 67  |

| 4.1  | P-type Base aluminum implant schedules                                                                                                                                                                | •  | 75  |

| 4.2  | Complete implant schedule of high energy nitrogen implant for n-source in the trigate Gen-1 and Gen-2 samples.                                                                                        |    | 80  |

| 4.3  | Polysilicon etch recipe in STS-ASE ICP-RIE                                                                                                                                                            | •  | 83  |

| 4.4  | Trigate Gen-1 sample information and nomenclature                                                                                                                                                     | 1  | .30 |

| 4.5  | Trigate Gen-2 sample information and nomenclature                                                                                                                                                     | 1  | .32 |

| 4.6  | CSL thickness information in Gen-1 trigate samples. $\ldots$                                                                                                                                          | 1  | .34 |

| 4.7  | Gen-1 trigate – $P^+$ implant profile $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                         | 1  | 41  |

| 4.8  | SiC etch recipe in Oxford Plasmapro 100 ICP-RIE                                                                                                                                                       | 1  | .44 |

| 5.1  | List of trigate device samples reported in this chapter                                                                                                                                               | 1  | .68 |

| 5.2  | Measured specific on-resistance at $V_G = 18$ V of trigate MOSFETs for<br>all device variations. Multiple MOSFETs for each device variation were<br>measured and the mean value for each is tabulated | 1  | .78 |

| 5.3  | Specific series and channel resistances of device I determined by method 1 and method 2. Performance benefit is defined by the ratio of the planar and trigate specific channel resistances.          | 1  | .89 |

| A.1  | Commonly used chemicals in the trigate fabrication process and their ven-<br>dors                                                                                                                     | 2  | 271 |

## LIST OF FIGURES

| Figu | Figure F                                                                                                                                                                                                                                                                                                                             |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

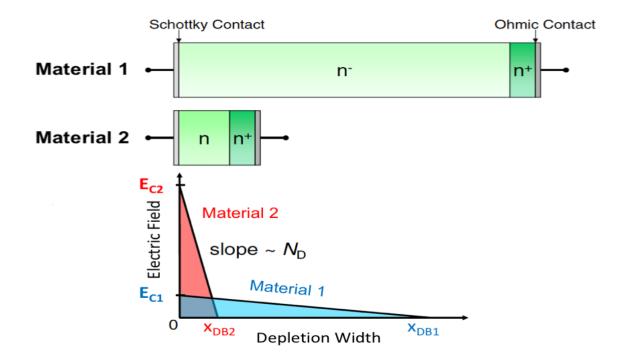

| 1.1  | Schottky diode in two material systems for the same blocking voltage and the electric field profile in reverse bias. Material 2 has a higher bandgap and critical electric field as compared to material 1                                                                                                                           | 3  |

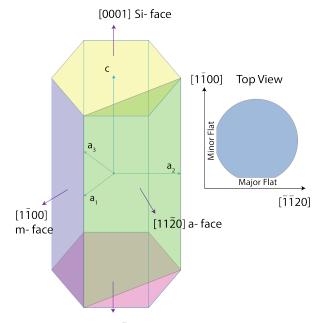

| 1.2  | Hexagonal unit cell in 4H-SiC with important faces highlighted. Typical SiC wafer orientation is also shown                                                                                                                                                                                                                          | 8  |

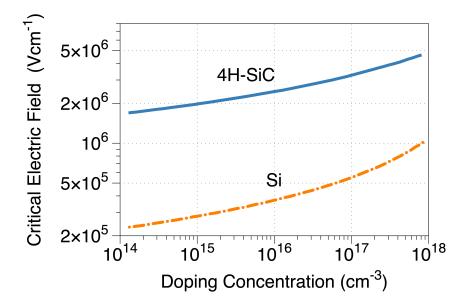

| 1.3  | Critical electric field of SiC and Si as a function of doping $\ldots \ldots \ldots$                                                                                                                                                                                                                                                 | 9  |

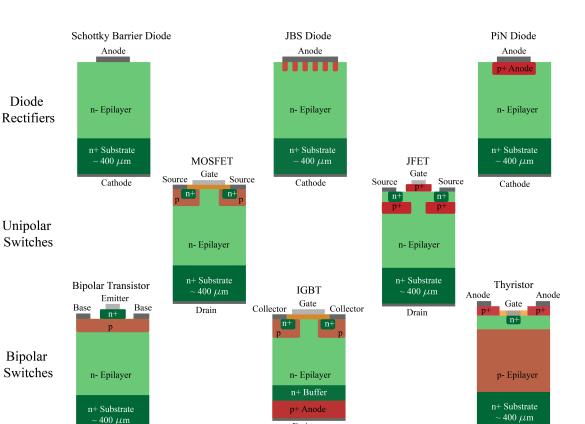

| 1.4  | Schematic structures of various SiC power devices currently developed                                                                                                                                                                                                                                                                | 12 |

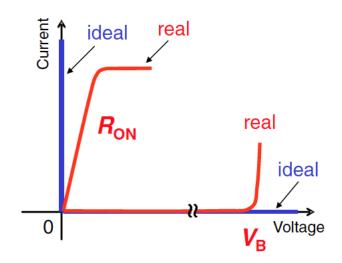

| 2.1  | Current–voltage characteristics of power switch                                                                                                                                                                                                                                                                                      | 16 |

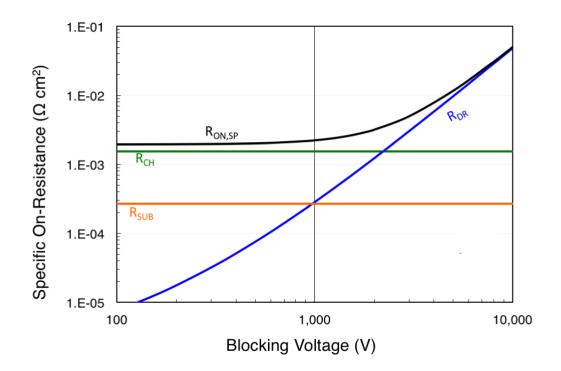

| 2.2  | Two different types of SiC MOSFETs: (a) DMOSFET and (b) UMOSFET                                                                                                                                                                                                                                                                      | 18 |

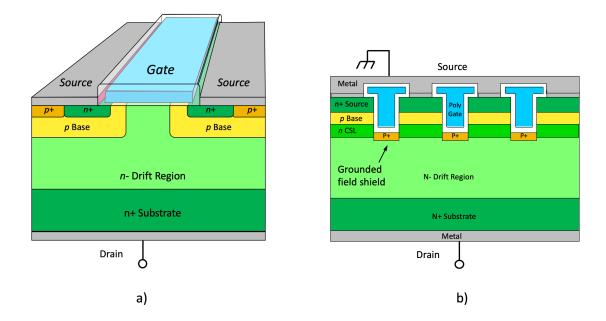

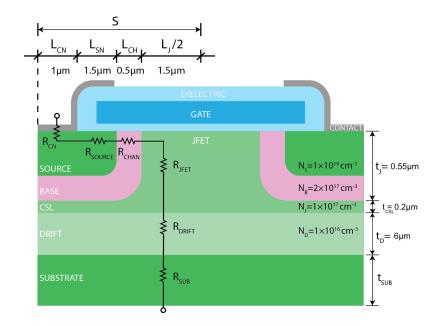

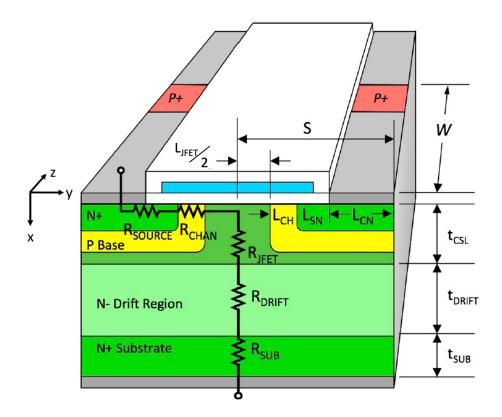

| 2.3  | Resistance components of DMOSFET device                                                                                                                                                                                                                                                                                              | 19 |

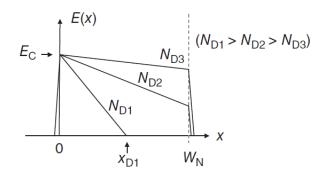

| 2.4  | Electric field profile under punch-through at lower doping concentrations .                                                                                                                                                                                                                                                          | 24 |

| 2.5  | Series resistance components in a DMOSFET                                                                                                                                                                                                                                                                                            | 27 |

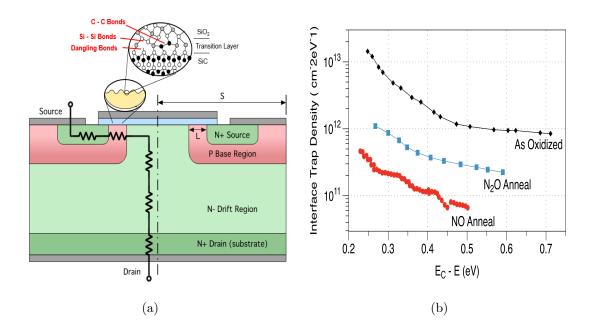

| 2.6  | (Non-idealities at the SiC/SiO <sub>2</sub> interface. a) Various defects and impurities at the SiC-SiO <sub>2</sub> interface leads to electronic defects in the MOSFET channel region and increases the channel resistance (b) Interface trap density in 4H-SiC MOS structures near conduction band measured using high-low method | 29 |

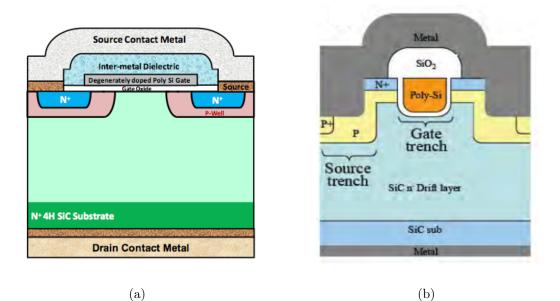

| 2.7  | Cross section illustration of commercially available SiC Power MOSFETs (a) Wolfspeed 3rd Generation DMOSFET (Released 2016) and (b) Rohm double-trench UMOSFET                                                                                                                                                                       | 31 |

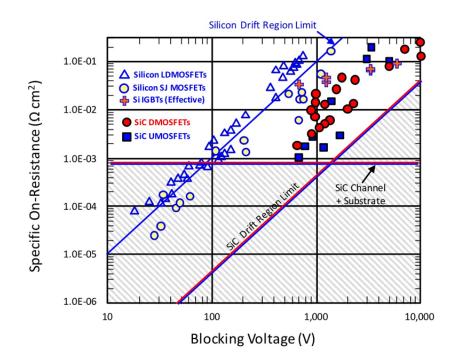

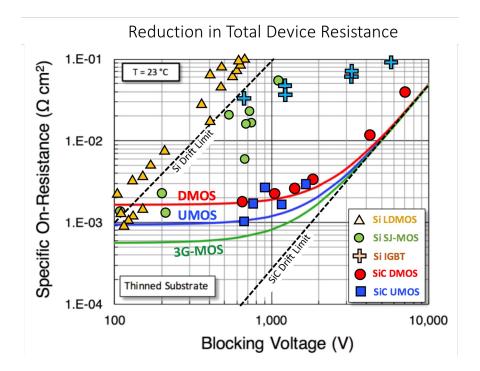

| 2.8  | Performance of silicon MOSFETs and IGBTs compared to the SiC MOS-<br>FETs. The limits imposed by channel, substrate and drift region resis-<br>tances are also depicted                                                                                                                                                              | 32 |

| 3.1  | Components of specific channel resistance in a vertical SiC DMOSFET                                                                                                                                                                                                                                                                  | 35 |

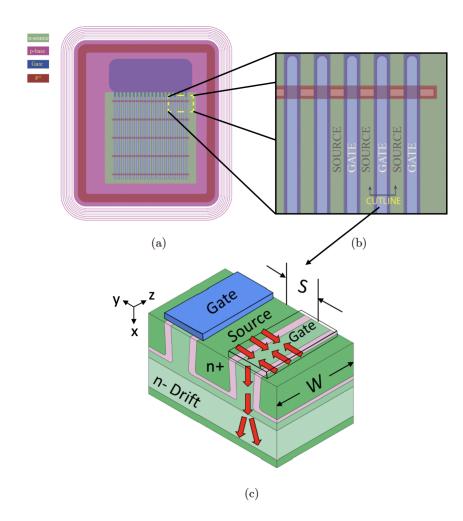

| 3.2  | DMOSFET design structure (a) Complete device, (b) Close-up view (c)<br>An isometric view from the cut-line of (b)                                                                                                                                                                                                                    | 36 |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pε | age |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

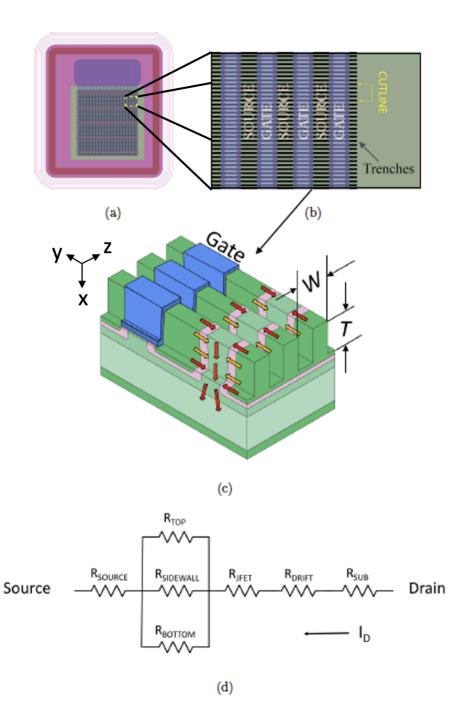

| 3.3  | Trigate MOSFET structure: (a) Complete device, (b) Close-up view of (a), and (c) An isometric view from the cut-line, and (d) Equivalent resistance circuit between source and drain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 38  |

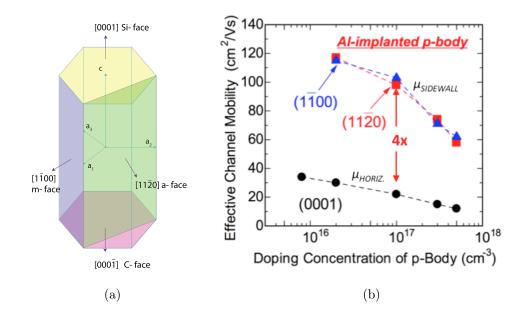

| 3.4  | Hexagonal unit cell of 4H-SiC and carrier mobility on differnt crystal planes. (a) Important crystal planes in SiC unit cell (b) Channel mobility along different crystal planes as a function of doping [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 41  |

| 3.5  | Performance of SiC trigate MOSFET compared to DMOSFETs and UMOS-<br>FETs, along with silicon power devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 42  |

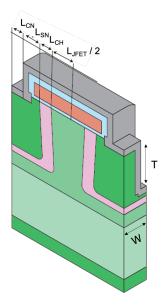

| 3.6  | Unit cell of a device and different dimensional components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 43  |

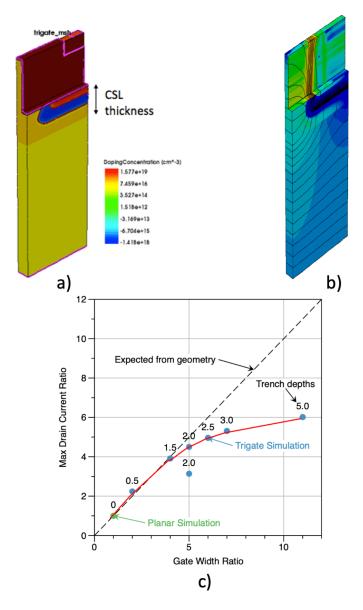

| 3.7  | Numerical simulation results of Trigate DMOSFET (a) Simulated unit cell.<br>(b) Unit cell in the on-state; color indicates current density and contours<br>are electron quasi-Fermi levels. The gate oxide thickness is 40 nm. The<br>applied gate voltage is $V_T + 6$ V, and the drain bias is 0.2 V (c) Drain<br>current ratio vs. gate width ratio as trench depth is increased from zero (a<br>planar device) to 5 µm. The JFET width is 3 µm for all points except the<br>lower point at a trench depth of 2 µm. For this point the JFET half-width<br>is 1 µm. Any current ratio greater than unity represents an improvement<br>over the conventional planar DMOSFET |    | 46  |

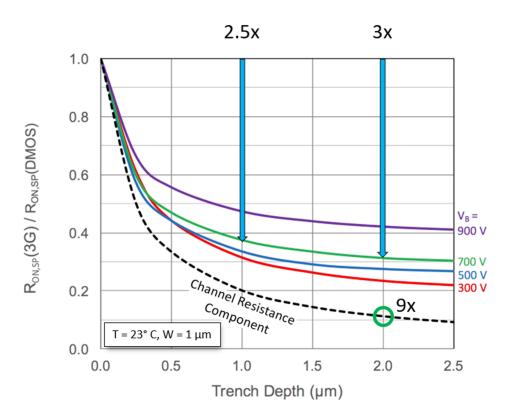

| 3.8  | Trigate MOSFET specific on-resistance compared with that of a standard DMOSFET as a function of trigate trench depth. Substrate is assumed to be thinned to 100µm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 47  |

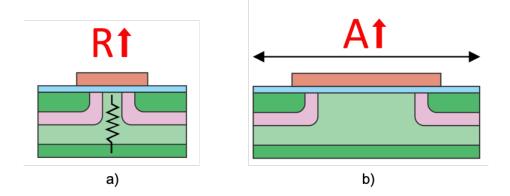

| 3.9  | Specific on-resistance due to non-optimum JFET region widths: (a) too narrow leads to high resistance (b) too wide leads to large area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 48  |

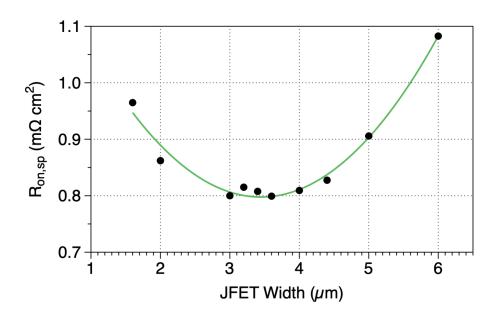

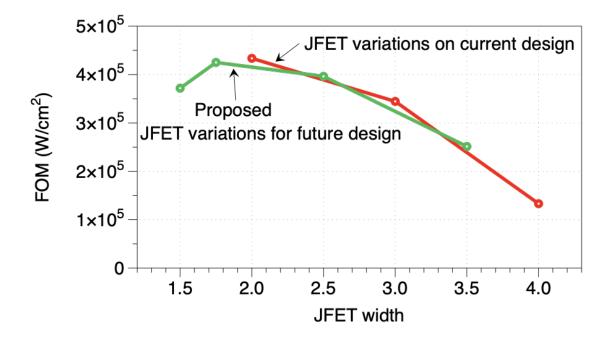

| 3.10 | Simulated specific on-resistance of a trigate MOSFET with variations in JFET width(LJFET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 49  |

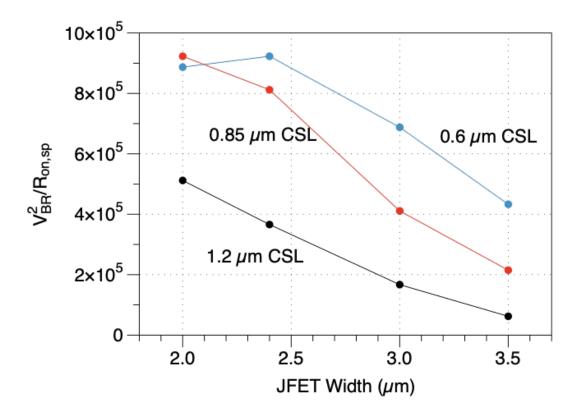

| 3.11 | Figure of merit vs. JFET width for different CSL thicknesses with a trench depth of 2 $\mu$ m and a CSL doping of $1 \times 10^{17} \text{cm}^3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 50  |

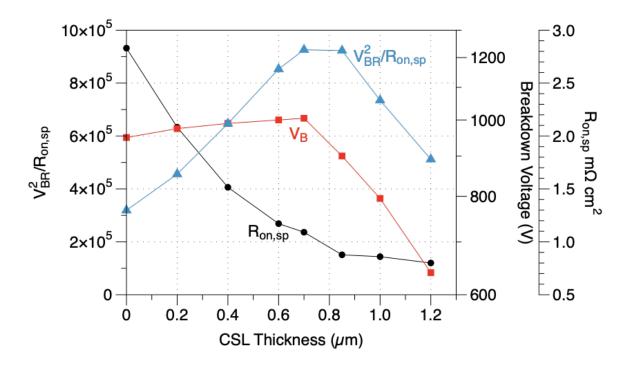

| 3.12 | Performance vs CSL thickness for a JFET width of 2.0 $\mu$ m, trench depth of 2.0 $\mu$ m and CSL doping of $1 \times 10^{17} \text{cm}^{-3}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 52  |

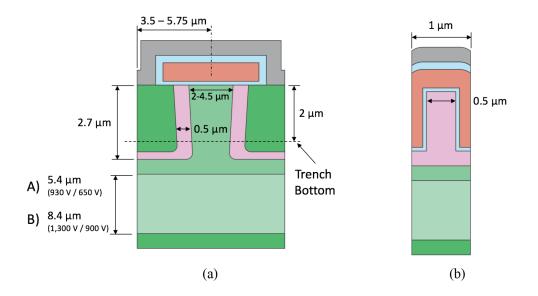

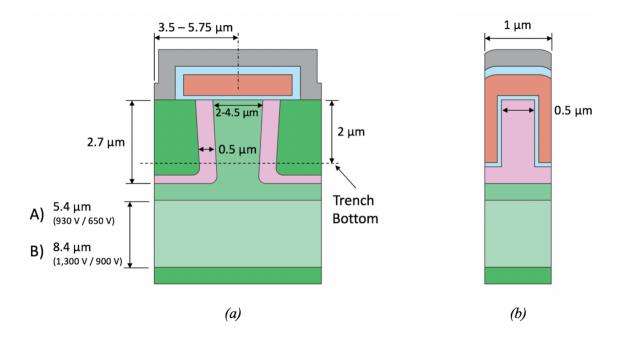

| 3.13 | Cross section of trigate MOSFET (a) through the fin centerline, and (b) perpendicular to the fin through the channel region                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 53  |

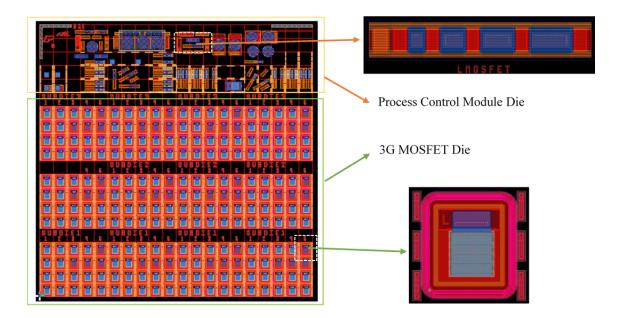

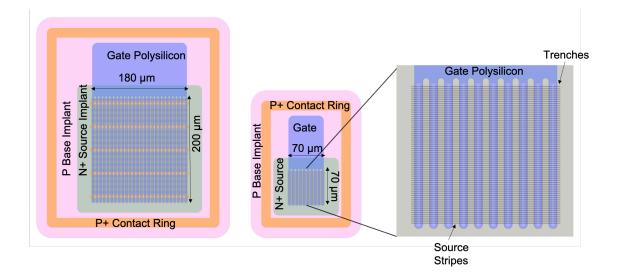

| 3.14 | The mask layout die containing both the device module and the process control module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 53  |

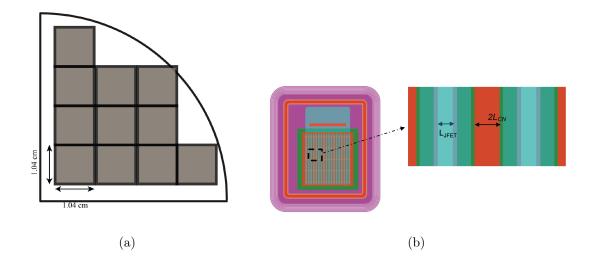

| 3.15 | Mask layout of trigate devices (a) Die distribution in a wafer quarter (b) Device module parameter definition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 54  |

| Figu | re Page                                                                                                                                                                                                                 | е |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

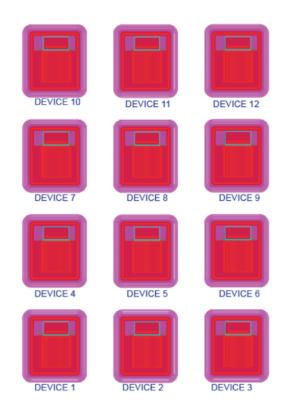

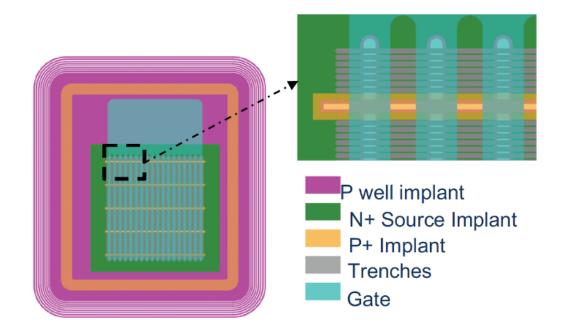

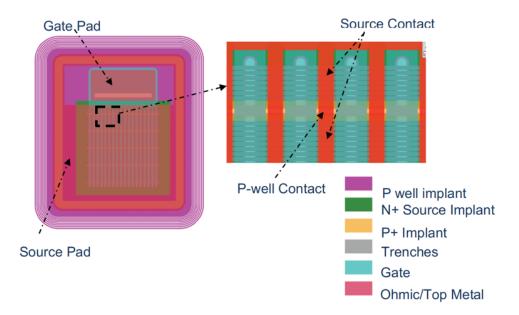

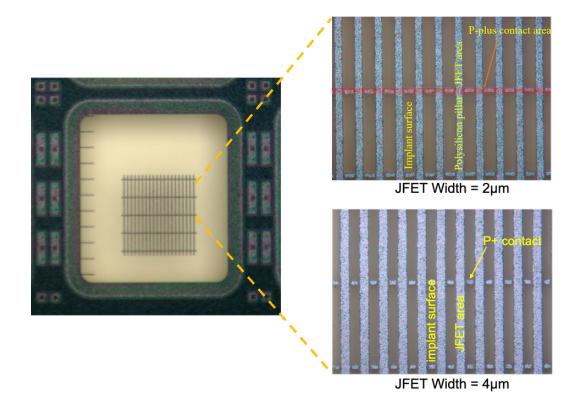

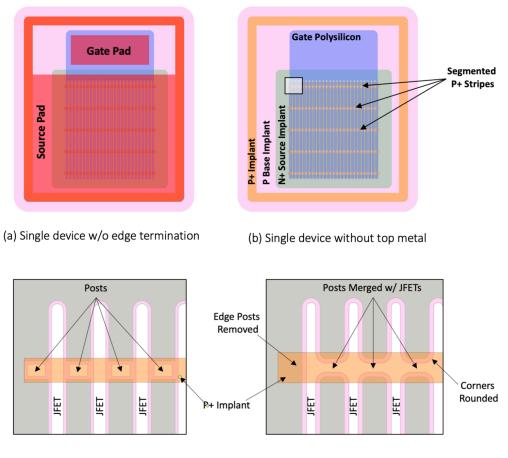

| 3.16 | Test die layout including variations in JFET width $L_{JFET}$ and source<br>contact length $L_{CN}$                                                                                                                     | 3 |

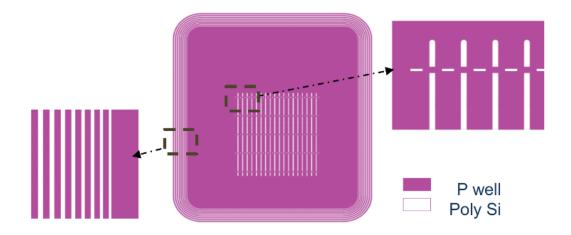

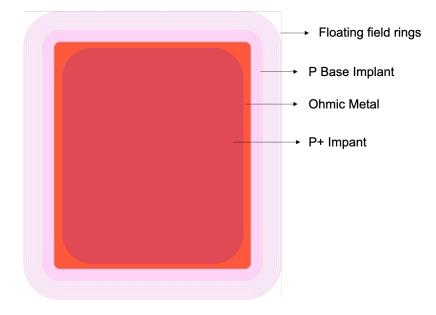

| 3.17 | P-well implant mask. The left-hand detail shows the floating field-ring edge termination, and the right-hand detail shows the interior of the active device. Aluminum will be implanted in the purple-shaded regions 57 | 7 |

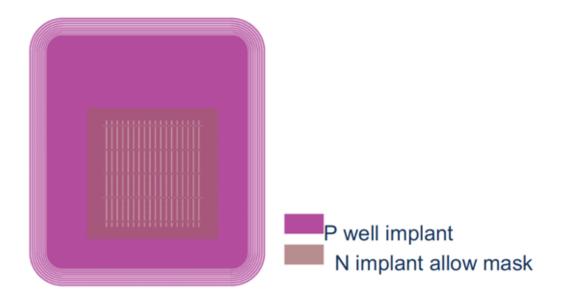

| 3.18 | N-implantation is allowed inside the light red region, where it is self aligned to the P-well implant to form the 0.5 µm channel                                                                                        | 8 |

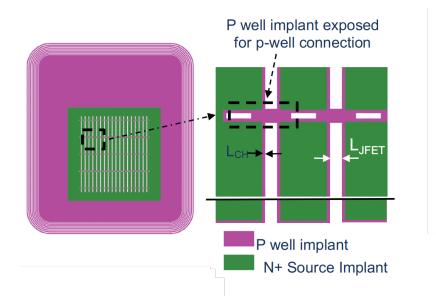

| 3.19 | Top view of the active region where he $N^+$ source implantation goes into<br>the green regions. The P-well underlines the $N^+$ implants                                                                               | 9 |

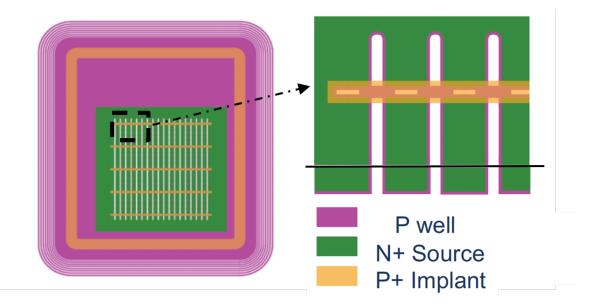

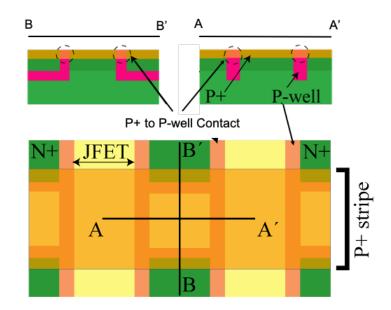

| 3.20 | The $P^+$ contact implant region is shown in gold. The detail at the right shows $P^+$ contact stripes running across the active area to ground the P-well.59                                                           | 9 |

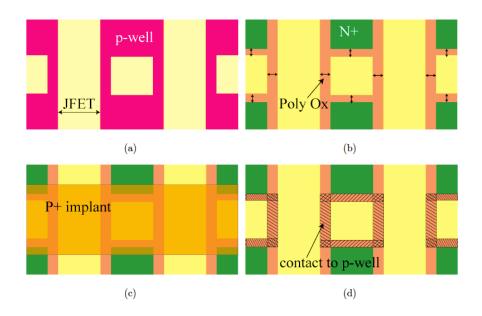

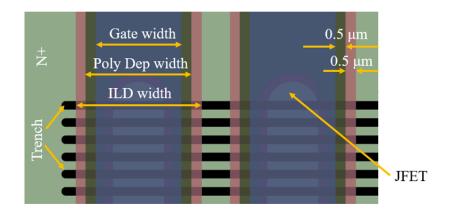

| 3.21 | $P^+$ implant formation (a) P-well implant and JFET region; (b) self-aligned 0.5 µm poly oxidation and source implantation; (c) $P^+$ implantation, and (d) $P^+/P$ -well overlap region                                | 0 |

| 3.22 | $P^+$ implant strip in the active area of the trigate DMOSFET and cross-<br>section view to illustrate the overlap of the $P^+$ and P-well regions 62                                                                   | 1 |

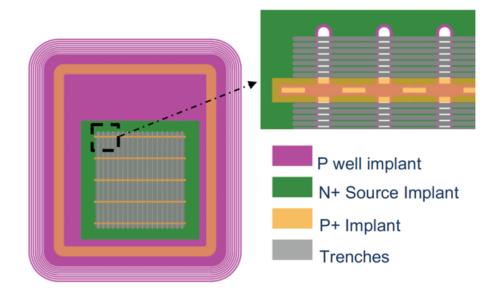

| 3.23 | Trench mask showing 0.5 µm wide trenches running horizontally 62                                                                                                                                                        | 2 |

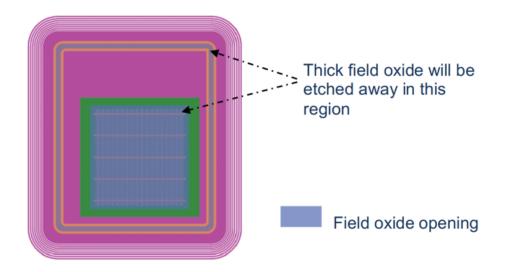

| 3.24 | Field oxide will be removed in the blue-shaded regions                                                                                                                                                                  | 2 |

| 3.25 | Etched polysilicon gate, shown in light blue. The detail on the right shows the gate runner in the active area                                                                                                          | 3 |

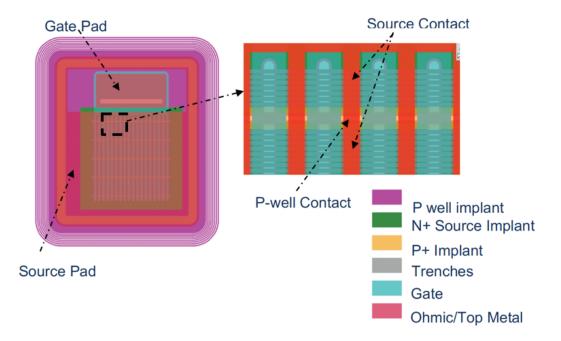

| 3.26 | Design and expected dimensions of the trigate MOSFET active area after<br>the ILD oxidation                                                                                                                             | 4 |

| 3.27 | Ohmic contacts and top metal mask                                                                                                                                                                                       | 5 |

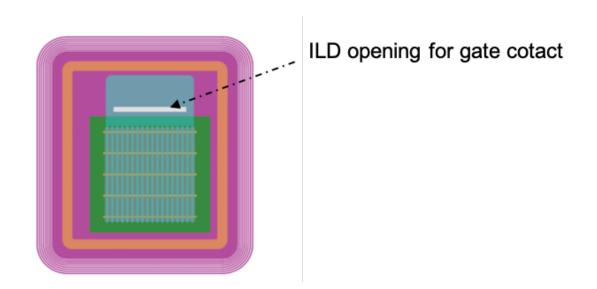

| 3.28 | Interlayer dielectric is removed in the white shaded region to provide con-<br>tact to the gate polysilicon                                                                                                             | 5 |

| 3.29 | Top metal mask that is used to isolate adjacent devices in the active area. 66                                                                                                                                          | 3 |

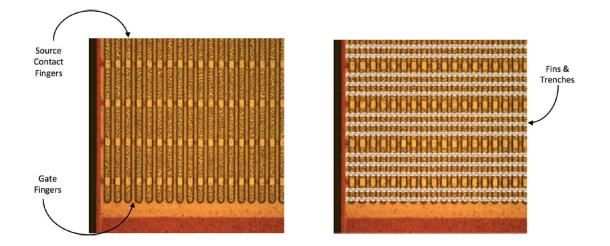

| 4.1  | Photo of a conventional planar DMOSFET (left) and the same device with<br>fins and trenches etched across the source and gate fingers (right). The<br>structure on the right is the proposed trigate (3G) MOSFET 69     | 9 |

| Figu | Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

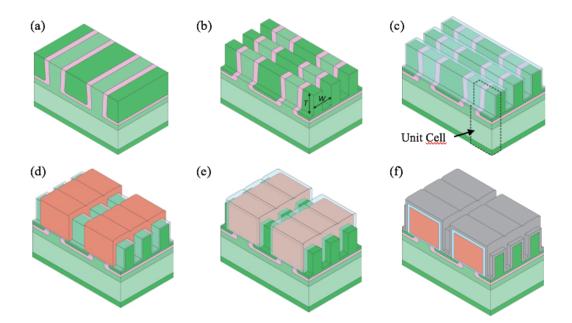

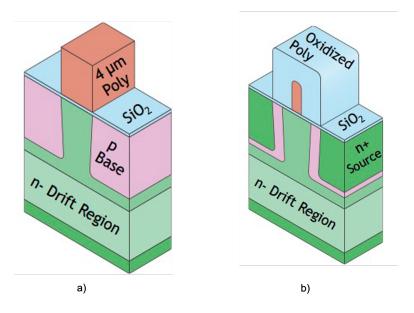

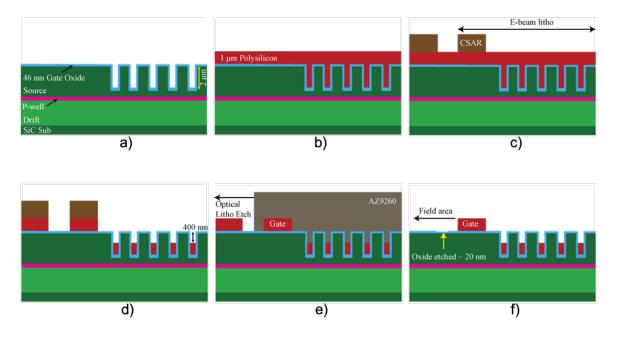

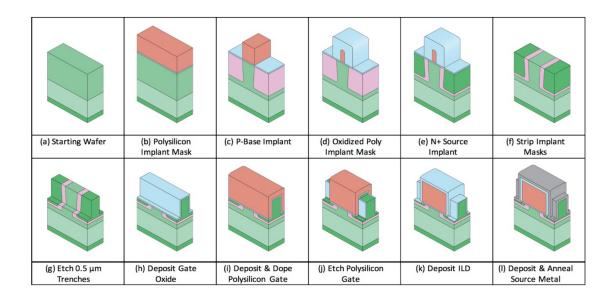

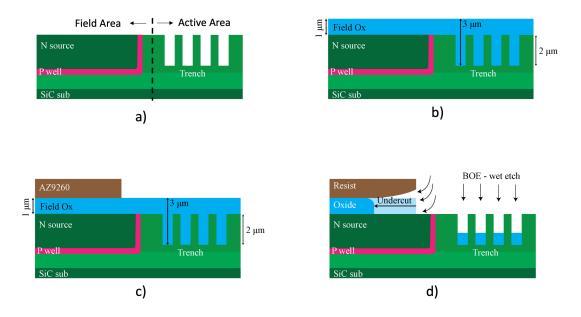

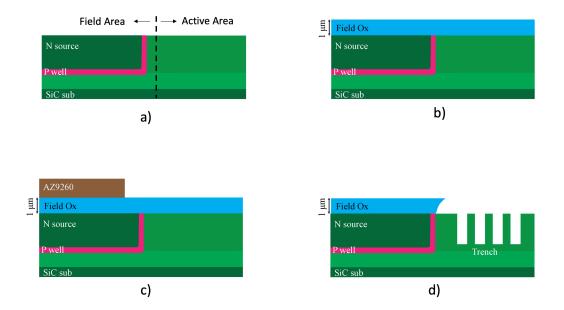

| 4.2  | Steps in the fabrication of the trigate power MOSFET: (a) implant P-base<br>and N+ source using a self-aligned process, (b) etch trenches perpendicular<br>to the source stripes, (c) deposit gate oxide and anneal, (d) deposit and<br>dope polysilicon gates to fill the trenches, then pattern poly into stripes,<br>(e) form a thick oxide over the gates by thermal oxidation and clear the<br>oxide over the exposed SiC by a short BHF dip, (f) deposit ohmic metal<br>and anneal to form source and base contacts, then deposit top metal over<br>entire active area | . 70 |

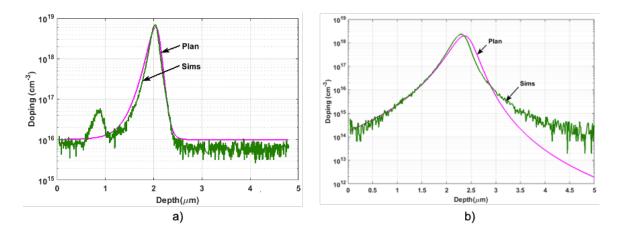

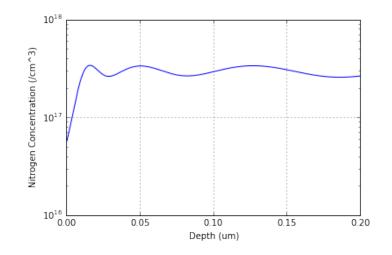

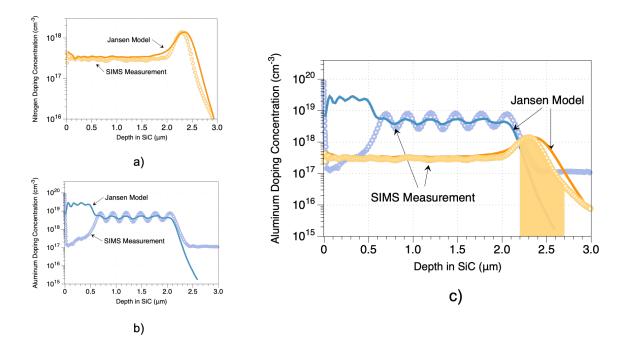

| 4.3  | Calibration of high energy implants with measured SIMS profiles. The purple lines are predictions using the Janson model [98], and the green curves are the measured profiles a) Implant profile of Al in SiC at a dose of $7.73 \times 10^{13}$ cm <sup>-2</sup> and an energy of 4.25 MeV, b) Implant profile of N in SiC at a dose of $1.35 \times 10^{14}$ cm <sup>-2</sup> and energy of 3.0 MeV.                                                                                                                                                                       | . 72 |

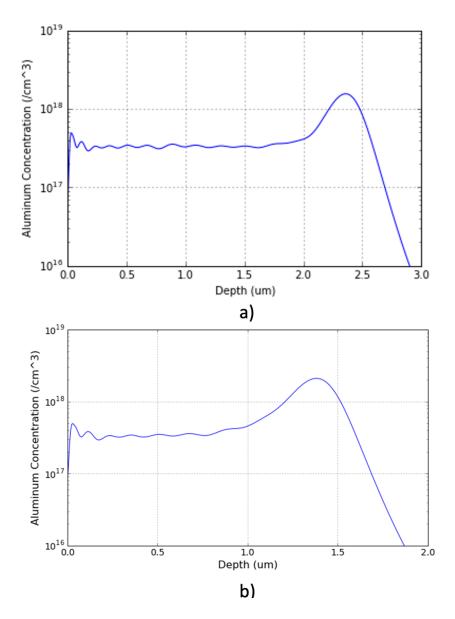

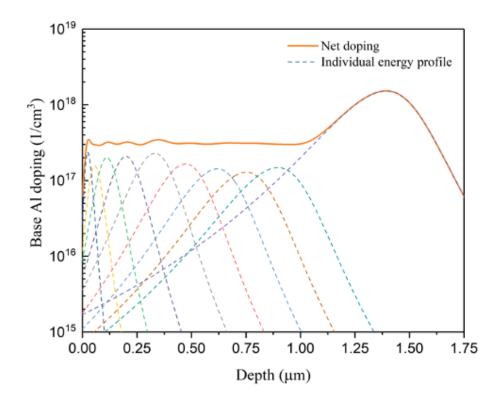

| 4.4  | Complete aluminum implant (P-base) profile for the trigate MOSFETs a) Gen-1 with 2 $~\mu m$ trench depth, b) Gen-2 with 1 $~\mu m$ trench depth                                                                                                                                                                                                                                                                                                                                                                                                                              | . 74 |

| 4.5  | Aluminum P-well implant profile at the surface of SiC without a screen oxide showing the tail of the low energy implant near the surface                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 76 |

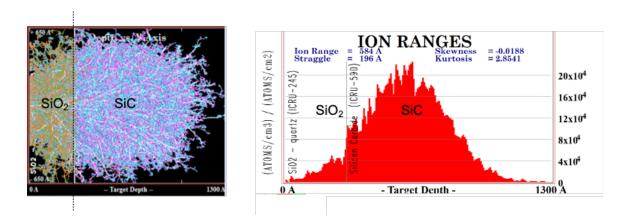

| 4.6  | Monte Carlo simulation of an aluminum implant using TRIM [97] with $30 \text{ nm SiO}_2$ screen oxide and an implantation energy of $20 \text{ keV} \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                             | . 76 |

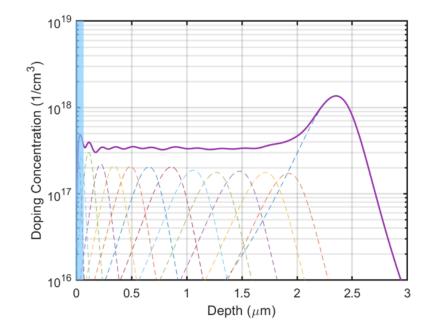

| 4.7  | Aluminum P-well implant profile. The dashed lines show the profile of each individual implant energy, while the solid line shows the resulting total concentration profile. The blue region represents the screen oxide $\therefore$                                                                                                                                                                                                                                                                                                                                         | . 77 |

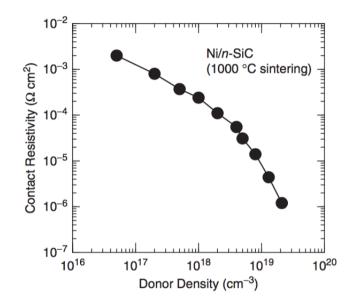

| 4.8  | Nickel silicide contact resistivity to N+ SiC [30] $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 78 |

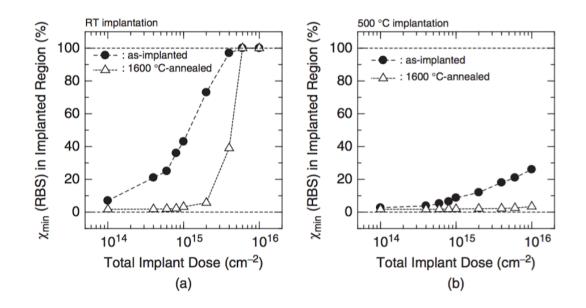

| 4.9  | Amorphization of SiC vs. dose and implant temperature of nitrogen im-<br>plant. [30]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 79 |

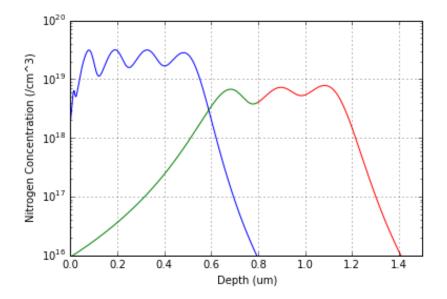

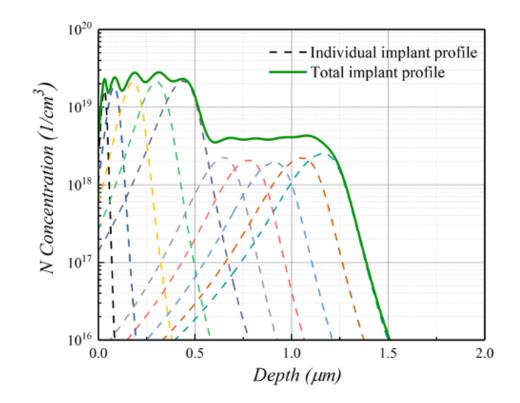

| 4.10 | Source region nitrogen implantation profile with the split high and low energy implantation schedules illustrated for the trigate Gen-2 samples with a 1 $\mu$ m trench depth $\ldots$                                                                                                                                                                                                                                                                                                      | . 79 |

| 4.11 | Calibration of ion implantation into polysilicon with highest energies for a<br>luminum and nitrogen used in the trigate MOSFETs. a) Measured profile of Al in a polysilicon mask with a dose of $7.73 \times 10^{13}$ cm <sup>-2</sup> and an energy of 4.25 MeV, b) Measured profile of N in a polysilicon mask with a dose of $1.35 \times 10^{14}$ cm <sup>-2</sup> and an energy of 3.0 MeV                                                                                                                                                                             | . 81 |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pag  | ;e |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|

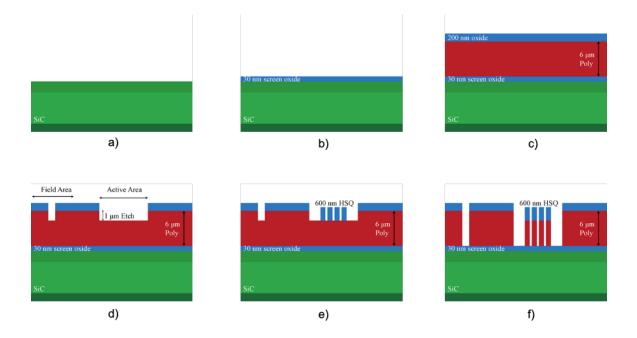

| 4.12 | Schematic images depicting the process flow to pattern the polysilicon<br>mask using method-1. a)Clean SiC wafer, b)Screen oxide grown by ther-<br>mal oxidation, c) Deposition of polysilicon by LPCVD and thermal oxida-<br>tion to form 200nm of oxide, d)Optical lithography and polysilicon etch to<br>form temporary alignment marks, e) E-beam lithography to pattern the<br>polysilicon mask in the active area using the alignment marks defined in<br>the previous step, f) Polysilicon etch to form the polysilicon mask for the<br>P-base implant. | . 8  | 4  |

| 4.13 | Schematic images depicting the process flow to pattern the polysilicon mask using method-2. a) Clean SiC wafer, b) Screen oxide and deposition of 5 µm thick polysilicon by LPCVD, c)Electron beam lithography in the active and field areas using CSAR resist, d)Polysilicon etch to form the polysilicon mask for the P-base implant.                                                                                                                                                                                                                        | . 8  | 5  |

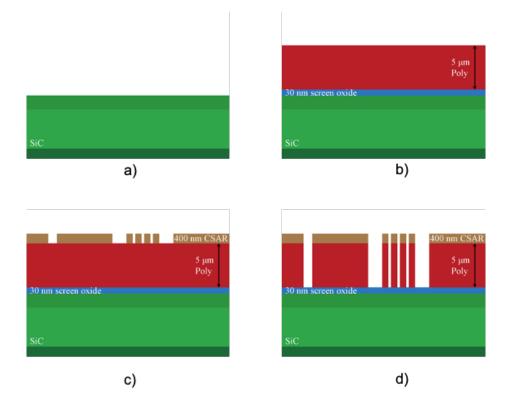

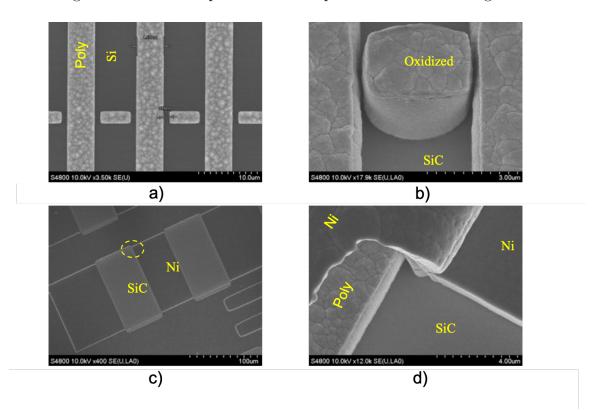

| 4.14 | SEM images of the polysilicon etch using the Bosch process in the ICP STS ASE for method-1 and method-2                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 8  | 6  |

| 4.15 | Illustration of the n-source implant self-aligned to the P-base. a) Polysil-<br>icon mask pattern during the aluminum P-base implant, b) Thermal ex-<br>pansion of the polysilicon mask to self-align the n-source implant to the<br>P-base implant                                                                                                                                                                                                                                                                                                            | . 8  | 57 |

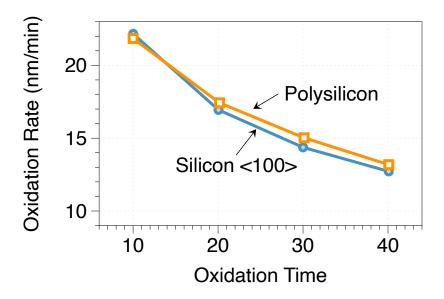

| 4.16 | Pyrogenic oxidation of polysilicon and crystalline silicon $<100>$ at $1100^{\circ}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C. 8 | 8  |

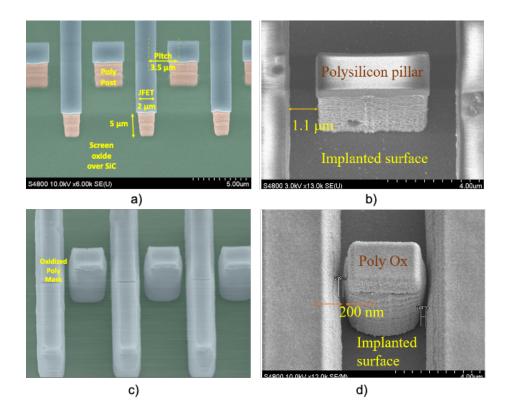

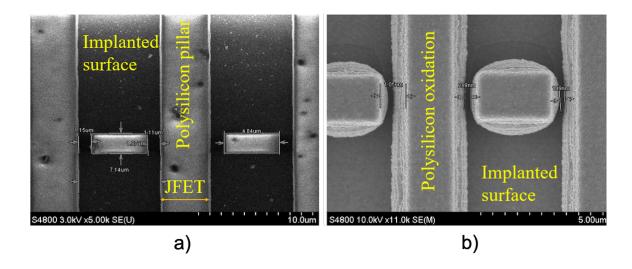

| 4.17 | SEM images of polysilicon used to mask base and source implants. a) Polysilicon pillars and post mask used for base implant, b) Expansion of polysilicon mask after thermal oxidation as part of the self-aligned short-channel process                                                                                                                                                                                                                                                                                                                        | . 8  | 9  |

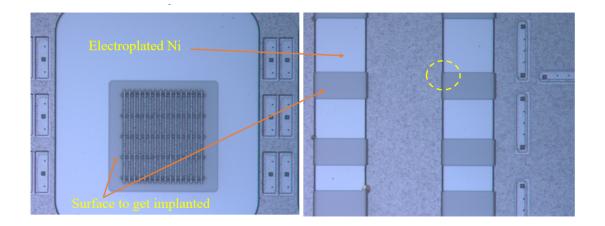

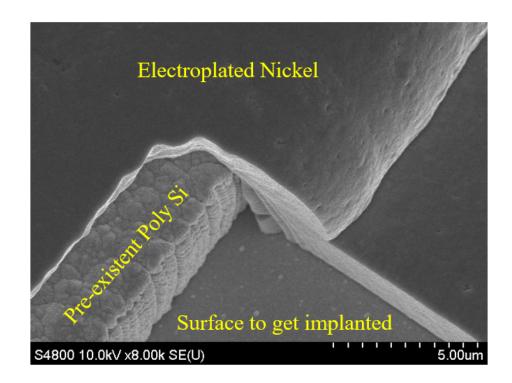

| 4.18 | Photomicrograph image of the electroplated Ni N+ block mask for the trigate (left) and PCM test structures (right).                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 9  | 0  |

| 4.19 | SEM image of circled region in Figure 4.18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 9  | 0  |

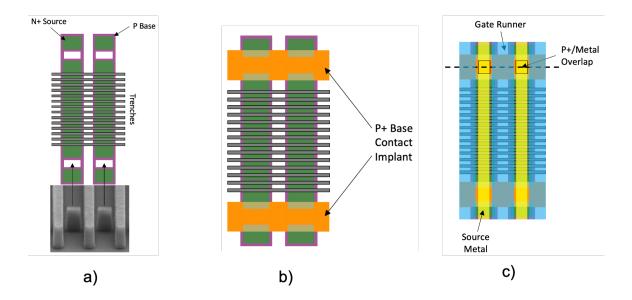

| 4.20 | Schematic illustration of the trigate active area. a) Base and source implants, b) Segmented P+ base contact implant, c) Completed device with gate runners and source ILD windows.                                                                                                                                                                                                                                                                                                                                                                            | . 9  | 2  |

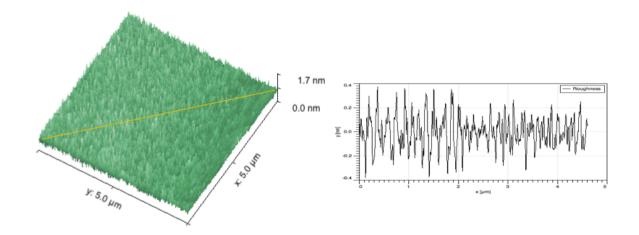

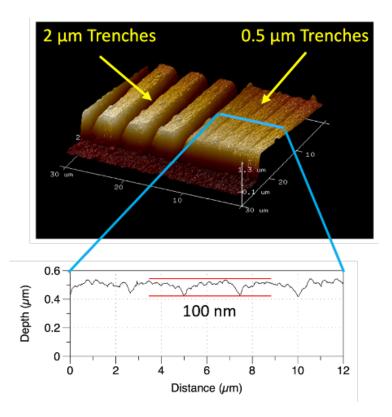

| 4.21 | 3D AFM image of across the source and base regions after high energy implantation and activation anneal. The roughness along the cutline (a) is shown in (b). A smooth SiC surface is recovered after the activation anneal process with a surface roughness(RMS) of 0.24 nm                                                                                                                                                                                                                                                                                   | . 9  | 3  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |    |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                  | Page  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

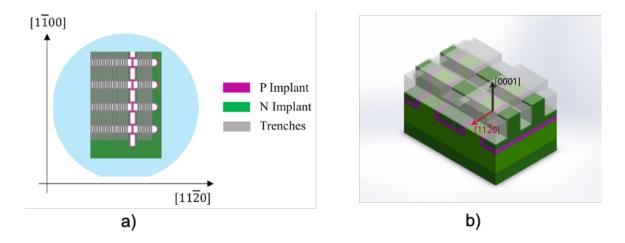

| 4.22 | Trench etch for trigate devices (a) JFET, source, and trench orientation with respect to the wafer flats and crystallographic directions. Trench sidewalls lie nominally on $\{11\overline{2}0\}$ , or a-face planes, (b) 3D isometric view of a unit cell of the trigate MOSFET, showing the relative orientation of these features with respect to primary crystollographic directions $\ldots$ . | . 94  |

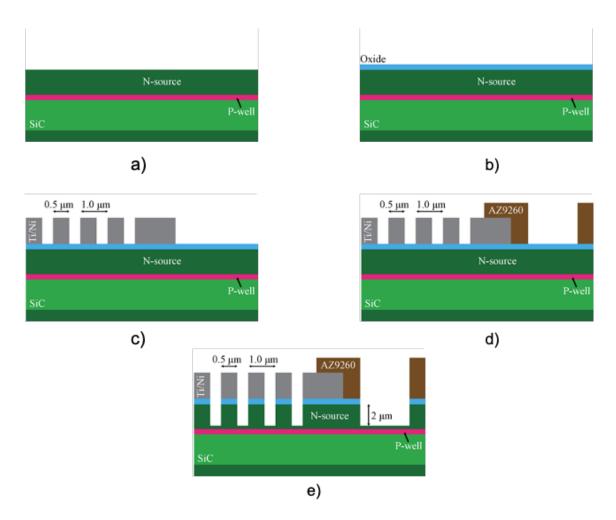

| 4.23 | Trench etch proess flow: (a) Wafer with n-source and P-well implant, (b) Growth of thin layer sacrificial oxide, (c) e-beam lithography and Ti/Ni (10/200 nm) metal liftoff in the active region, (d) 8-10 $\mu m$ thick AZ9260 photoresist pattern in the field and PCM regions, (e) SiC plasma etch.                                                                                              | . 95  |

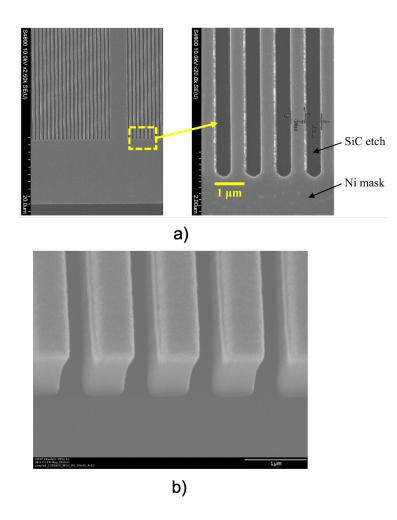

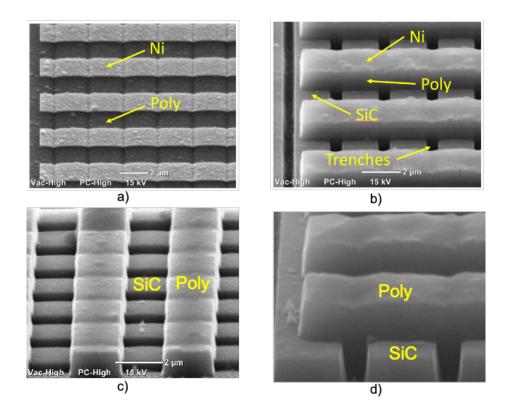

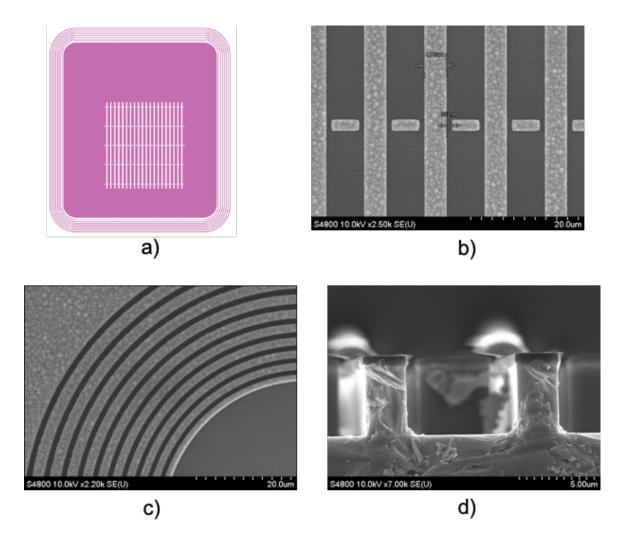

| 4.24 | SEM images of SiC trenches. a) Top view, b) Tilted SEM image of the SiC trench etch to form the trigate devices                                                                                                                                                                                                                                                                                     | . 96  |

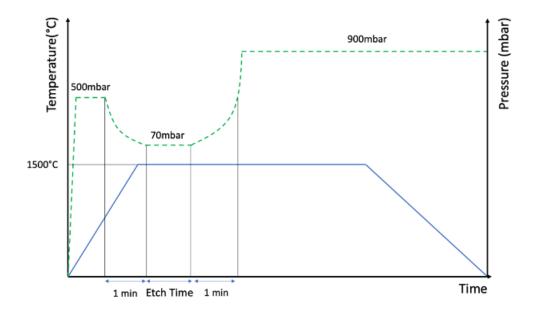

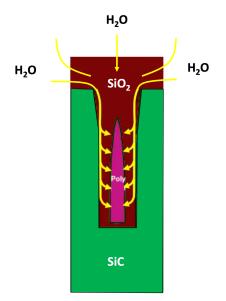

| 4.25 | Process flow of the ${\cal H}_2$ etch process using the Epigress CVD chamber $~$ .                                                                                                                                                                                                                                                                                                                  | . 99  |

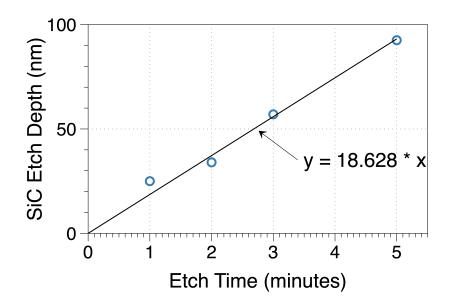

| 4.26 | SiC etch depth in $H_2$ ambient at 1500°C and 70 mbar as a function of etch time. The etch time is defined in Figure 4.25                                                                                                                                                                                                                                                                           | 100   |

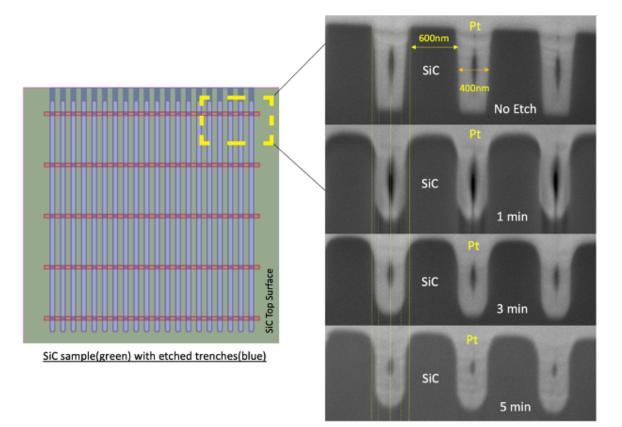

| 4.27 | FIB cross section of $H_2$ etched trenches at 1500°C and 70mbarr for different etch time. The etch time is defined in Figure 4.25. Trench corner rounding is observed as the etch time is increased                                                                                                                                                                                                 | 101   |

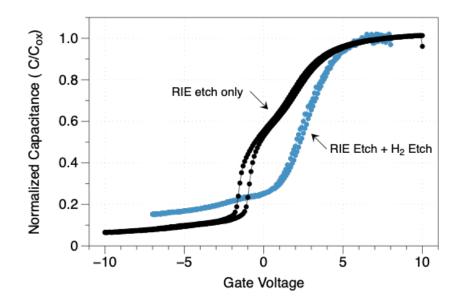

| 4.28 | CV characteristics measured at 100 kHz for $H_2$ etched and unetched trench MOSCAPs.                                                                                                                                                                                                                                                                                                                | 102   |

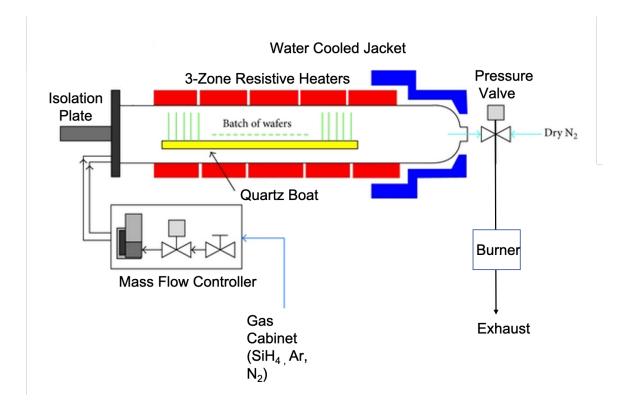

| 4.29 | Apparatus for LPCVD deposition of polysilicon using a quartz tube furned                                                                                                                                                                                                                                                                                                                            | e.105 |

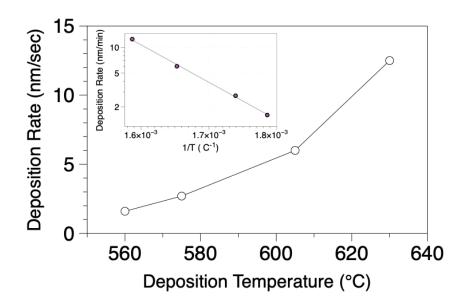

| 4.30 | Deposition rate of LPCVD polysilicon at a deposition pressure of 130 mTorr for different deposition temperatures                                                                                                                                                                                                                                                                                    | 106   |

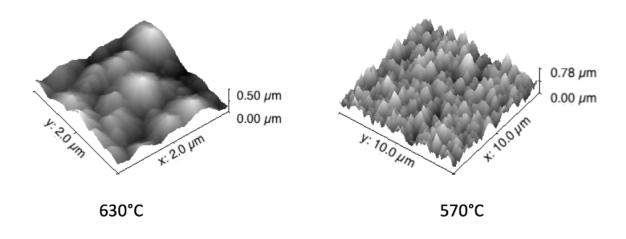

| 4.31 | Surface roughness of the LPCVD polysilicon film deposited at $630^{\circ}$ C and $570^{\circ}$ C                                                                                                                                                                                                                                                                                                    | 106   |

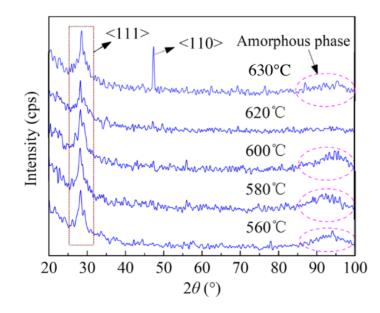

| 4.32 | XRD diffraction signal of LPCVD polysilicon film deposited at differnt temperatures. Signal from all the crystal faces is seen at $630^{\circ}C$                                                                                                                                                                                                                                                    | 107   |

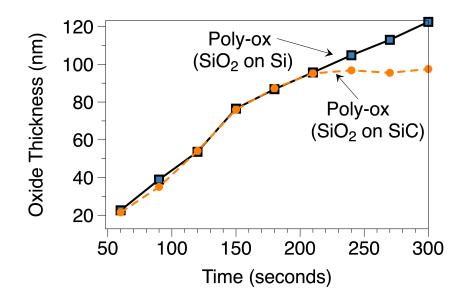

| 4.33 | Calibration of polysilicon oxidation on Si and SiC samples to ensure com-<br>plete but not excess oxidation of the deposited polysilicon film                                                                                                                                                                                                                                                       | 108   |

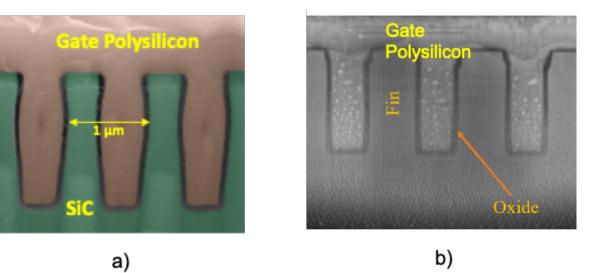

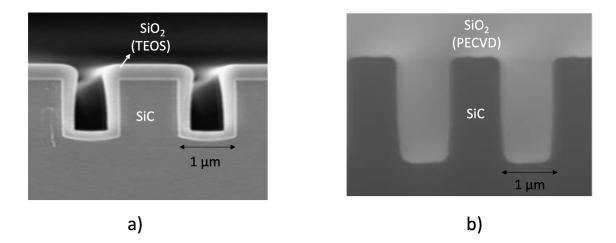

| 4.34 | Cross section SEM images showing conformal oxide over SiC trenches using the poly-ox process a) Trench depth of 2 $\mu m$ b)Trench depth of 1 $\mu m.$ .                                                                                                                                                                                                                                            | 109   |

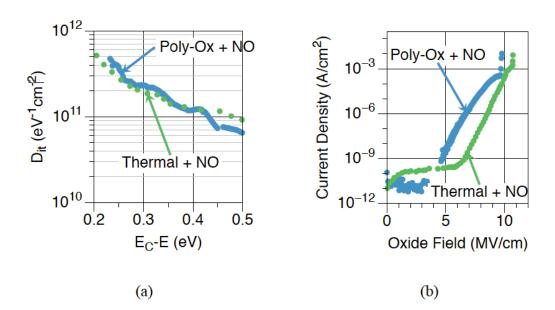

| 4.35 | Electrical characterization of an oxidized polysilicon gate oxide with an NO anneal. a) Interface trap density $(D_{it})$ vs energy with respect to conduction band measured using high-low technique, b) Gate leakage current as a function of oxide field. The measured $D_{it}$ and dielectric breakdown of the poly-ox process is comparable to the standard thermal oxide, b) $\ldots$ .       | 110   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

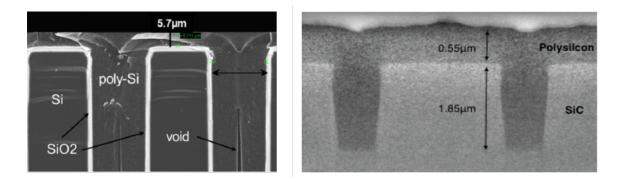

| 4.36 | Cross section SEM images of SiC trenches after polysilicon depositon and planarization.a) Polysilicon deposited at 630°C and 500mbarr, b) Polysilicon deposited at 630°C and 150mbarr.                                                                                                                                                                                                                                                                                                                   | 113   |

| 4.37 | AFM scan of SiC trenches after polysilicon deposition and planarizaiton                                                                                                                                                                                                                                                                                                                                                                                                                                  | 114   |

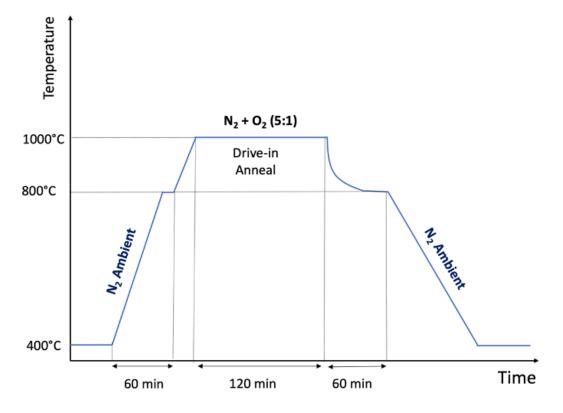

| 4.38 | Spin-on dopant drive-in process flow used for polysilicon gates                                                                                                                                                                                                                                                                                                                                                                                                                                          | 116   |

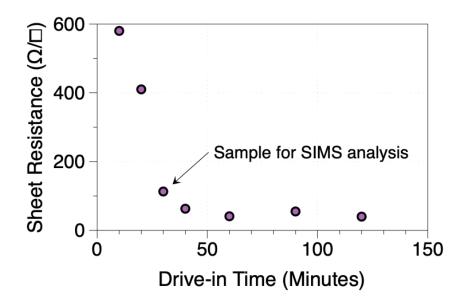

| 4.39 | Sheet resistance of a 2 µm thick polysilicon layer as a function of drive-in time at 1000°C.                                                                                                                                                                                                                                                                                                                                                                                                             | 117   |

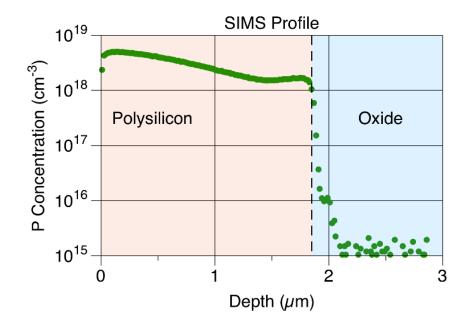

| 4.40 | SIMS profile of phosphorus in a $\sim 2 \ \mu m$ thick LPCVD deposited polysil-<br>icon film doped by diffusion from a spin-on dopant source at 1000°C for<br>30 minutes using the process depicted in Figure 4.38                                                                                                                                                                                                                                                                                       | 118   |

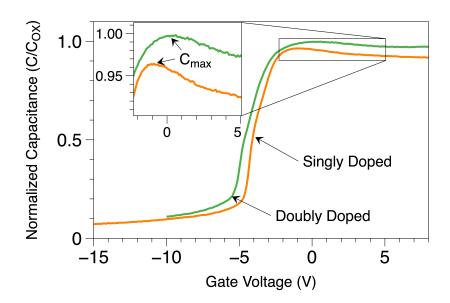

| 4.41 | Capacitance vs Gate Voltage for single and double doping of polysilicon gate.                                                                                                                                                                                                                                                                                                                                                                                                                            | 119   |

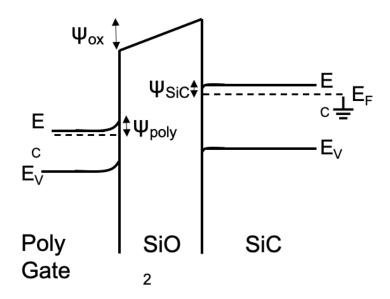

| 4.42 | Band diagram of a polysilicon gated N-type MOS capacitor in accumulation                                                                                                                                                                                                                                                                                                                                                                                                                                 | n.120 |

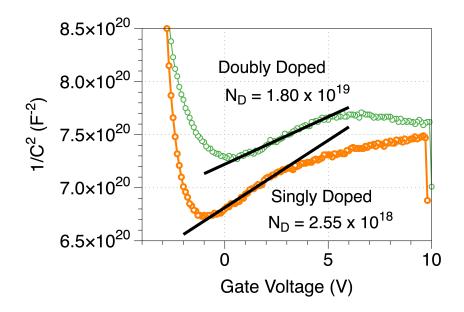

| 4.43 | Plot of $1/C^2$ vs gate voltage for a N-type MOS capacitor with a signly and doubly doped polysilicon gate                                                                                                                                                                                                                                                                                                                                                                                               | 123   |

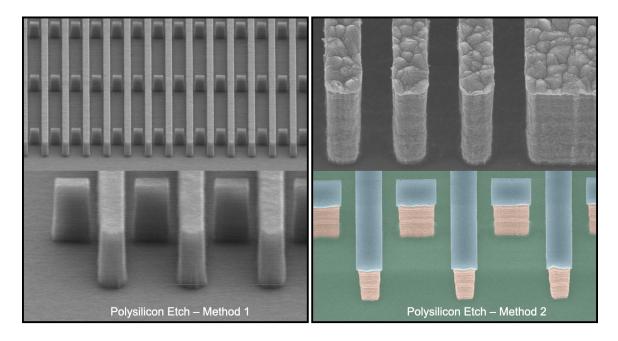

| 4.44 | Polysilicon gate etch process flow illustrated by cross-sections along the line A-A' in Figure 3.24 (a) trench etch and poly-ox gate oxide deposition, (b) 1 µm thick polysilicon deposition using LPCVD and degenerate doping by spin-coating and diffusion, (c) e-beam lithography using CSAR resist and 30 nA exposure, (d) poly gate etch using the Bosch process and the CSAR mask, (e) AZ9260 pattern for field area polysilicon etch, and (f) Polysilicon etch in field and test structure areas. | 124   |

| 4.45 | SEM images of the polysilicon gate etch using $\rm SF_6/O_2$ RIE is the STS-AOE ICP. (a) Nickel mask patterned using e-beam lithography over planarized SiC trenches, (b)-(d) Polysilicon gate fingers defined over SiC trenches.                                                                                                                                                                                                                                                                        | 125   |

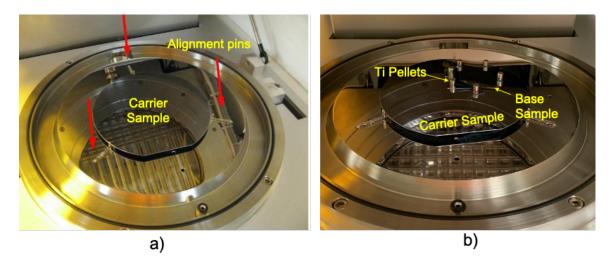

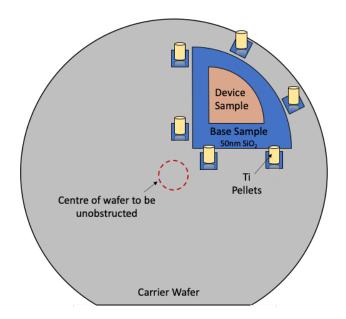

| 4.46 | Sample loading sequence in the Jipelec RTA for ohmic anneal. a) Carrier wafer loading and alignment, b) Base sample with Ti pellets for $O_2$ gettering                                                                                                                                                                                                                                                                                                                                                  | ng126 |

| 4.47 | Sample arrangement and setup in the Jipelec RTA for ohmic anneal                                                                                                                                                                                                                                                                                                                                                                                                                                         | 128   |

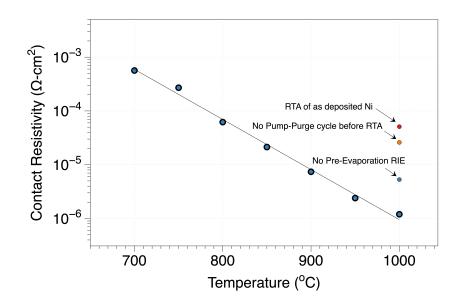

| 4.48 | Contact resistivity as a function of annealing temperature                                                                                                                                                                                                                                                                                                                                                                                                                                               | 129   |

| 4.49 | Cross sections of the trigate MOSFET (a) through the fin centerline and (b) perpendicular to the fin through the channel region                                                                                                                                                                                                                                                                                                                                                                          | 131   |

| 4.50 | Pictorial depiction of the major process steps in the fabrication of trigate MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                     | 132   |

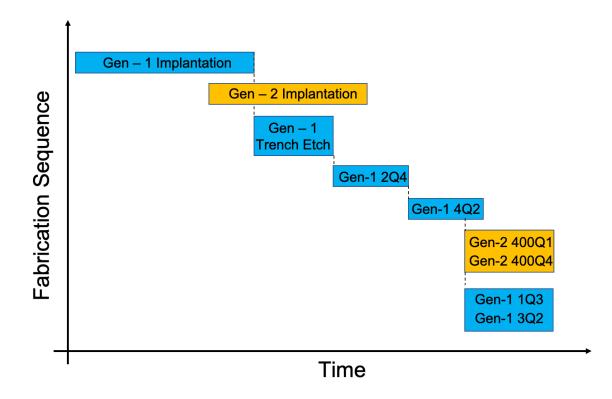

| 4.51 | Fabrication sequence of the Gen-1 and Gen-2 trigate samples                                                                                                                                                                                                                                                                                                                                                                                                                                              | 133   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.52 | Polysilicon patterned in the active area for the P-base implant mask                                                                                                                                                                                                                                                                                                                                                      | 135  |

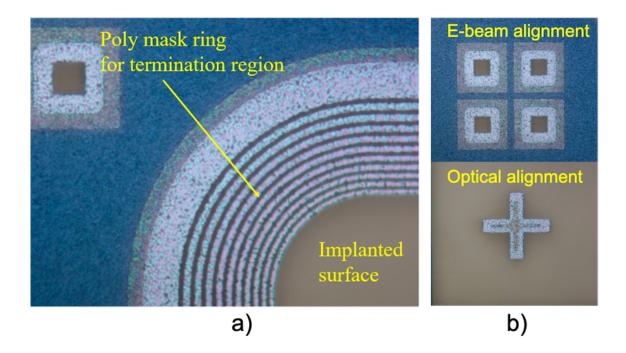

| 4.53 | SEM images of floating field rings and alignment marks in Gen-1 sample 4Q2 (a) P-type islands patterned by e-beam lithography in the FFR region, (b) SEM image of the alignment between the optical and electron beam layers. The process parameters and alignment is discussed in Section 4.1.1.2.                                                                                                                       | 136  |

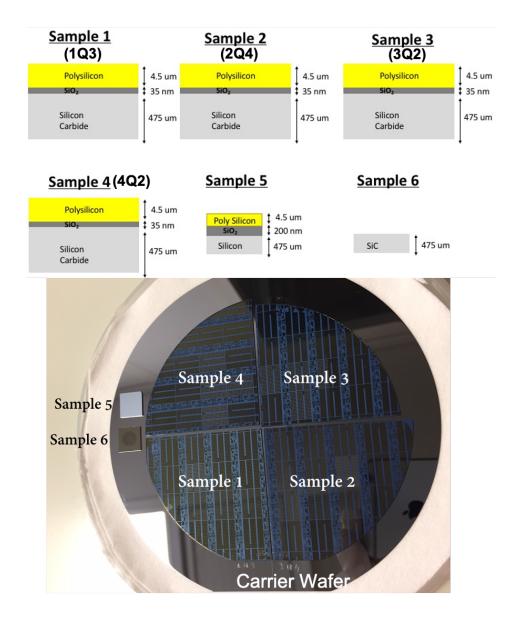

| 4.54 | Trigate Gen-1 samples loaded onto a 5 inch carrier wafer for P-base alu-<br>minum implant at Ion Beam Services                                                                                                                                                                                                                                                                                                            | 137  |

| 4.55 | Top view SEM images of polysilicon pillars before and after thermal oxidation to block the nitrogen N+ implant in the active area                                                                                                                                                                                                                                                                                         | 138  |

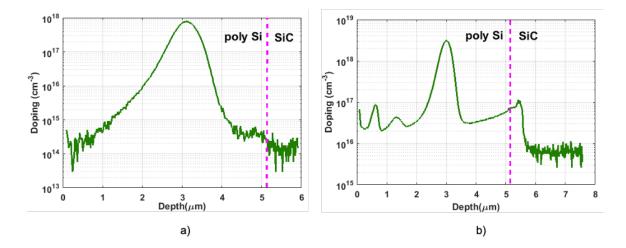

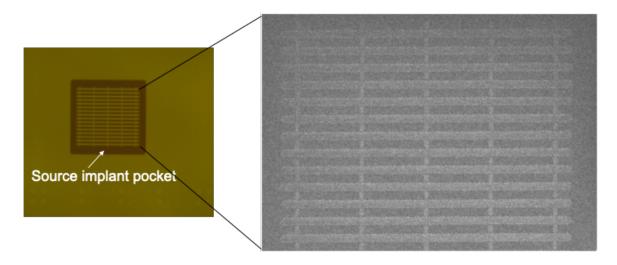

| 4.56 | SIMS analysis of high energy ion implants in SiC for the Gen-1 trigate<br>samples. a) Aluminum implant for the P-base, b) Nitrogen source implant<br>for the n-source. The SIMS measurement does not include the low energy<br>implant done at CuttingEdge Ions Inc, while the Janson model does. c)<br>Both aluminum and nitrogen implants. The shaded region is the high dose<br>base implant below the trigate trench. | 139  |

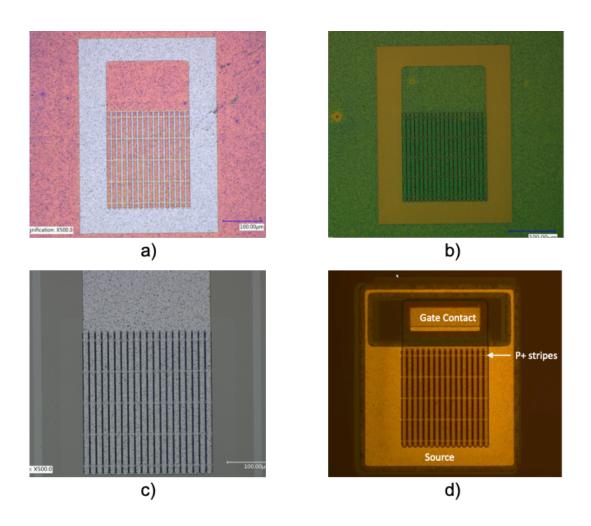

| 4.57 | Optical micrograph and SEM images of the active area after the high energy base and source implants, but before the high temperature implant anneal                                                                                                                                                                                                                                                                       | 140  |

| 4.58 | Optical micrograph images of Gen-1 trigate samples with a nickel mask prior to $P+$ implantation                                                                                                                                                                                                                                                                                                                          | 140  |

| 4.59 | Carbon cap formed on Gen-1 samples prior to implant anneal in the Epi-<br>gress hotwall CVD reactor at 1700°C for 20 minutes in an argon ambient.                                                                                                                                                                                                                                                                         | 142  |

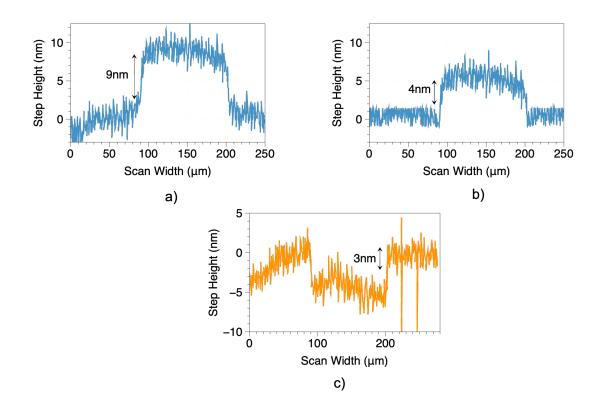

| 4.60 | Step height of implanted regions after high energy implants using a stylus profilometer a) Scan across the source implant before anneal, b) Scan across the source implant after anneal, c) Scan across the base implant before anneal                                                                                                                                                                                    | 143  |

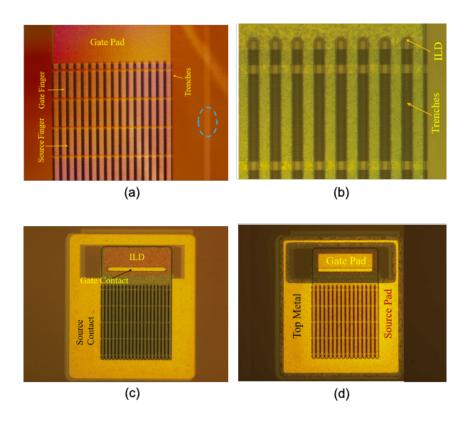

| 4.61 | Optical images of the Gen-1 trigate sample after a) Polysilicon gate doping<br>and etch b) ILD pyrogenic oxidation at 1100°C for 4 hours and 20 minutes.<br>c) Ohmic anneal at 1000°C for 3 minutes in argon d) Top metal deposition<br>(Ti/Au)                                                                                                                                                                           | 145  |

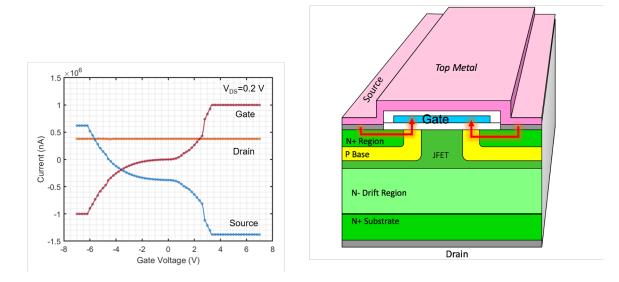

| 4.62 | Measured current at the source, drain and gate terminals plotted as a func-<br>tion of gate voltage. High gate leakage current is observed that indicates<br>failed MOSFET devices                                                                                                                                                                                                                                        | 146  |

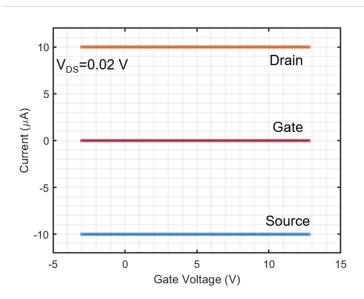

| 4.63 | Source and drain current as a function of gate voltage for a trigate MOS-<br>FET on sample 2Q4.                                                                                                                                                                                                                                                                                                                           | 147  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

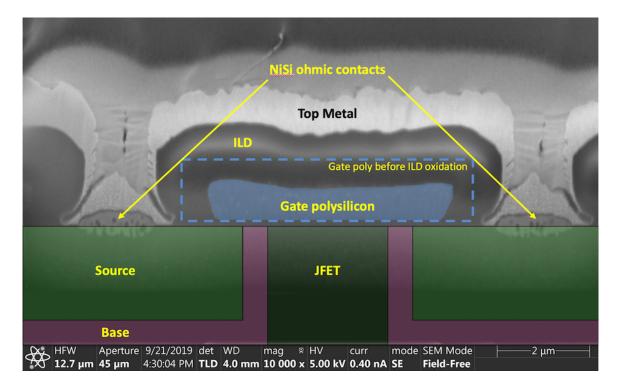

| 4.64 | SEM of a FIB cross-section of a planar Gen-1 MOSFET. False color schematically illustrates the location of the source and base implants and the gate                                                                                                                                                                                                                                                                                                                 | 148  |

| 4.65 | SEM image from Figure 4.64, recolored to match cross-section through the center of the P+ base contact implant stripe $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                             | 149  |

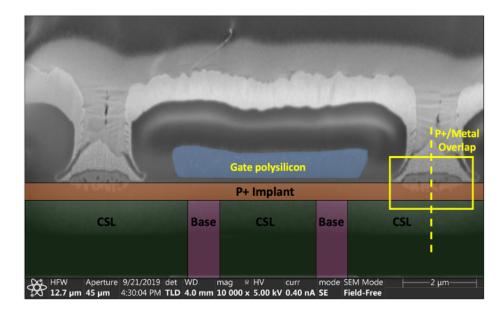

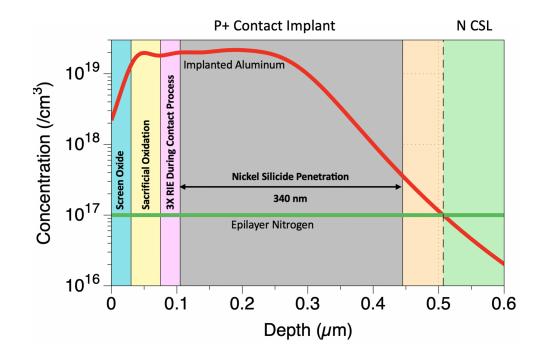

| 4.66 | P+ contact implant profile (red), and the background CSL doping (green). The PN junction occurs at the intersection, $\sim 0.5 \ \mu m$ below the original surface. The gray box indicates the measured penetration depth of the NiSi ohmic contact region.                                                                                                                                                                                                          | 150  |

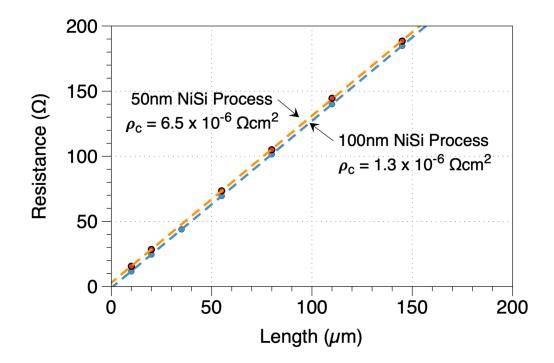

| 4.67 | TLM contact resistance measurements using the 50 nm and 100 nm nickel silicide processes.                                                                                                                                                                                                                                                                                                                                                                            | 151  |

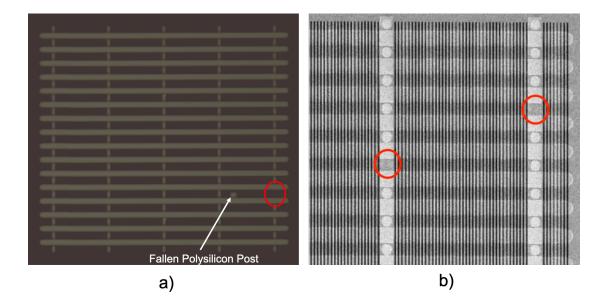

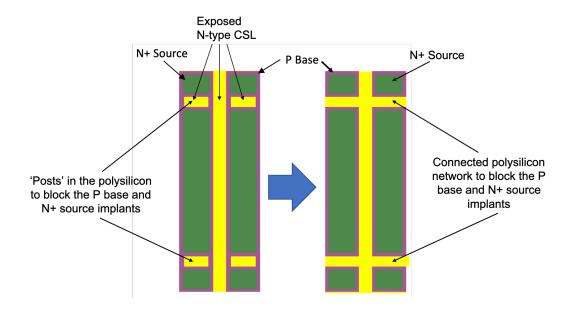

| 4.68 | Source-drain shorts caused by missing polysilicon posts after the P-type base implant and before the N+ source implant. a) Optical micrograph image showing fallen polysilicon post after the thermal oxidation process for the source implant, b) Secondary electron potential contrast SEM image of the active area of a trigate device after all implantation is complete. Light regions are P-type, gray regions are N-type, while trenches appear nearly black. | 152  |

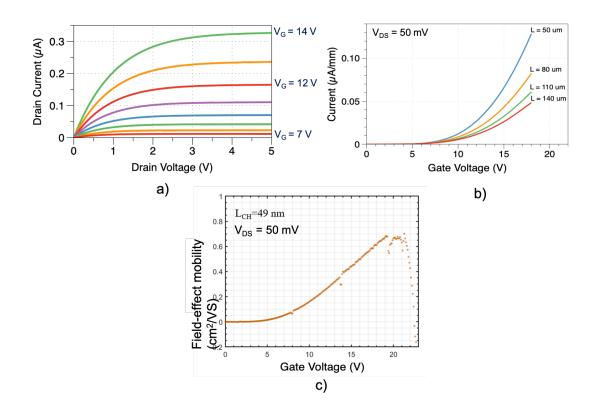

| 4.69 | Electrical measurements on lateral planar MOSFETs on sample 2Q4. (a) Drain current vs. drain voltage characteristics, (b) Drain current vs. gate voltage characteristics, (c) Field-effect mobility vs. gate voltage                                                                                                                                                                                                                                                 | 153  |

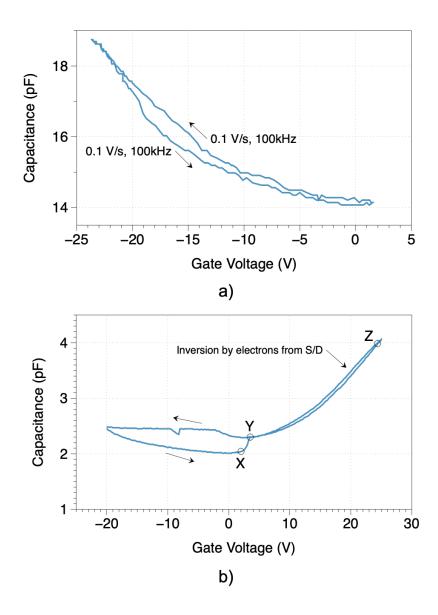

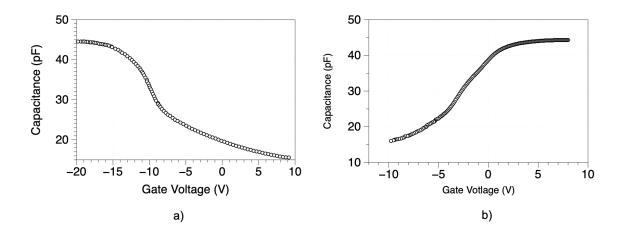

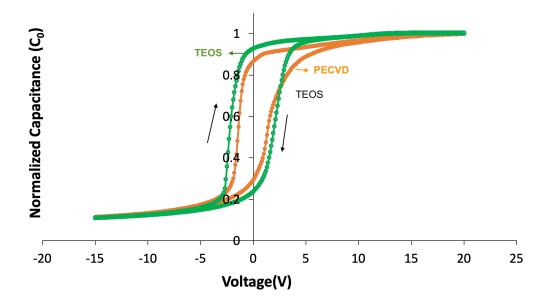

| 4.70 | C-V characteristics on sample 2Q4. (a) MOS capacitors on P-base, (b) Diode controlled MOSFET measurements on a lateral planar MOSFET at 1 kHz.                                                                                                                                                                                                                                                                                                                       | 155  |

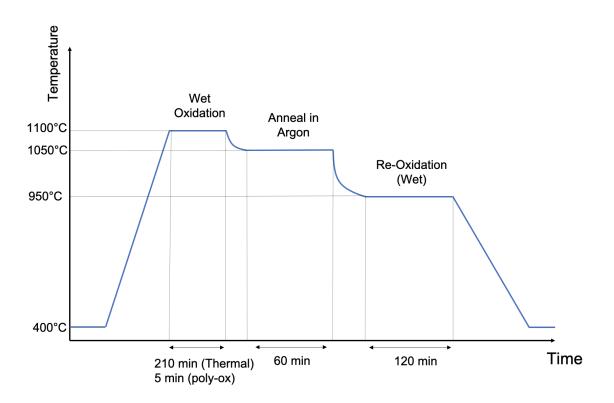

| 4.71 | Process flow for pyrogenic wet oxidation carried out for both thermal and poly-ox gate oxide processes                                                                                                                                                                                                                                                                                                                                                               | 157  |

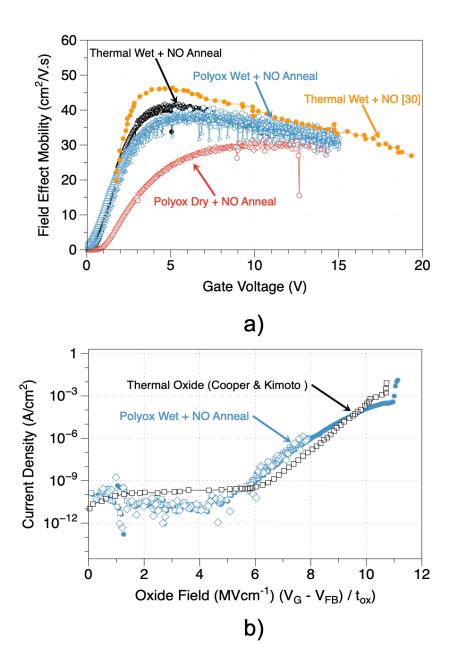

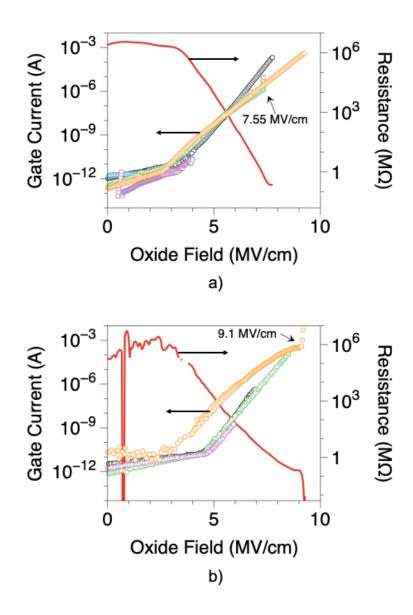

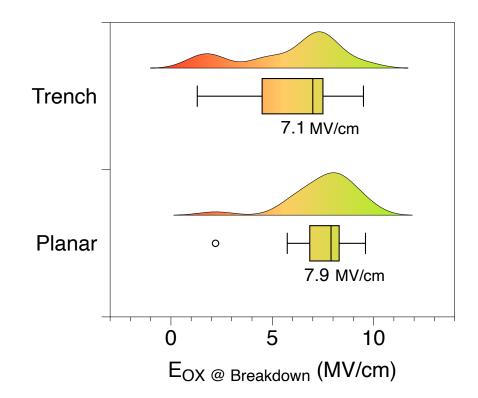

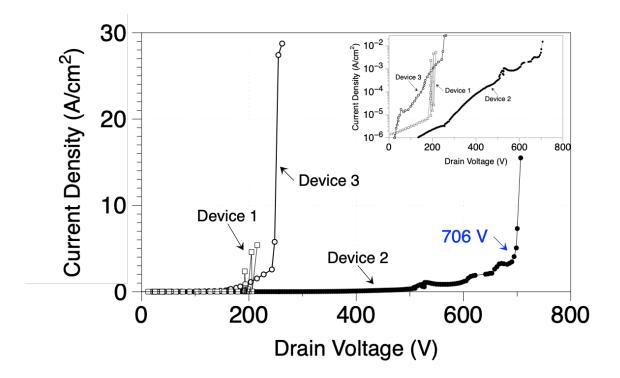

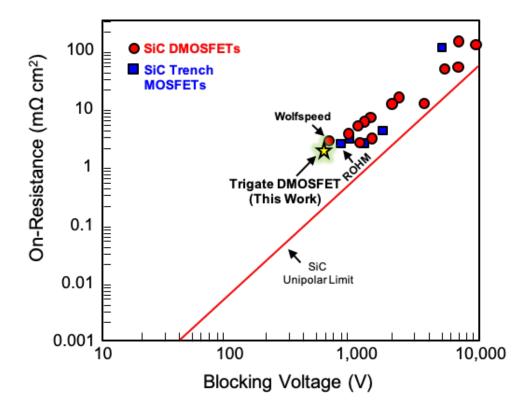

| 4.72 | Electrical measurements from polyox optimization experiment. (a) Field-<br>effect mobility of long channel lateral MOSFETs as a function of gate<br>voltage, and (b) Leakage current and breakdown as a function of oxide<br>field for the poly-ox wet oxidation process compared with thermal oxide<br>reported in literature [30]                                                                                                                                  | 158  |

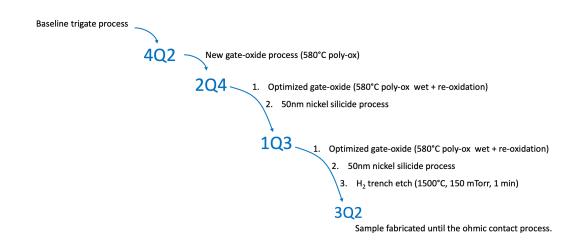

| 4.73 | Fabrication sequence and major process changes applied to Gen-1 trigate samples                                                                                                                                                                                                                                                                                                                                                                                      | 159  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                          | Page   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 4.74 | SEM images of the polysilicon mask for the base implant in Gen-2 samples.<br>(a) Mask layout of the JFET fingers; purple regions are to be implanted,<br>(b) Active area with polysilicon runners and posts, (c) Floating field ring<br>areas, (d) cross-sectional SEM of a test device processed with the trigate<br>devices, showing a good vertical, highly anisotropic polysilicon etch | 161    |

| 4.75 | Target implant schedule for Gen-2 trigate samples modelled using an an-<br>alytical implant model [98].                                                                                                                                                                                                                                                                                     | 162    |

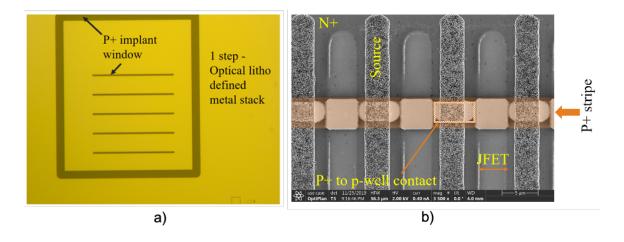

| 4.76 | SEM images of the N+ implant mask process. (a) Poly mask before oxida-<br>tion, (b) Poly oxidized by 0.5 $\mu$ m, closing the 1 $\mu$ m gap (c) Ni electroplating<br>pattern in a long channel MOSFET, (d) Closer view as indicated in (c), il-<br>lustrating step coverage of the electroplated Ni over the polysilicon topolog                                                            | gy.163 |

| 4.77 | Target N-type source implant schedule for Gen-2 trigate samples modelled using an analytical implant model [98]                                                                                                                                                                                                                                                                             | 164    |

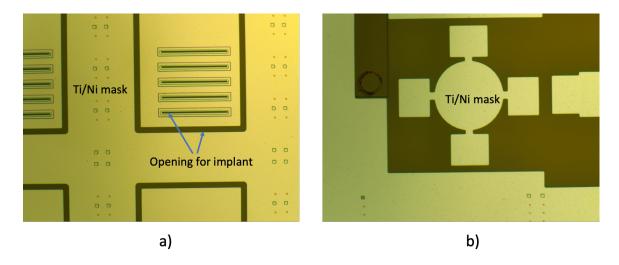

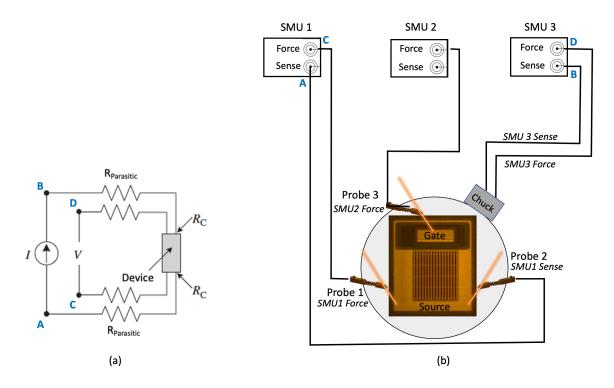

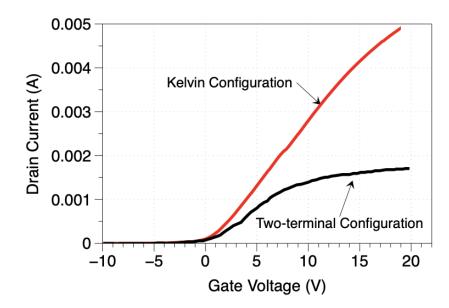

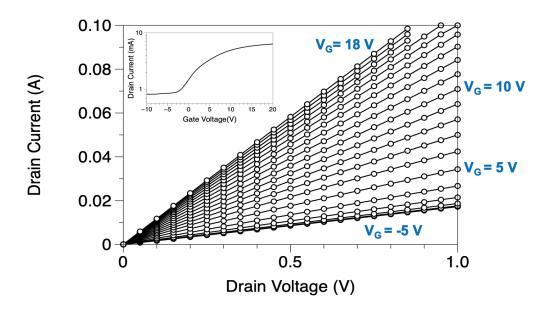

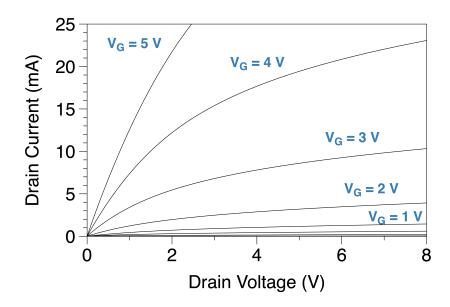

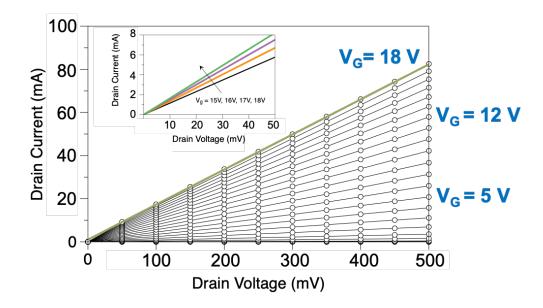

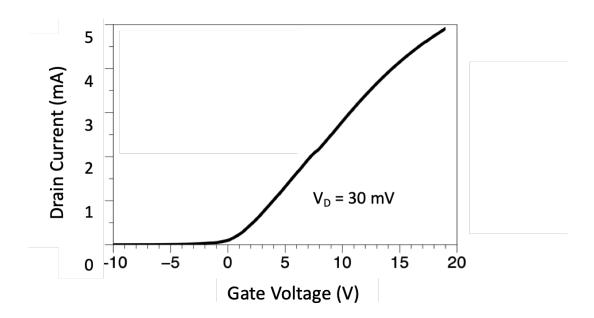

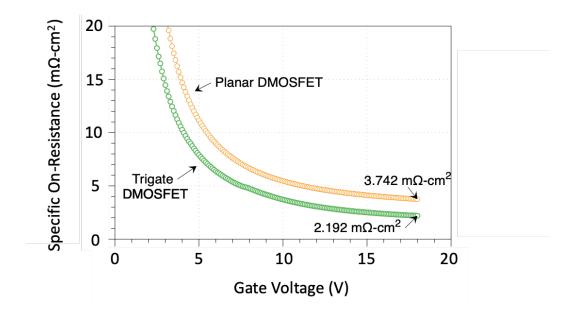

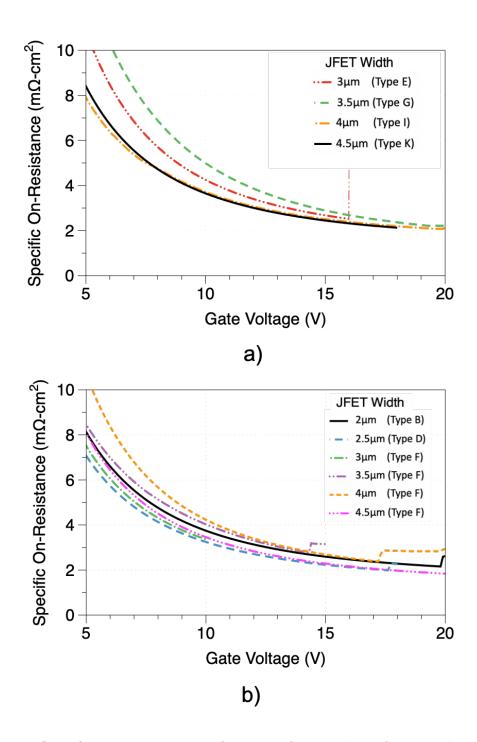

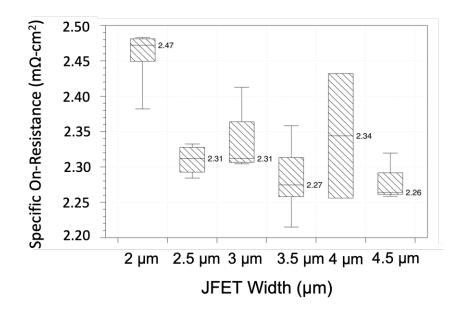

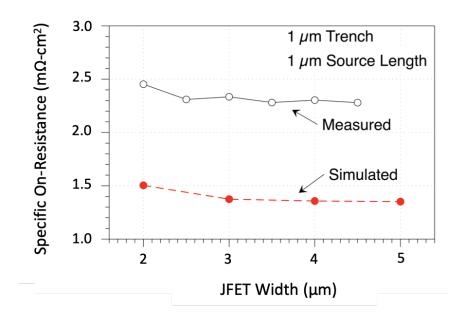

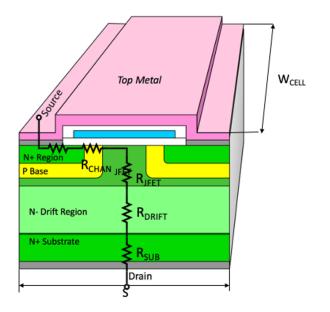

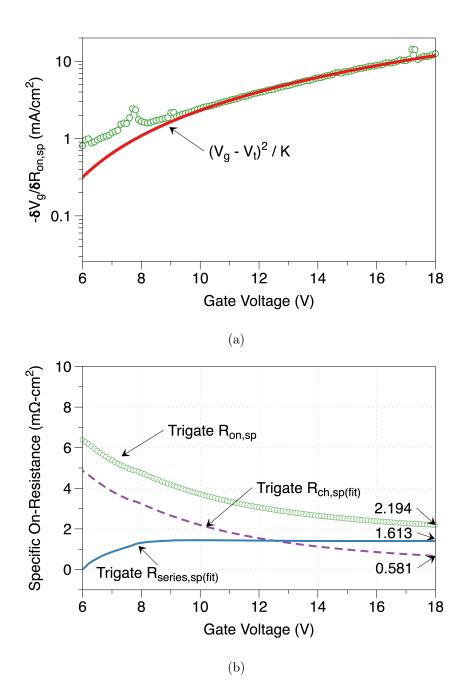

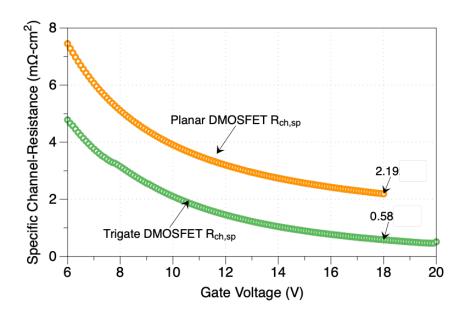

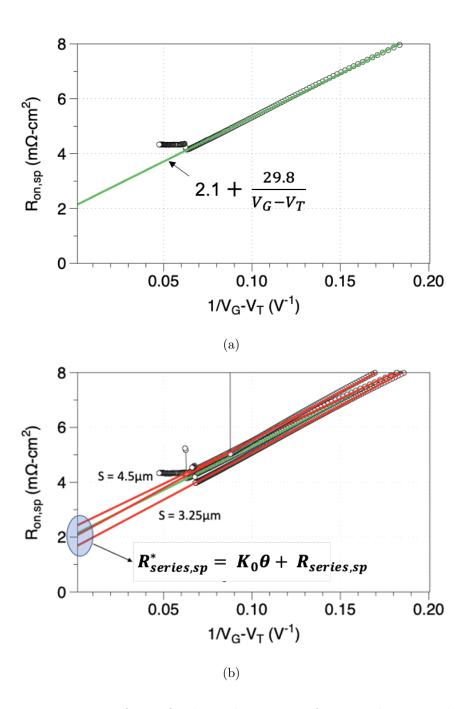

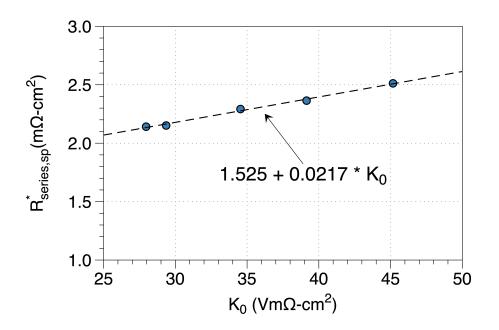

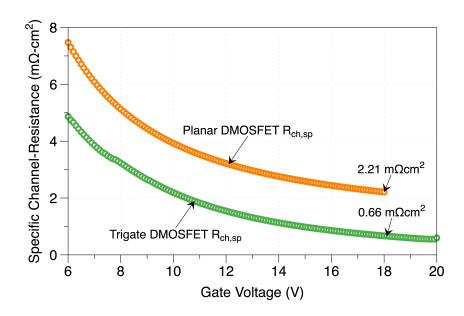

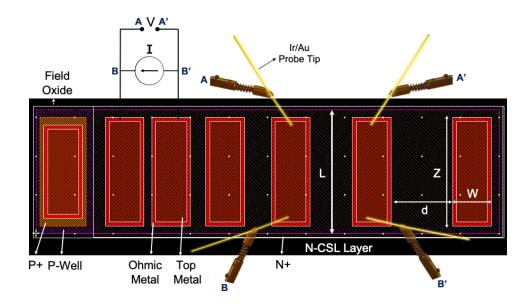

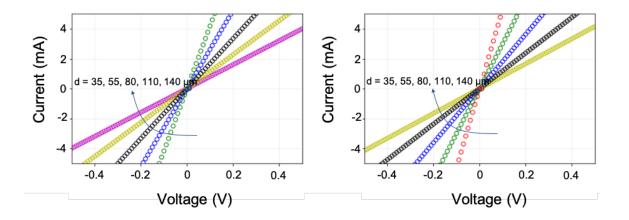

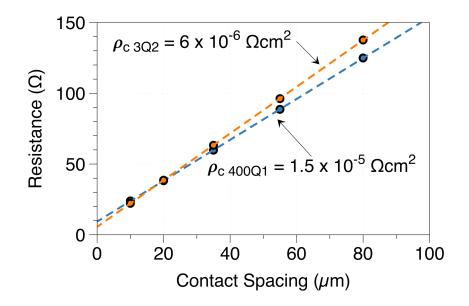

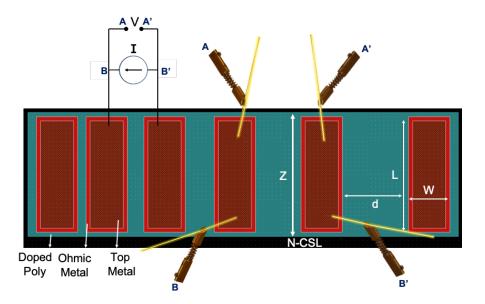

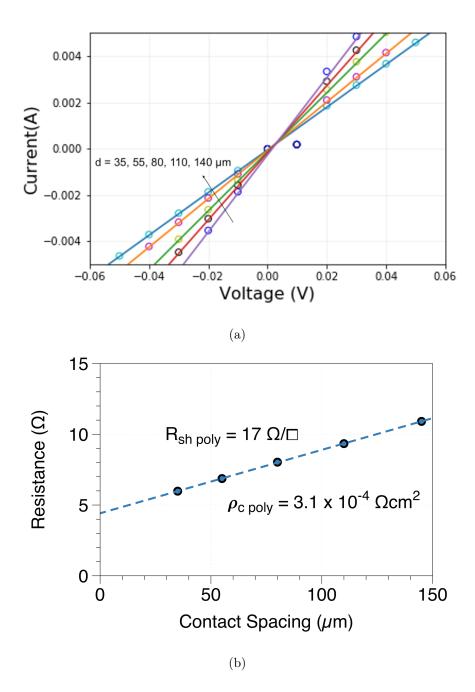

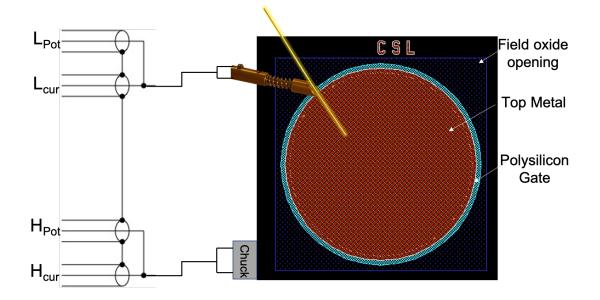

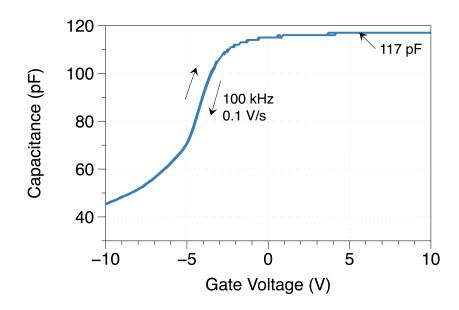

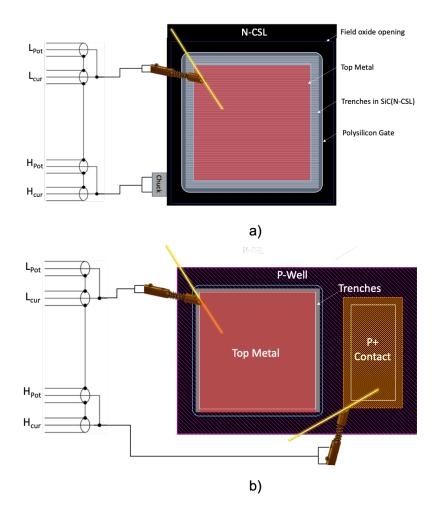

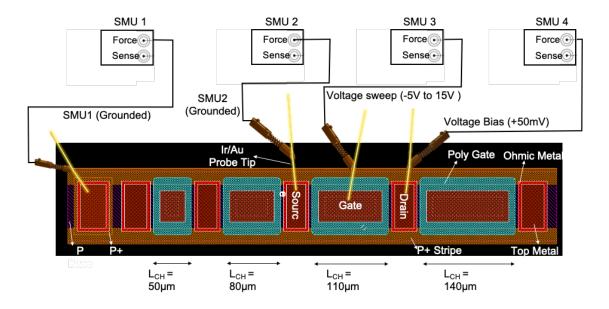

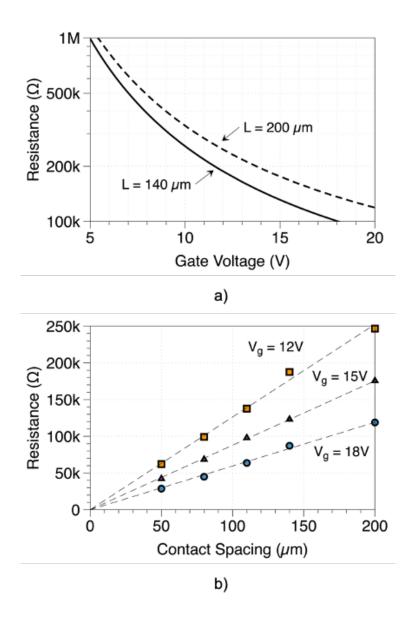

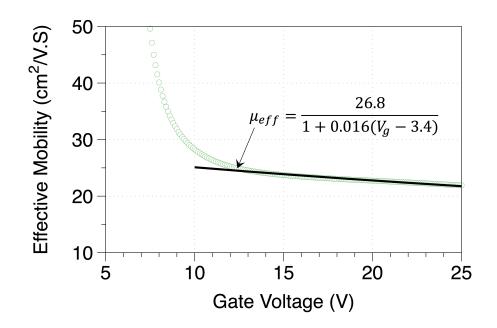

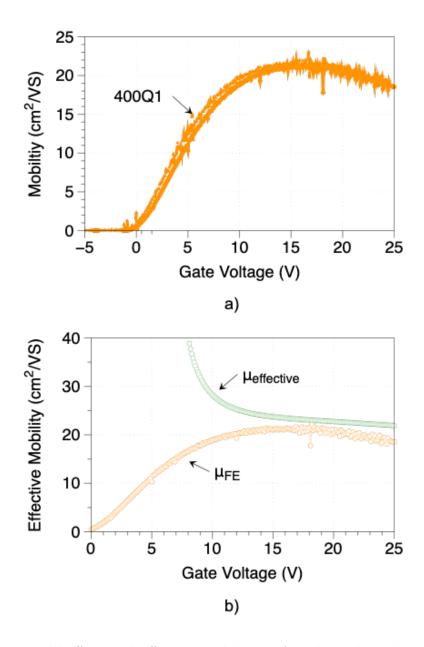

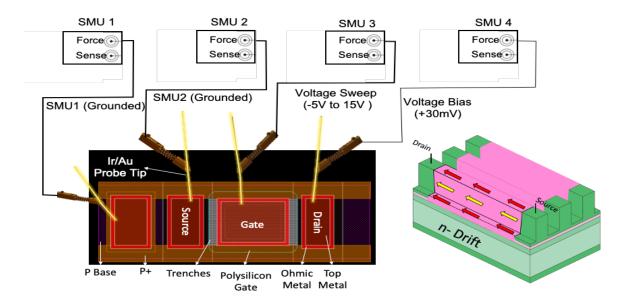

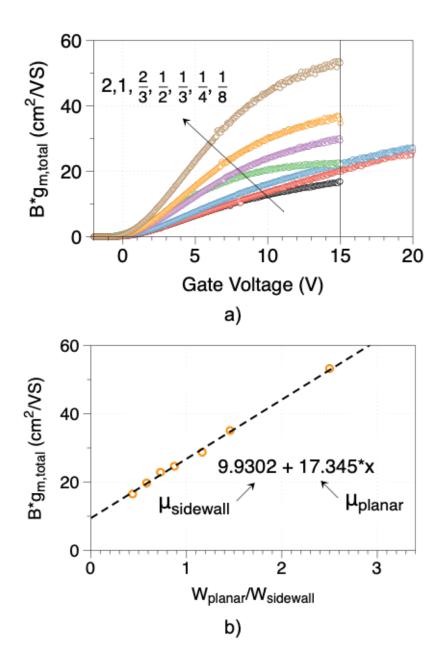

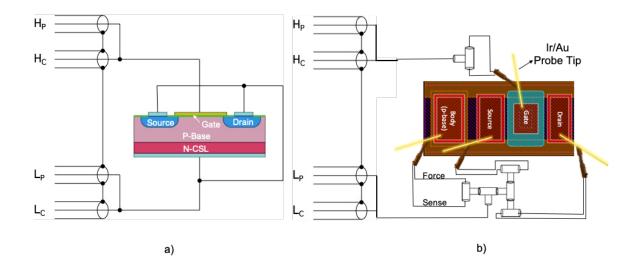

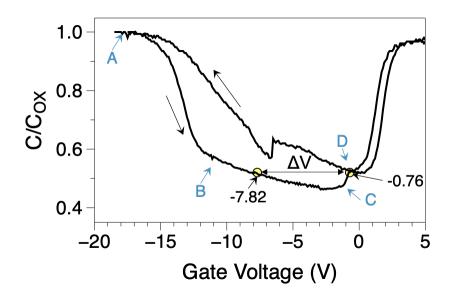

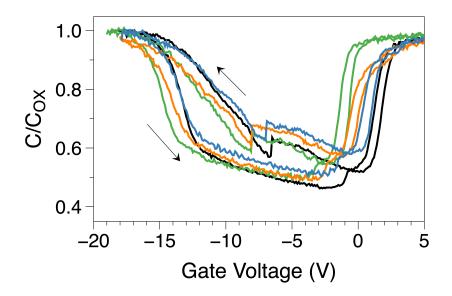

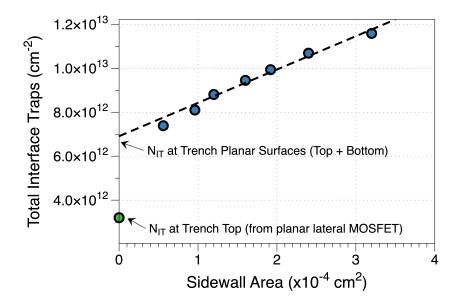

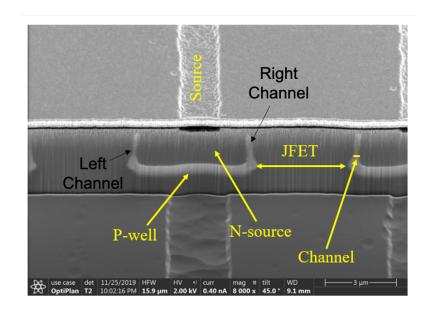

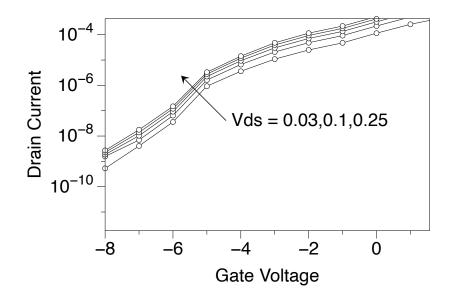

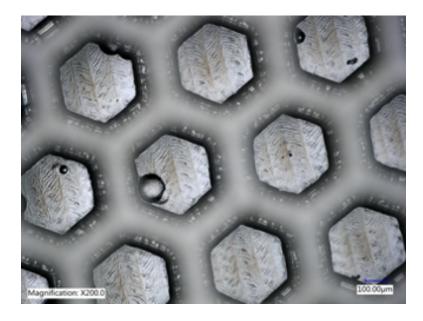

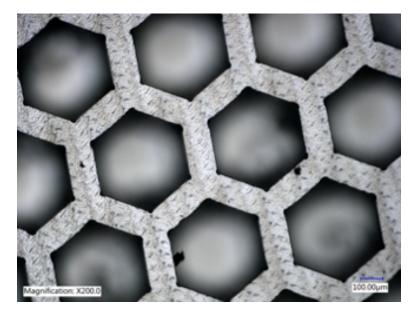

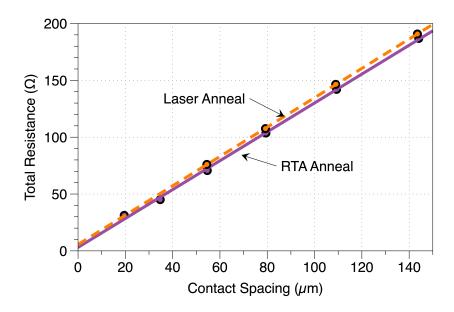

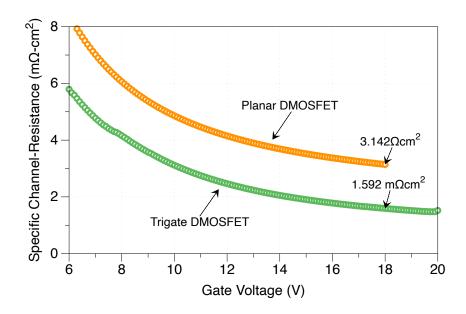

| 4.78 | P+ implantation for the Gen-2 trigate MOSFETs. (a) Metal mask defined<br>by a one step optical lithography process, (b) SEM image of the active area<br>after the $P+$ implantation                                                                                                                                                                                                         | 165    |