## 4H-SIC VERTICAL TRI-GATE POWER MOSFETS TECHNOLOGY DEVELOPMENT

by

S M Naeemul Islam

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

Electrical and Computer Engineering West Lafayette, Indiana December 2020

## THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

Dr. Dallas T. Morisette, Chair

School of Electrical and Computer Engineering

Dr. James A. Cooper

School of Electrical and Computer Engineering

### Dr. Michael J. Manfra

School of Physics and Astronomy, School of Electrical and Computer Engineering and School of Materials Engineering

### Dr. Zhihong Chen

School of Electrical and Computer Engineering

### Approved by:

Dr. Dimitrios Peroulis

To The Almighty God

### ACKNOWLEDGMENTS

As I am writing this section, I already have left Purdue for my next endeavor building a career with Wolfspeed. But it still makes me hard to believe that after seven long years at Purdue now I am here finishing one of the important and eventful chapters of my life. During this time, I consider myself very lucky and privileged to work with many amazing people on the planet, and here I can only express a small part of my gratitude for their support during my Ph.D.

First and foremost, I would like to thank my advisor Professor Dallas Morisette for all the training and support he provided me during my doctoral research and study. When I joined his group in 2015, I was inexperienced, and I knew very little in the power semiconductor device as well as wide bandgap material engineering. Professor Dallas with his immense patience and in-depth knowledge helped me to understand many aspects of the field starting from the underlying physics to the device level characterization. Often owing to my naivety, if I had difficulty understanding any concept, he took his time to explain it repetitively from various perspectives until I fully comprehended. This motivated once being a shy and quite international graduate student to speak more loudly and ask more questions. Such a way professor Dallas created an excellent environment within his group where we could share any device or design ideas with him and to the group with an open mind. Even after that, if we hesitated to express ourselves thinking the idea could be "dumb", I recall him always started answering with - "there is no such thing (dumb idea or question) exist" which made one less word in our dictionary. I am thankful to him to help build confidence in myself and his willingness to give me independence in my research work and trusting me to work with very sensitive and expensive lab tools in the cleanroom. In addition, he always encouraged me to pursue whatever I needed to expedite be it chemical or toany chemical needed for device fabrication or equipment needed for characterization which helped to steer the research problem to a simpler solution and expedited my study. Besides research and study, I had very enjoyable conversations with him about almost everything - discussing life, sports, taking tips as a parent, travel plan, etc. I am also very grateful and indebted to him for his help both administratively and morally when I faced unavoidable immigration-related complexities. I am greatly honored to work under such a gifted professor and humble person.

Next, I would like to thank Professor James Cooper for the guidance he has given me during my Ph.D. It is my great pleasure and honor to work under a professor of his stature. I have greatly benefited and enjoyed learning from every discussion I had with him. To his wisdom, Professor Cooper always knew at what level the experiment could be pushed while it was running well and when to be patient and what could be tried when the experiments were not going well. His invaluable guidance, patience, and enthusiasm always fostered a positive vibe within the group. I would like to thank my doctoral committee member -Professor Michael Manfra. I am immensely grateful to him to allow me to work in very sensitive low-temperature cryostat characterization equipment and introduced me to the device fabrication in the cleanroom.

I would like to thank Professor Zhihong Chen for being one of the members of my doctoral committee. It has been my great pleasure and honor to have her expert opinion and feedback on this work.

Next, I would like to thank my group members and fellow post-docs without whom I could not reach to this point. First, I would like to thank Rahul who was my all-time partner to this journey. His innovative ideas, fabrication expertise, and depth in understanding the physics always benefited me. During the slow pace in device fabrication development, I always found him patient on me and shared his hand when needed. His patience and calmness in any difficult situation always amazed me. I am thankful to Monzurul, Madan, Noah, Kouhsik, Chunkun, Arash, and Varun. They were always with me when I needed them in both good and bad times. I would like to thank Monzurul for the TCAD simulation tutorial lecture and lucid explanations. I believe no one is better than him explaining things. Besides, I will greatly miss his sudden brain puzzle problem for which we had to pick our pen and paper to make boolean tables thinking all the combinations to solve it. I would like to thank Madan who helped me understanding various TCAD related study and his expert hand for taking FIB images what would have taken ages for me. I would like to thank Noah whom I always found in the cleanroom regardless if it is beyond midnight or 8 in the morning. His energy and positive attitude towards solving problems in any sort of fabrication level were exceptional. His willingness to help and valuable advice many times helped me to try new things in a simpler way. The late-night discussion and debate with Chunkun about various topics—new novels, politics, gardening, etc. were very enjoyable. I would like to thank all of them to transform this journey towards Ph.D. enjoyable and memorable which without them would be very monotonous. I would also like to thank our newest members in the group – Swati and Rajni to bring fresh energy to the group and I wish them the best of success.

I would like to thank my former colleague while working in Professor Manfra's group – Sumit Mandal, John Watson, Saeed Fallahi, Ali Shirazi, Qi Qian, Mike Yannell, James Nakamura, Tiantian Wang, and Geoff Gardner. They all have been my greatest support and helped me to build my knowledge in device characterization and fabrication.

I would like to thank all of the scientists, engineer, and staff in the Birck nanofabrication facility, Prof. Yi Xuan, Bill Rowe, Justin Wirth, Tim Miller, Dave Lubelski, Kenny Schwartz, Jeremiah Shepard, Dan Hosler, Richard Hosler, Michael Bayless, Francis Manfred, Stephen Jurss, Tim Miller, Joon Park, Ron Reger, Nancy Black, Kyle Corwin, Mary Jo Totten, Brenda Meador, Rosa Diaz, Nithin Raghunathan, John Coy, whose valuable assistance made this work possible. It is my greatest grievance that Kenny had passed away after I left. He helped me in numerous ways with metal deposition, target source change, training, etc. May he rest in peace.

I would like to thank Wolfspeed, a Cree company for giving me the opportunity to work with them even when I was not officially done with my Ph.D. I would like to thank my manager Sei-Hyung Ryu and other colleagues, Dan Litchenwalner, Woongsun Kim, Charlotte Jonas, Kijeong Han, Jeff Kim, and Andreas Scholze for their support, advice, and for giving me some leeway to concentrate on my thesis writing.

I would like to thank all my friends from my compatriot community at Purdue, naming all of them will take another thesis length of writing, so I am restraining myself from that daunting task. I am thankful to the Bangladesh student's association at Purdue for giving me the opportunity to work as an executive committee member. It was a unique experience which helped me to learn organization, leadership, and being a team player. I would also like to thank all the members of the Purdue Tigers cricket team. At my leisure, I enjoyed playing with some crazy enthusiast cricketers in the world. I would also like to thank the wonderful community of the Islamic Society of Greater Lafayette (ISGL).

I would like to thank my parents who always encouraged me and supported me in every possible way. I certainly would not have made this far without their unselfish sacrifice and unending love. I am grateful to them for giving me the freedom and helping me to decide to come to other ends of the world at Purdue to pursue my Ph.D. I would like to thank my siblings and siblings-in-law who supported me immensely in this journey.

I would like to thank my coolness of eyes – our 3-year-old son Yusuf. The immense joy and comfort of heart seeing him growing up in each day is mountain-greater than any grim I faced ever. You are my best-blessed gift and thanks to smiling at me always even when I was guilty not to hold your hand during our playtime instead spent time coaxing with etching or lithography.

Finally, last but not the least, I would like to thank my loving wife Nayima. I have been her greatest fan. Without her encouragement, patience, and love, I would not be able to run this dream. Her exceptional patience in tolerating all the nights and weekends I have spent in the lab and cleanroom trying to make progress in experiments incredibly encouraged me to move forward. She is my greatest source of support. I take my hats off and give all the kudos to her who single-handedly managed our son. I will always be indebted to her devotion and sacrifice.

## TABLE OF CONTENTS

| LIS | ST O | F TAB   | LES       |                                               | . 12 |

|-----|------|---------|-----------|-----------------------------------------------|------|

| LIS | ST O | F FIGU  | URES      |                                               | . 13 |

| AE  | BSTR | ACT     |           |                                               | . 20 |

| 1   | INT  | RODUC   | CTION .   |                                               | . 21 |

|     | 1.1  | Power   | Semicono  | ductor Devices                                | . 21 |

|     | 1.2  | Silicon | Carbide   |                                               | . 22 |

|     |      | 1.2.1   | Critical  | Electric Field                                | . 24 |

|     |      | 1.2.2   | High Te   | emperature Operation and Thermal Conductivity | . 29 |

| 2   | A N  | OVEL .  | APPROA    | CH TO SIC POWER SWITCHING DEVICES - THE TRI-  |      |

|     | GAT  | 'E MOS  | SFET      |                                               | . 31 |

|     | 2.1  | Silicon | Carbide   | MOSFET Applications                           | . 31 |

|     | 2.2  | SiC M   | OSFET S   | Status and Prospects                          | . 33 |

|     |      | 2.2.1   | Dielectri | ic Interface                                  | . 33 |

|     |      | 2.2.2   | Design I  | Innovation                                    | . 36 |

|     |      |         | 2.2.2.1   | Source Contact Resistance                     | . 39 |

|     |      |         | 2.2.2.2   | Source Resistance                             | . 39 |

|     |      |         | 2.2.2.3   | Channel Resistance                            | . 40 |

|     |      |         | 2.2.2.4   | JFET Resistance                               | . 42 |

|     |      |         | 2.2.2.5   | Drift Resistance                              | . 44 |

|   |     |         | 2.2.2.6 Substrate Resistance                         | 47 |

|---|-----|---------|------------------------------------------------------|----|

|   | 2.3 | Propos  | sed Tri-gate SiC MOSFET                              | 49 |

| 3 | DEV | VICE DI | ESIGN AND MASK LAYOUT                                | 55 |

|   | 3.1 | Device  | e Design - JFET Length                               | 59 |

|   | 3.2 | Device  | e Design - Contact Length                            | 60 |

|   | 3.3 | Device  | e Design - Floated Field Ring (FFR) Edge Termination | 61 |

|   | 3.4 | Mask 1  | Layout                                               | 66 |

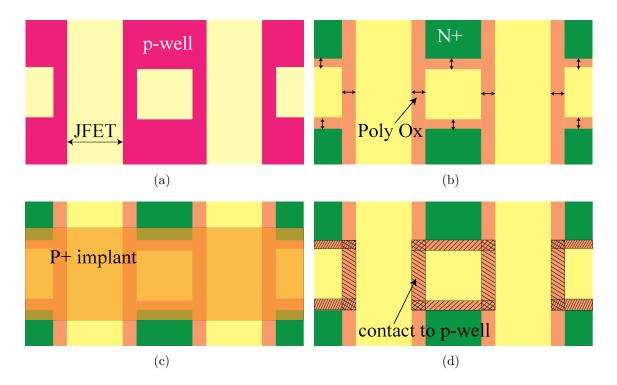

|   |     | 3.4.1   | P-well Implant - Optical Lithography                 | 67 |

|   |     | 3.4.2   | P-well Implant - E-beam Lithography                  | 67 |

|   |     | 3.4.3   | Alternate P-well Implant Single Step Mask            | 70 |

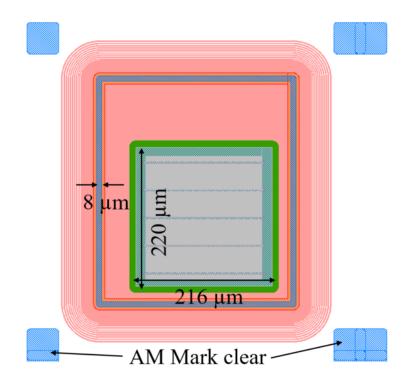

|   |     | 3.4.4   | Alignment Mark                                       | 70 |

|   |     | 3.4.5   | N+ Source Implant - Optical Lithography              | 73 |

|   |     | 3.4.6   | P <sup>+</sup> Implant - E-beam Lithography          | 74 |

|   |     | 3.4.7   | P <sup>+</sup> Implant - Optical Lithography         | 76 |

|   |     | 3.4.8   | Alternate P+ Implant - One-step Lithography Process  | 77 |

|   |     | 3.4.9   | Trench - E-beam Lithography                          | 78 |

|   |     | 3.4.10  | Trench - Optical Lithography                         | 79 |

|   |     | 3.4.11  | Field Oxide - Optical Lithography                    | 81 |

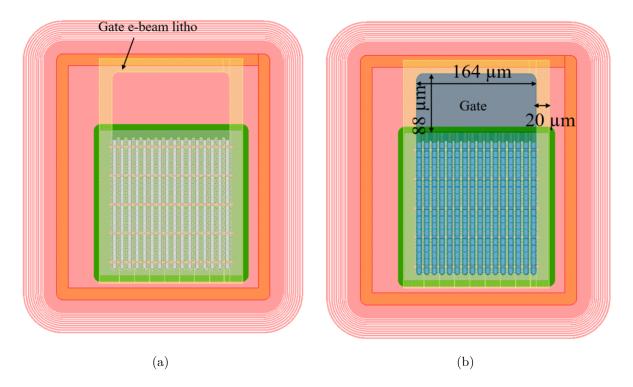

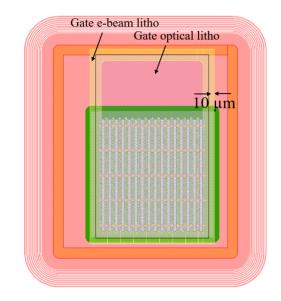

|   |     | 3.4.12  | Gate - E-beam Lithography                            | 82 |

|   |     | 3.4.13  | Gate - Optical Lithography                           | 83 |

|   |      | 3.4.14 Ohmic - Optical Lithography                   | 84  |

|---|------|------------------------------------------------------|-----|

|   |      | 3.4.15 ILD Etch - Optical Lithography                | 86  |

|   |      | 3.4.16 Top Metal - Optical Lithography               | 87  |

| 4 | TRI- | GATE PROCESS TECHNOLOGY                              | 88  |

|   | 4.1  | Implantation – P-well                                | 89  |

|   | 4.2  | Implantation – Source                                | 100 |

|   | 4.3  | Current Spreading Layer (CSL)                        | 108 |

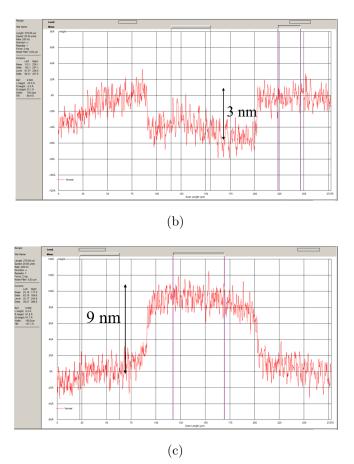

|   | 4.4  | Implant Swelling                                     | 112 |

|   | 4.5  | Implantation – P <sup>+</sup> Well Contact           | 114 |

|   | 4.6  | Trench                                               | 125 |

|   | 4.7  | Field Oxide                                          | 140 |

|   | 4.8  | Gate Oxide                                           | 147 |

|   | 4.9  | Polysilicon Gate                                     | 151 |

|   | 4.10 | Interlayer Dielectric - the Growth                   | 164 |

|   | 4.11 | Ohmic Contacts                                       | 165 |

|   | 4.12 | Interlayer dielectric - Patterning and Etching       | 170 |

|   | 4.13 | Top Metal                                            | 172 |

| 5 | DEV  | ICE MEASUREMENTS AND PROCESS MODIFICATIONS           | 175 |

|   | 5.1  | First Completed Run of Tri-gate Devices (Sample 4Q2) | 175 |

|   | 5.2  | Polysilicon Gate Oxide Optimization                  | 180 |

|    | 5.3  | Polysil  | icon Implant Mask Modification                   | 187 |

|----|------|----------|--------------------------------------------------|-----|

|    | 5.4  | Second   | l Completed Run of Tri-gate Devices (Sample 2Q4) | 191 |

|    |      | 5.4.1    | Surface Charge Inversion                         | 192 |

|    |      | 5.4.2    | Polysilicon Post Damage                          | 193 |

|    |      | 5.4.3    | Implant Tilt Angle Uncertainties                 | 194 |

|    |      | 5.4.4    | Ohmic Process and Anneal                         | 201 |

|    | 5.5  | Latera   | l MOSFET Measurement and Mobility Issue          | 205 |

|    | 5.6  | Summ     | ary                                              | 210 |

| 6  | CON  | ICLUSI   | ON AND FUTURE IMPROVEMENTS                       | 211 |

| RI | EFER | ENCES    | \$                                               | 218 |

| A  | FAB  | RICAT    | ION STEPS FOR 4Q2 AND 2Q4 GEN-1 TRI-GATE SAMPLE  | 223 |

| В  | GEN  | I-2 TRI- | -GATE IMPLANTATION DESIGN AND DEVICE LAYOUT      | 246 |

| С  | NICI | KEL EI   | ECTROPLATING                                     | 250 |

| VI | TA   |          |                                                  | 253 |

## LIST OF TABLES

| Tabl | le                                                                                                                                                                            | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

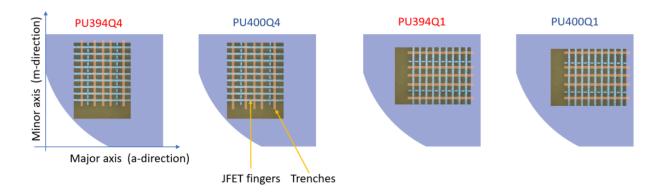

| 3.1  | Device variation in Gen-1 tri-gate mask layout.                                                                                                                               | 58   |

| 4.1  | Tri-gate Gen-1 sample information                                                                                                                                             | 89   |

| 4.2  | Gen-1 tri-gate – p-well aluminum implant profile                                                                                                                              | 91   |

| 4.3  | Polysilicon etch recipe in the STS ASE ICP-RIE etcher                                                                                                                         | 92   |

| 4.4  | Gen-1 tri-gate – n-source nitrogen implant profile                                                                                                                            | 102  |

| 4.5  | SiC etch recipe in E-620 Panasonic                                                                                                                                            | 112  |

| 4.6  | Gen-1 tri-gate – $p^+$ implant profile $\ldots \ldots \ldots$ | 115  |

| 4.7  | SiC etch recipe in an STS-AOE ICP-RIE                                                                                                                                         | 131  |

| 4.8  | SiC etch recipe in an Oxford Plasmapro 100 ICP-RIE                                                                                                                            | 136  |

| 4.9  | Tri-gate Gen-1 sample trench depth                                                                                                                                            | 138  |

| 4.10 | $\mathrm{SiO}_2$ etch recipe in E620 Panasonic ICP-RIE                                                                                                                        | 142  |

| 4.11 | Jupiter RIE etch recipe                                                                                                                                                       | 155  |

| 4.12 | Top metal deposition condition                                                                                                                                                | 172  |

| 5.1  | Gen-1 Tri-gate Samples                                                                                                                                                        | 175  |

| 5.2  | Polysilicon gate oxide optimization sample lot 1                                                                                                                              | 181  |

| 5.3  | Polysilicon gate oxide optimization sample lot 2                                                                                                                              | 182  |

| 5.4  | Effective oxide thickness extracted from the MOSCAP measurments shown in Fig. 5.7                                                                                             | 184  |

| B.1  | Gen-2 tri-gate – p-well aluminum implant profile                                                                                                                              | 247  |

| B.2  | Gen-2 tri-gate – n-source aluminum implant profile                                                                                                                            | 248  |

| B.3  | Gen-2 tri-gate device combination                                                                                                                                             | 249  |

| B.4  | Gen-2 FFR design with 5% expansion ratio on space and width $\ldots \ldots \ldots$                                                                                            | 249  |

| B.5  | Gen-2 tri-gate device FFR map                                                                                                                                                 | 249  |

## LIST OF FIGURES

| Figure |                                                                                                                                                              | Page        |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.1    | Hexagonal unit cell in 4H-SiC with important faces highlighted. Typical SiC wafer orientation is also shown                                                  | 23          |

| 1.2    | Impact ionization at a high electric field showing an energetic electron creating a electron-hole pair                                                       | 24          |

| 1.3    | Comparison of the impact ionization coefficients for SiC and Si as a function of inverse electric field, based on equations 1.5 - 1.8                        | 26          |

| 1.4    | Critical electric field of SiC and Si as a function of doping                                                                                                | 27          |

| 1.5    | Abrupt P <sup>+</sup> -N diode and the electric field profile at blocking voltage in non punch through case                                                  | 28          |

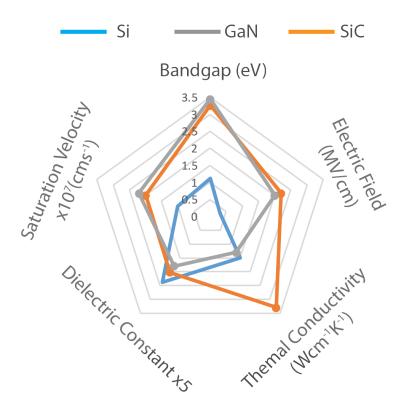

| 1.6    | Radar graph of selected material parameters of Si, SiC and GaN                                                                                               | 30          |

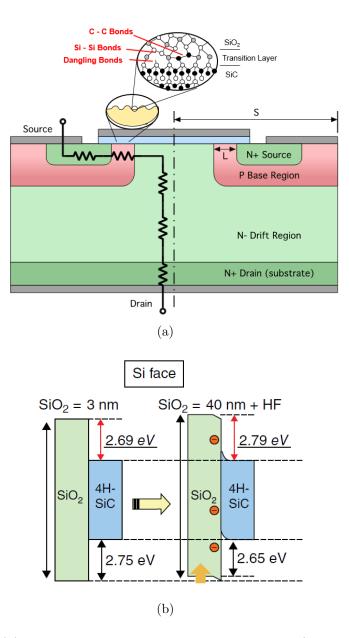

| 2.1    | (a) Dangling bonds and abruptness at $SiC/SiO_2$ interface and (b) The low conduction band offset between SiC and $SiO_2$ leads to Fowler-Nordheim tunneling | 35          |

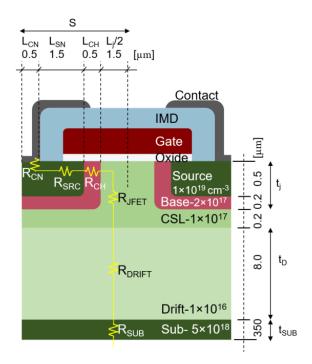

| 2.3    | Resistance components of DMOSFET device                                                                                                                      | 38          |

| 2.4    | (a) Simple one sided p-n junction, (b) Electric field profile in the non-punch-<br>through case                                                              | 44          |

| 2.5    | Electric field profile under punch-through at lower doping concentrations                                                                                    | 45          |

| 2.6    | Blocking voltage as a function of drift layer doping concentration and thickness                                                                             | <b>s</b> 46 |

| 2.7    | Specific on-resistance as a function of blocking voltage for different device designs in SiC and Si [4], [26]                                                | 48          |

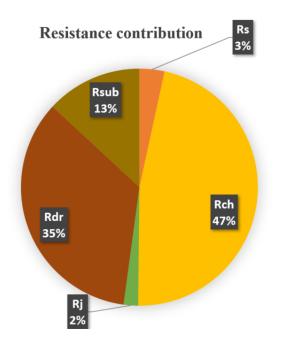

| 2.8    | Resistance contribution of 900 V DMOSFET device                                                                                                              | 49          |

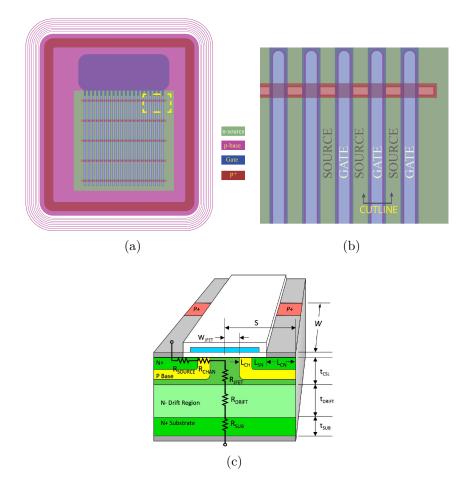

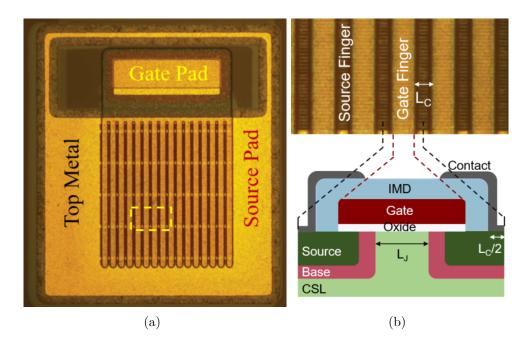

| 2.9    | DMOSFET design structure (a) Complete device, (b) Close-up view, and (c) An isometric view from the cut-line of (b)                                          | 51          |

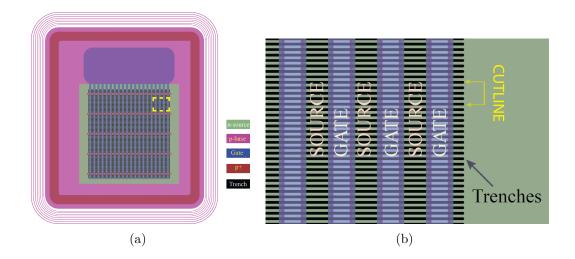

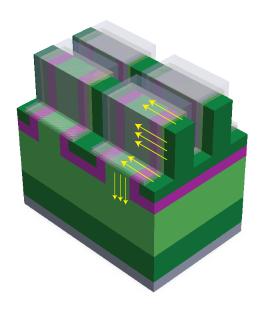

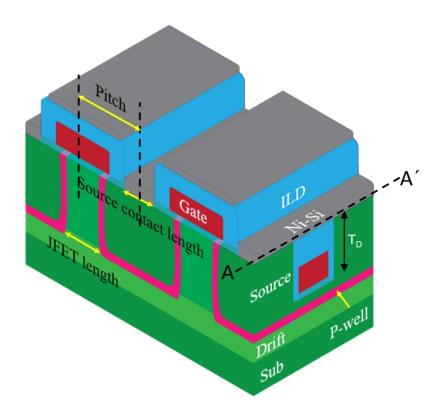

| 2.10   | Tri-gate MOSFET design structure (a) Complete device, (b)Closer view of a and (c)An isometric view from the cut-line of (b)                                  | 52          |

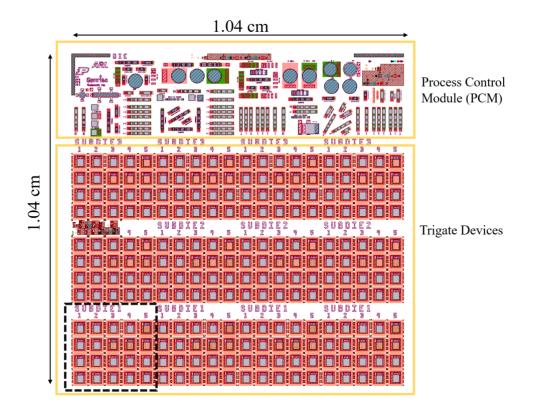

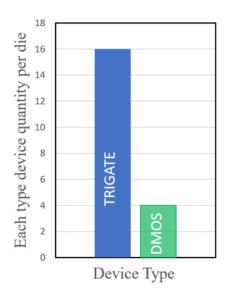

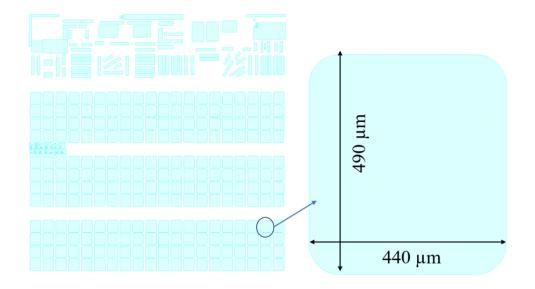

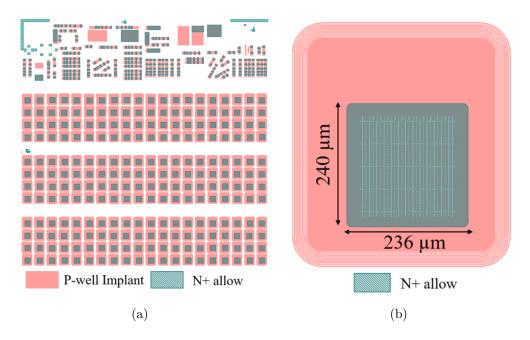

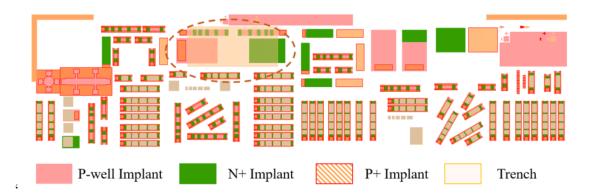

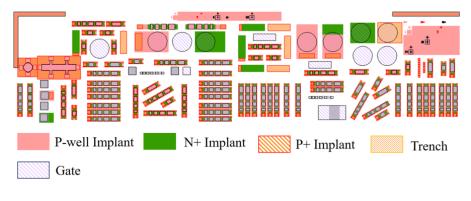

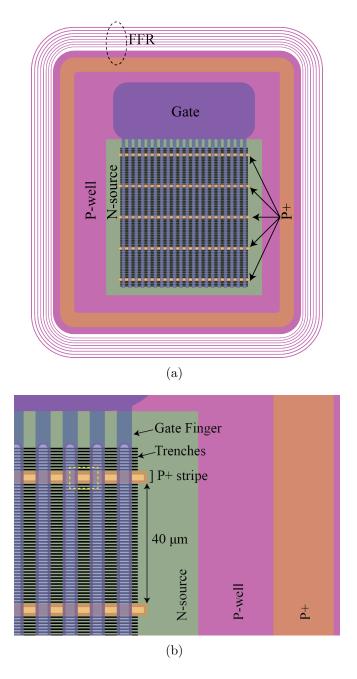

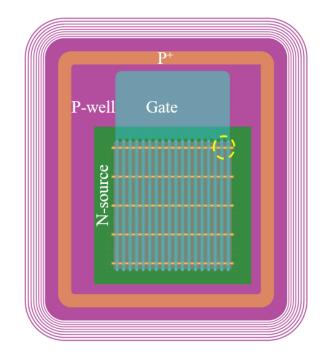

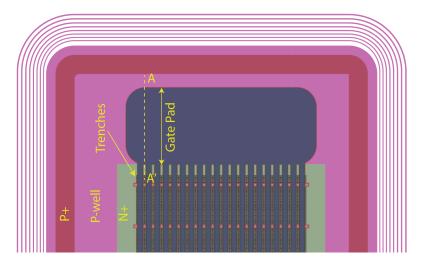

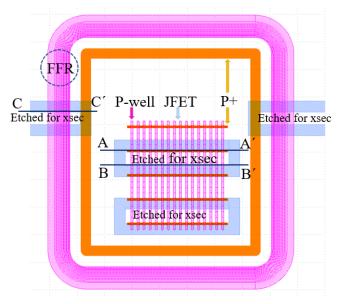

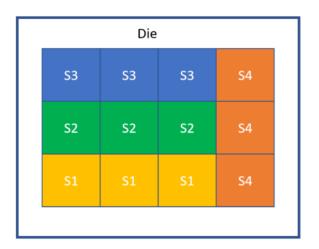

| 3.1    | Trigate mask layout die.                                                                                                                                     | 55          |

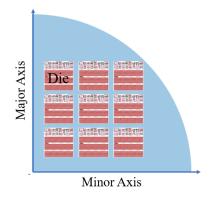

| 3.2    | Tri-gate device die in the quarter wafer SiC sample                                                                                                          | 56          |

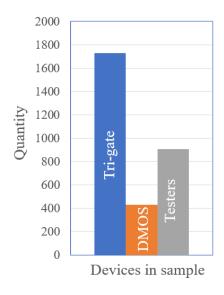

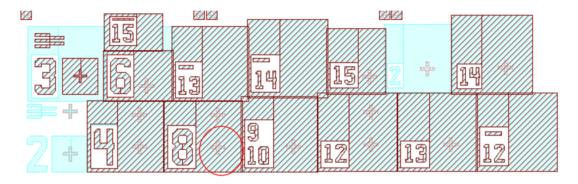

| 3.3    | Device distribution in a Tri-gate sample                                                                                                                     | 56          |

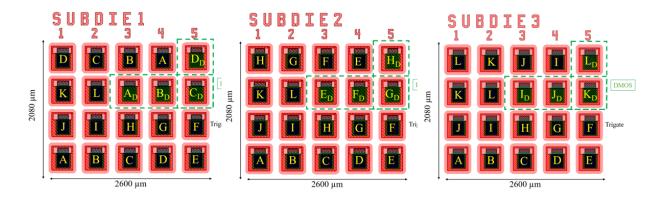

| 3.4    | Tri-gate mask layout sub-die. 'D' subscript indicates the location of a DMOS-<br>FET of the specified design                                                 | 57          |

| 3.5    | Device distribution in a single die                                                                                                                          | 57          |

| Figu | re                                                                                                                           | Page |

|------|------------------------------------------------------------------------------------------------------------------------------|------|

| 3.6  | Process parameter– JFET length and contact length visualization                                                              | 58   |

| 3.7  | Tri-gate device structure.                                                                                                   | 59   |

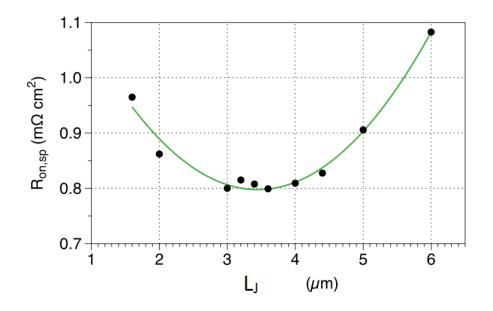

| 3.8  | Simulated specific on-resistance variation with the JFET length                                                              | 60   |

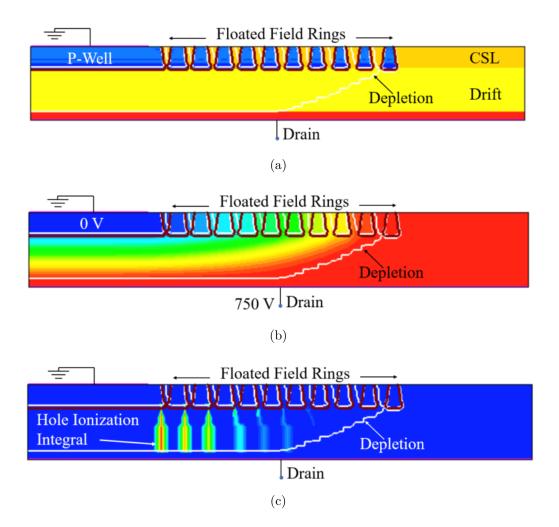

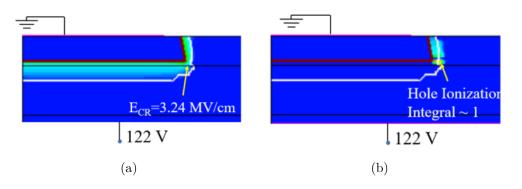

| 3.9  | Optimzed FFR edge termination design for 600 V application                                                                   | 63   |

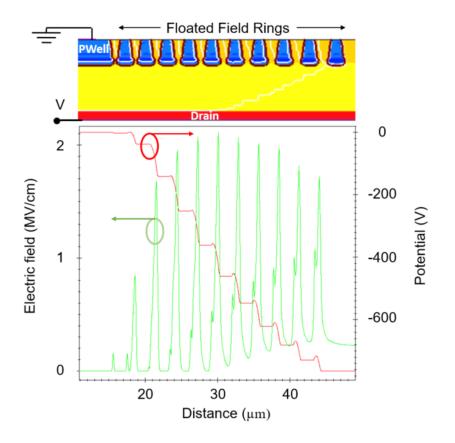

| 3.10 | The electric field and potential distribution at breakdown condition                                                         | 64   |

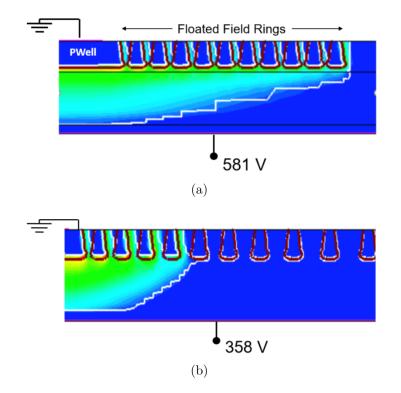

| 3.11 | Unterminated streture.                                                                                                       | 64   |

| 3.12 | Non-optimized FFR termination design.                                                                                        | 65   |

| 3.13 | P-well implant optical lithography in the die and in the tri-gate device                                                     | 67   |

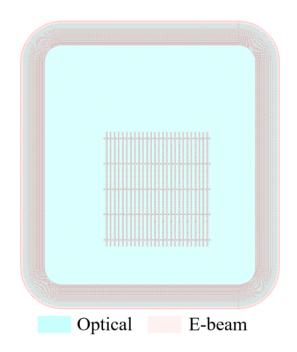

| 3.14 | Dual e-beam/optical P-well implant mask                                                                                      | 68   |

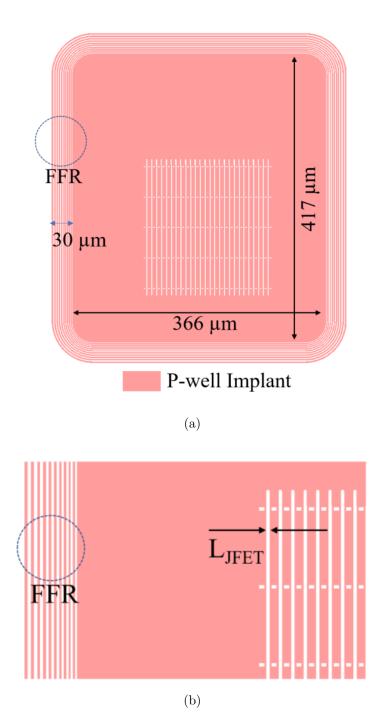

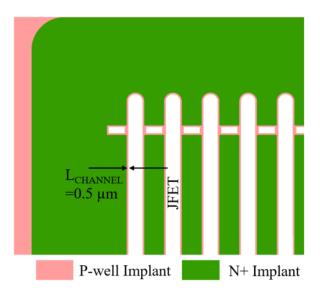

| 3.15 | P-well implant mask.                                                                                                         | 69   |

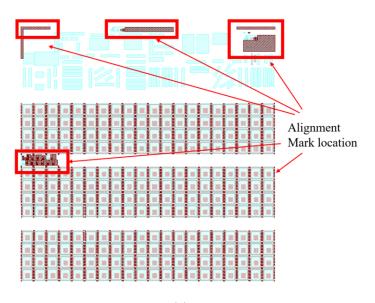

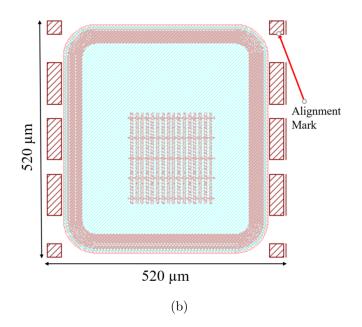

| 3.16 | Alignment mark locations.                                                                                                    | 71   |

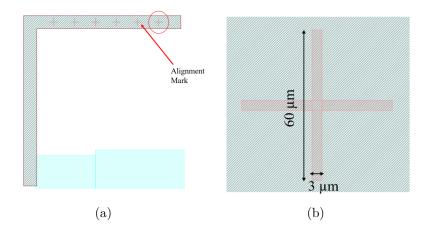

| 3.17 | JEOL JBX 8100FS e-beam or Hiedelberg laser writer registration marks                                                         | 72   |

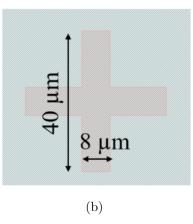

| 3.18 | MJB 3 optical aligner registration mark.                                                                                     | 72   |

| 3.19 | Source implant mask.                                                                                                         | 73   |

| 3.20 | P-well and N-source implant in the tri-gate device showing the channel length.                                               | 74   |

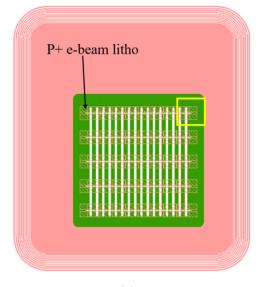

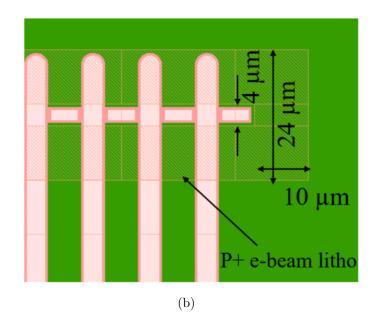

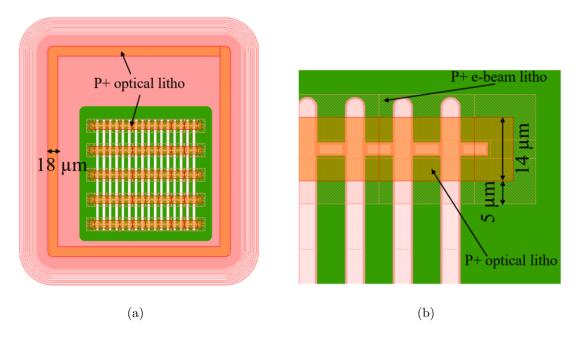

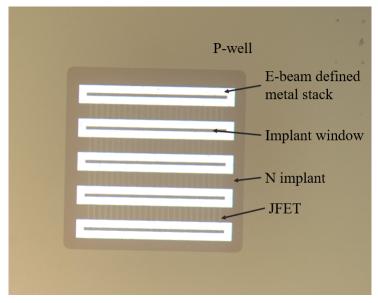

| 3.21 | P <sup>+</sup> implant e-beam lithography                                                                                    | 75   |

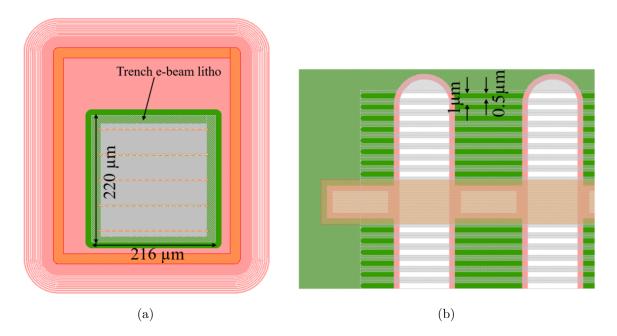

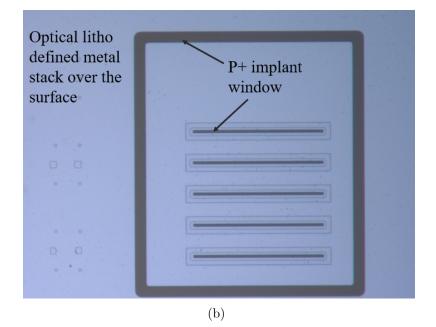

| 3.22 | P <sup>+</sup> implant optical lithography.                                                                                  | 76   |

| 3.23 | $\mathbf{P}^+$ implant one step lithography in the Heidelberg maskless aligner                                               | 77   |

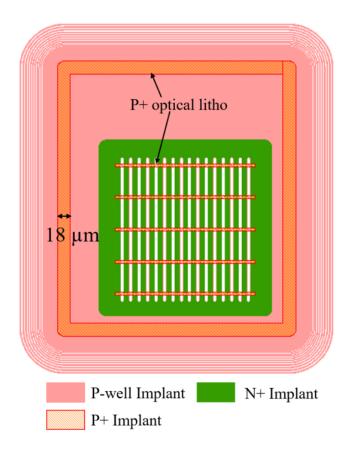

| 3.24 | Trench e-beam lithography.                                                                                                   | 78   |

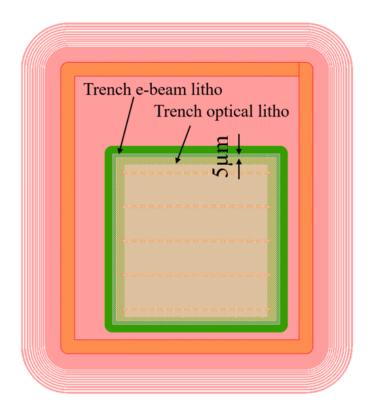

| 3.25 | Trench optical lithography.                                                                                                  | 80   |

| 3.26 | The marked region in the PCM region etches deeper compared to active area due to aspect ratio dependent etching.             | 80   |

| 3.27 | Field oxide optical lithography - blue shaded regions are opened in resist mask to allow a wet chemical oxide etch.          | 81   |

| 3.28 | Gate e-beam lithography.                                                                                                     | 83   |

| 3.29 | Gate optical lithography.                                                                                                    | 84   |

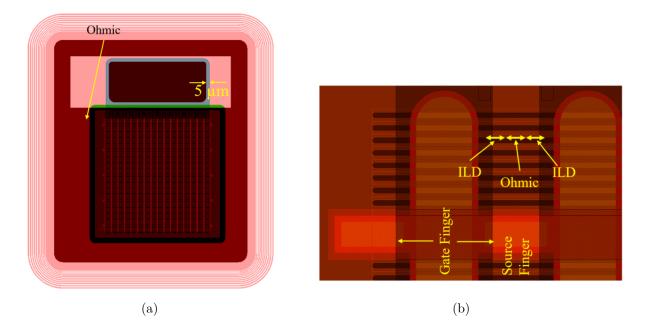

| 3.30 | Ohmic optical lithography.                                                                                                   | 85   |

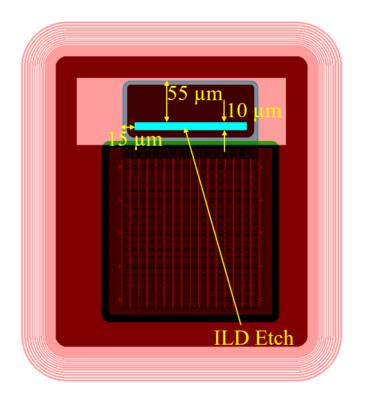

| 3.31 | Inter Layer Dielectric (ILD) optical lithography - blue shaded region is opened<br>in resist mask to allow a dry oxide etch. | 86   |

## Figure

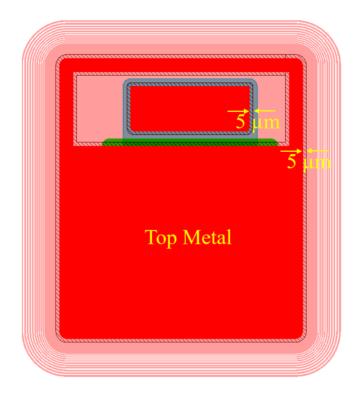

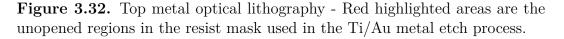

| 3.32 | Top metal optical lithography - Red highlighted areas are the unopened re-<br>gions in the resist mask used in the Ti/Au metal etch process.                                                                                                                                                 | 87   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

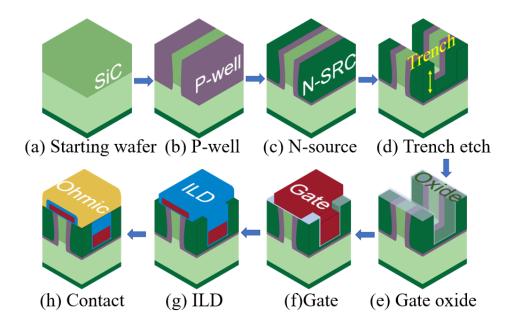

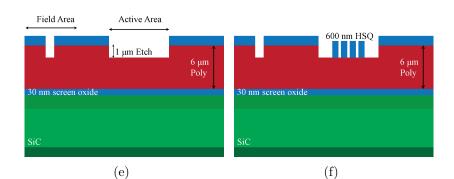

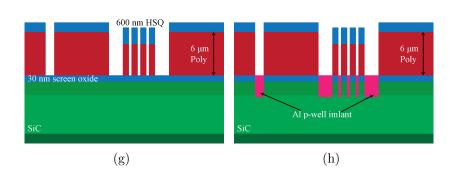

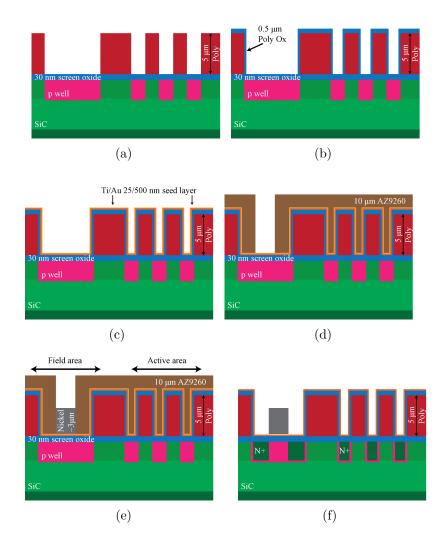

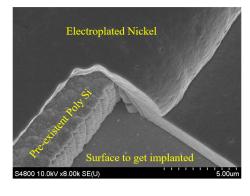

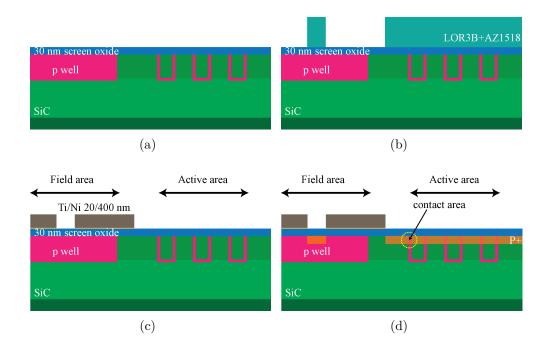

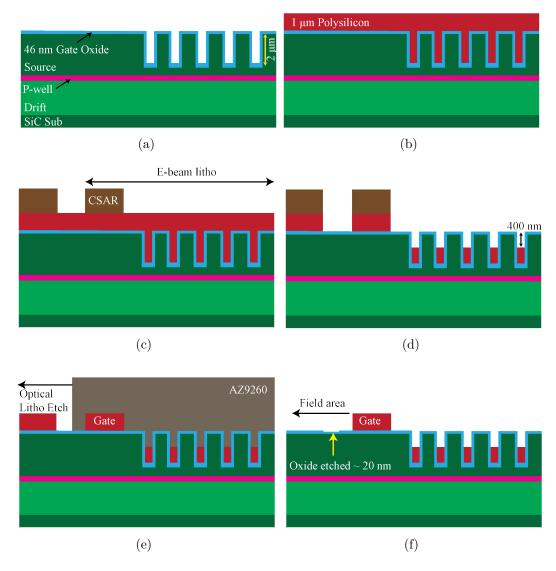

| 4.1  | Major fabrication steps in the tri-gate device fabrication technology                                                                                                                                                                                                                        | 88   |

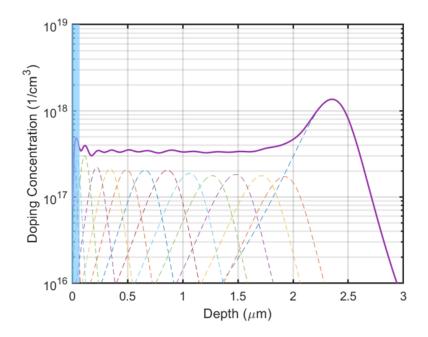

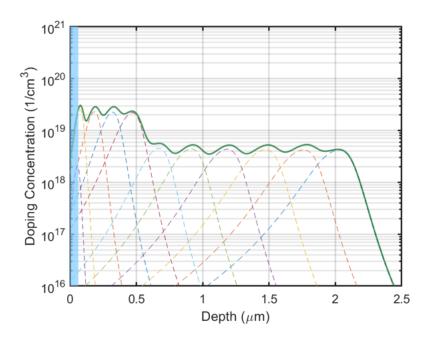

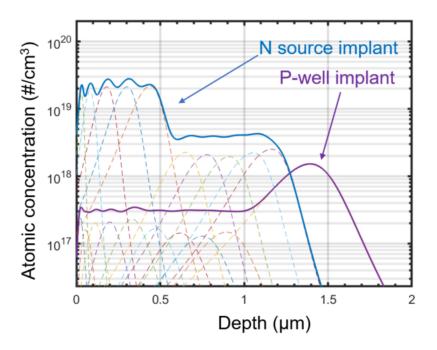

| 4.2  | Aluminum p-well implant profile. The dashed line shows implanted concen-<br>tration at each energy, and solid line shows the total implant concentration.<br>The blue region indicates the screen oxide thickness used during the implant                                                    | 90   |

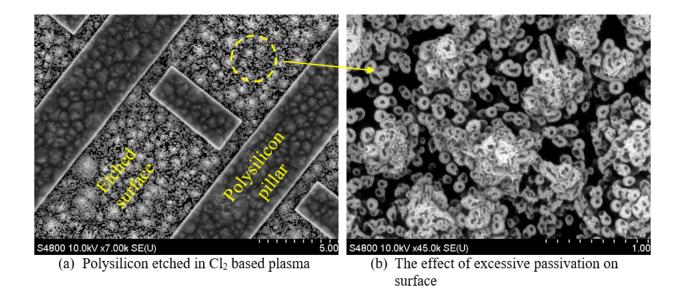

| 4.3  | Polysilicon etch in $Cl_2$ plasma produces excessive surface passivation resulting in micro-masking.                                                                                                                                                                                         | 93   |

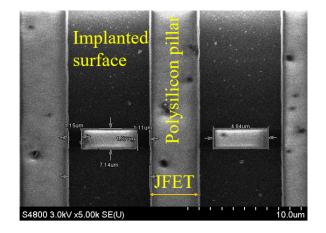

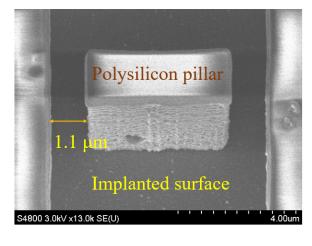

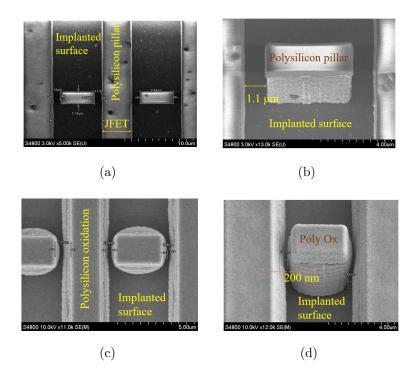

| 4.4  | SEM image of polysilicon patterned as a mask for the p-well implant process.                                                                                                                                                                                                                 | 95   |

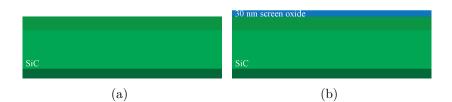

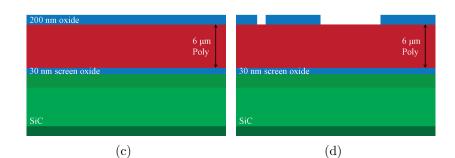

| 4.5  | Aluminum p-well implant process flow - scheme 1                                                                                                                                                                                                                                              | 96   |

| 4.6  | Aluminum p-well implant process flow - scheme 2                                                                                                                                                                                                                                              | 98   |

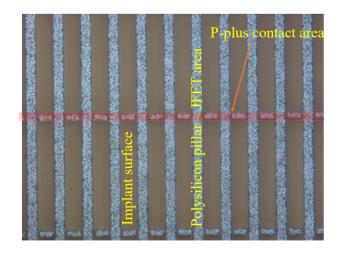

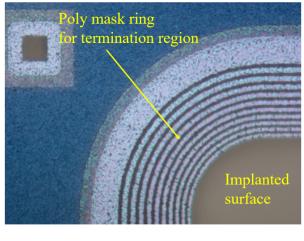

| 4.7  | Optical image of patterned polysilicon in active and termination regions                                                                                                                                                                                                                     | 99   |

| 4.8  | Nitrogen n-source implant profile. The dashed line shows the implanted dopant concentration at each energy, while the solid line shows the total concentration. The blue region near the surface indicates the screen oxide thickness present during the implantation process                | 101  |

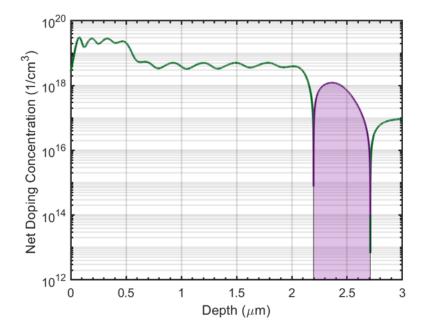

| 4.9  | Net implantation profile from the analytical model. Shaded region highlights the designed dose in the p-well area                                                                                                                                                                            | 102  |

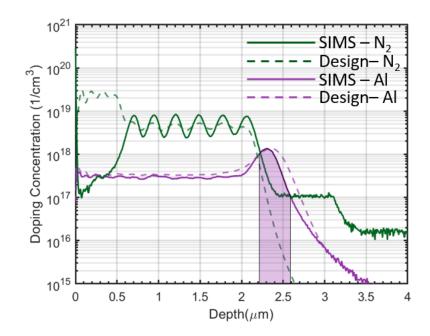

| 4.10 | SIMS analysis on a test sample is shown in the solid line. The dashed line shows the designed profile. The shaded region shows the obtained dose in p-well region                                                                                                                            | 103  |

| 4.11 | N-source implant SEM images.                                                                                                                                                                                                                                                                 | 104  |

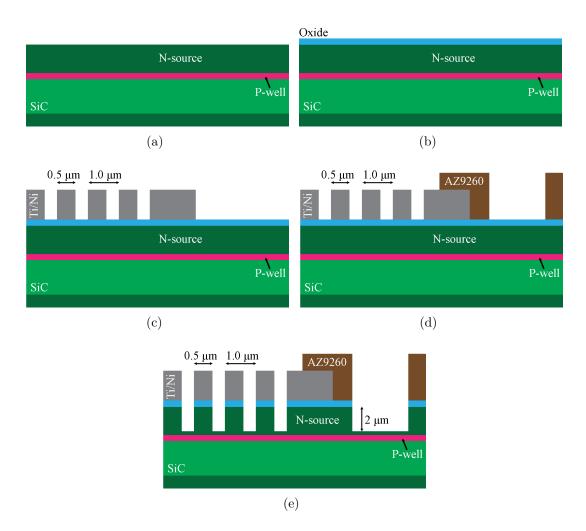

| 4.12 | N-source implant process flow                                                                                                                                                                                                                                                                | 106  |

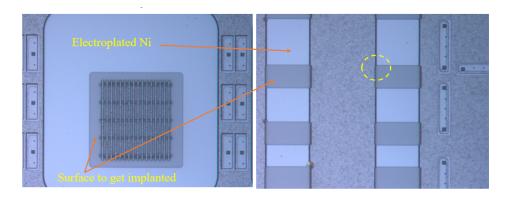

| 4.13 | Image of nickel electrodeposition.                                                                                                                                                                                                                                                           | 107  |

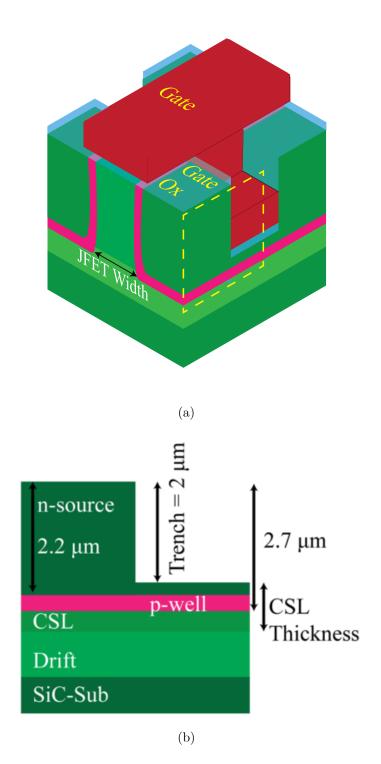

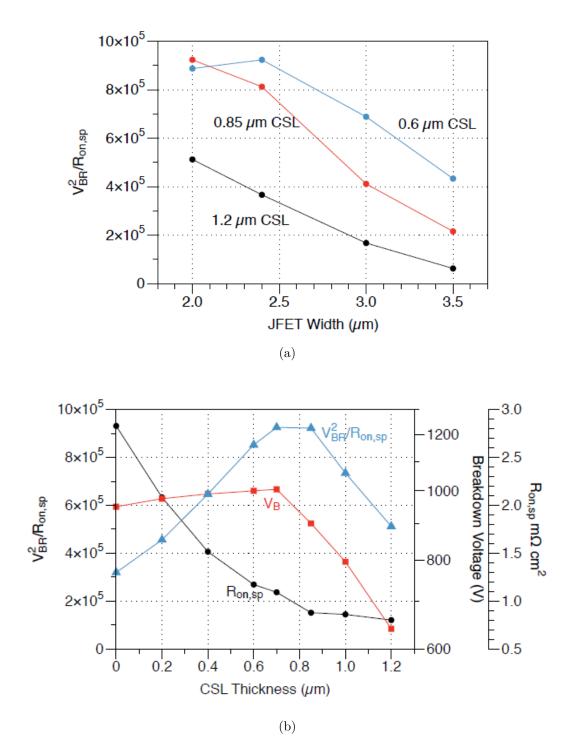

| 4.14 | Impact of CSL thickness on the tri-gate device - Structural dimensions                                                                                                                                                                                                                       | 109  |

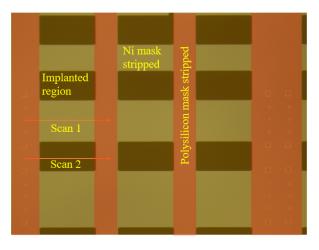

| 4.15 | Impact of CSL thickness on the tri-gate device - Performance                                                                                                                                                                                                                                 | 110  |

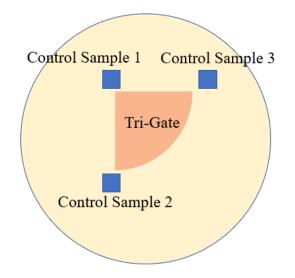

| 4.16 | Tri-gate sample loading strategy for blanket CSL thinning etch with small SiC control samples                                                                                                                                                                                                | 111  |

| 4.17 | Implant swelling after p-well and n-source implants prior to the implant anneal                                                                                                                                                                                                              | .113 |

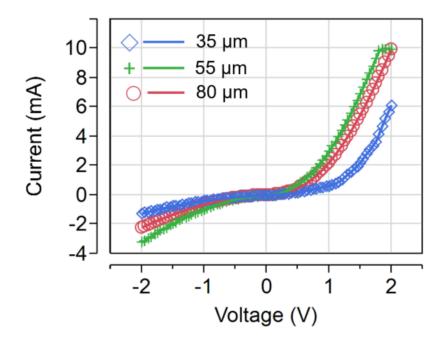

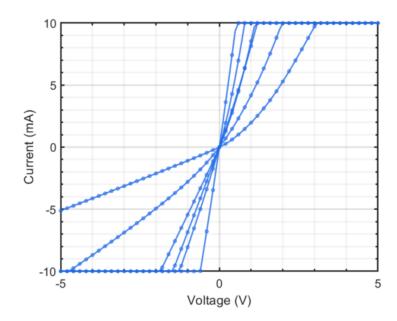

| 4.18 | I-V data on a P+ TLM pattern with pad spacings of 35 $\mu m,$ 55 $\mu m,$ and 80 $\mu m$                                                                                                                                                                                                     | .114 |

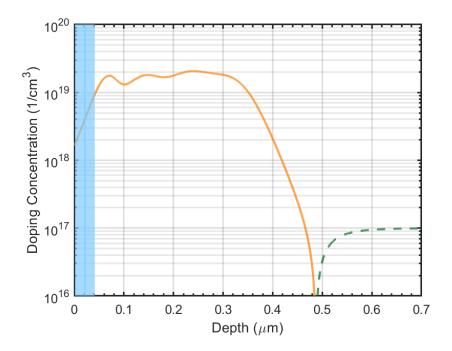

| 4.19 | Net implantation profile in the $p^+$ base contact region. The orange solid<br>line is the implanted aluminium concentration, and dashed green line is the<br>background n-CSL doping. The shaded blue region highlights the screen oxide<br>present on the surface during the implantation. | 115  |

## Figure

| 4.20 | Base contact $p^+$ implant                                                                                                                                                                                                                                 | 117 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

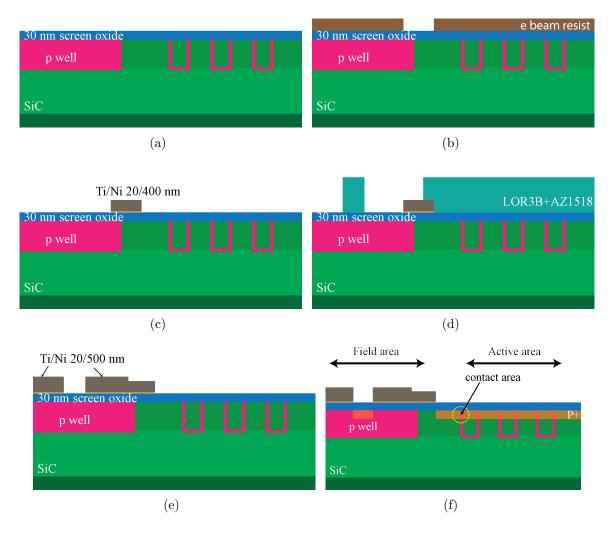

| 4.21 | Base contact P <sup>+</sup> implant formation                                                                                                                                                                                                              | 118 |

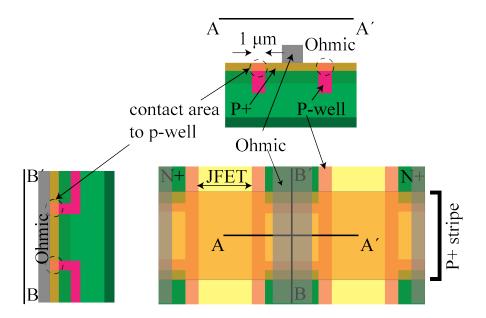

| 4.22 | Base contact P <sup>+</sup> implantation and cross-section views of showing formation of contact                                                                                                                                                           | 118 |

| 4.23 | $p^+$ base contact aluminum implant process flow 1                                                                                                                                                                                                         | 120 |

| 4.24 | $p^+$ base contact aluminum implant process flow 1                                                                                                                                                                                                         | 121 |

| 4.25 | Aluminum P <sup>+</sup> implant process flow 2                                                                                                                                                                                                             | 122 |

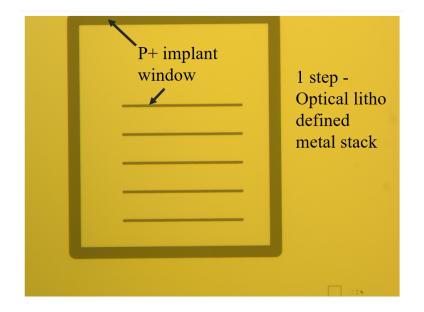

| 4.26 | Base contact implant mask Ti/Ni (10/400 nm) liftoff in the 1 step optical lithography.                                                                                                                                                                     | 123 |

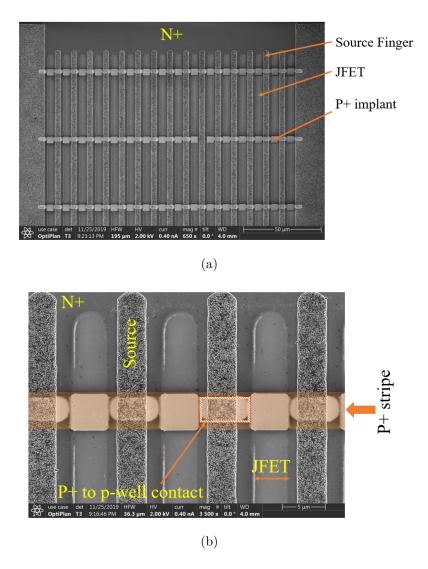

| 4.27 | SEM images showing the p+ implant contact area in a finished device. $\ldots$                                                                                                                                                                              | 124 |

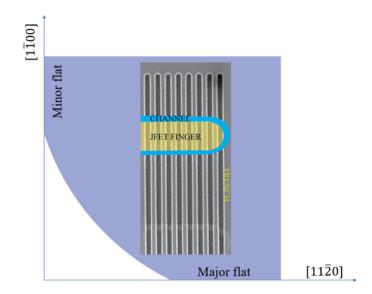

| 4.28 | The orientation of the trench and gate runners in the tri-gate MOSFET with respect to wafer flats and crystallographic directions.                                                                                                                         | 126 |

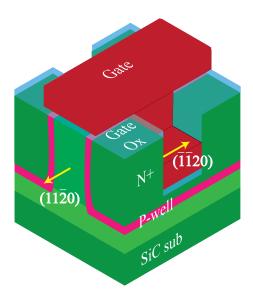

| 4.29 | Isometeric diagram of tri-gate device showing the directions of exposed sidewalls                                                                                                                                                                          | 127 |

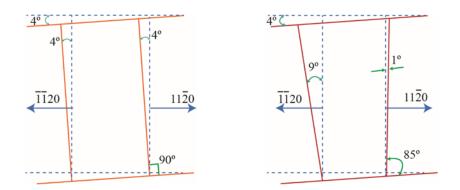

| 4.30 | Deviation of trench sidewalls with respect to principal crystallographic direc-<br>tions on a 4° off-cut wafer                                                                                                                                             | 128 |

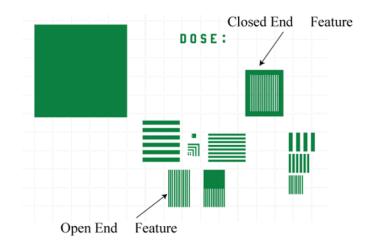

| 4.31 | Mask layout template for test SiC sample trench etch                                                                                                                                                                                                       | 129 |

| 4.32 | SEM image of trench etch process applied to a SiC test sample with the mask layout shown in 4.31                                                                                                                                                           | 131 |

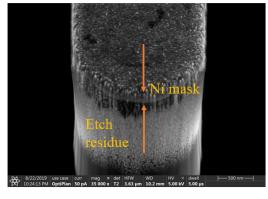

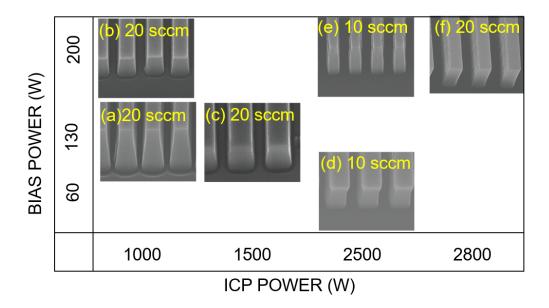

| 4.33 | Results of a SiC etch study using an $SF_6$ plasma at a pressure of 5 mTorr<br>with 10 or 20 sccm flow as mentioned in the image. All etches were done<br>in an Oxford PlasmaPro 100 ICP-RIE system at Notre Dame University's<br>nanofabrication facility | 133 |

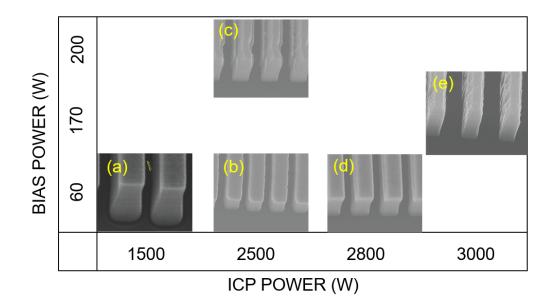

| 4.34 | Results of a SiC study using an $SF_6/Ar$ (10/20 sccm) plasma at a pressure of 5 mTorr. All etches were done in an Oxford PlasmaPro 100 ICP-RIE system.                                                                                                    | 134 |

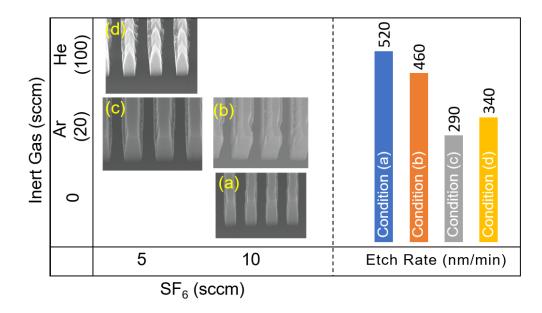

| 4.35 | Results of a SiC etch study using $SF_6$ and inert gas plasma at 5 mtorr pressure and 2500/200 W ICP/bias power. All etches were done in an Oxford PlasmaPro 100 ICP-RIE system.                                                                           | 135 |

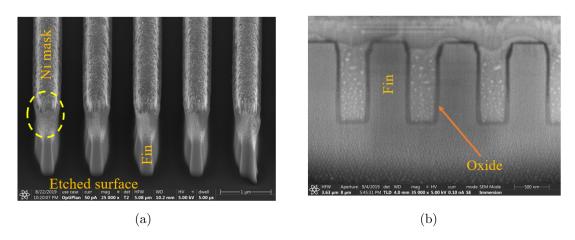

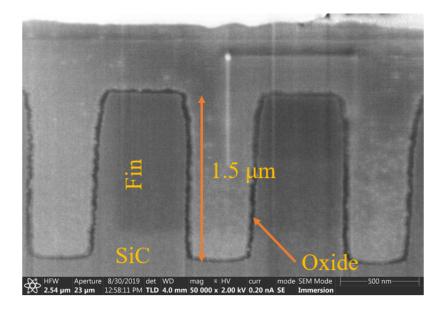

| 4.36 | Cross-section SEM image of the trench etch process in a test SiC sample etched with the parameters listed in Table 4.8                                                                                                                                     | 137 |

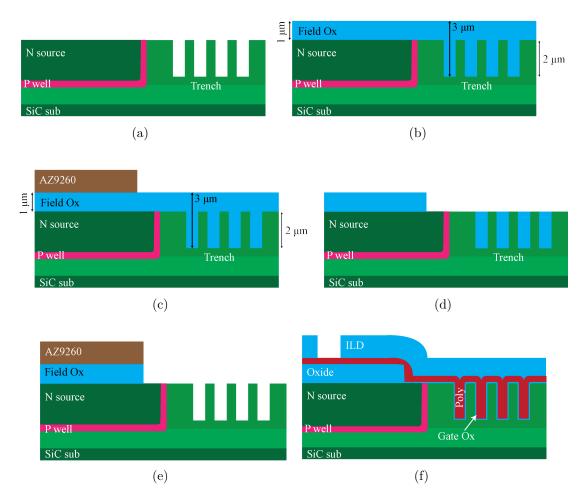

| 4.37 | Trench etch proess flow.                                                                                                                                                                                                                                   | 139 |

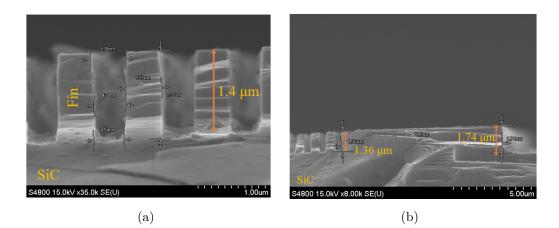

| 4.38 | Cross-section FIB image of the trench profile in the 4Q2 tri-gate sample                                                                                                                                                                                   | 140 |

| 4.39 | Field oxide process flow.                                                                                                                                                                                                                                  | 142 |

| 4.40 | Field oxide process concern.                                                                                                                                                                                                                               | 144 |

| Page |

|------|

|------|

| 4.41 | Wet etch of thick oxide with Photoresist mask shows oxide undercut                                                                                                           | 145 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.42 | Tri-gate device with and without field oxide.                                                                                                                                | 146 |

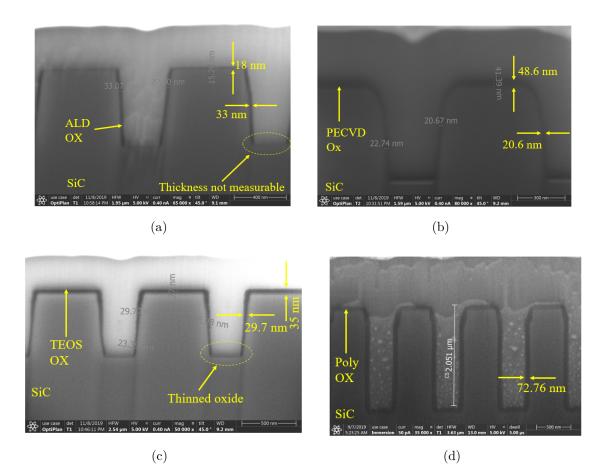

| 4.43 | Different oxide deposition techniques                                                                                                                                        | 148 |

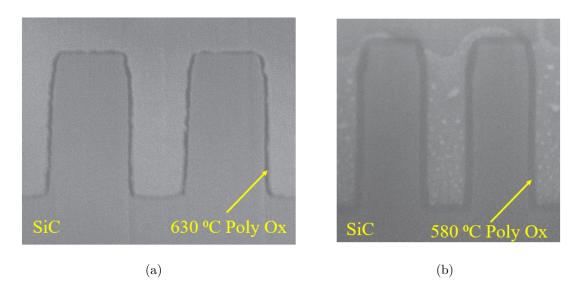

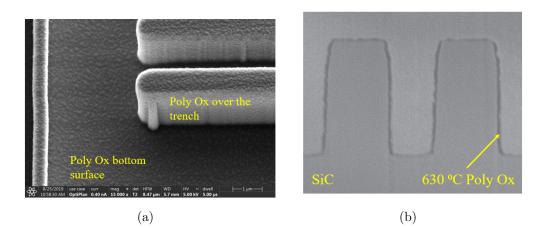

| 4.44 | SEM images of oxidized polysilicon, with the poly deposited at different temperatures.                                                                                       | 150 |

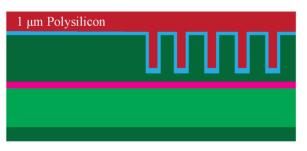

| 4.45 | SEM cross-section of trench structures with 630°C and 580°C poly deposition and 1100°C wet oxidation.                                                                        | 151 |

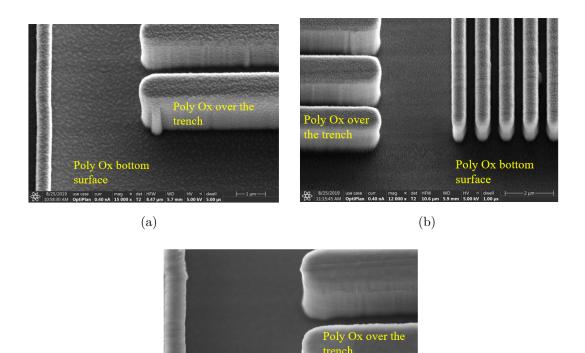

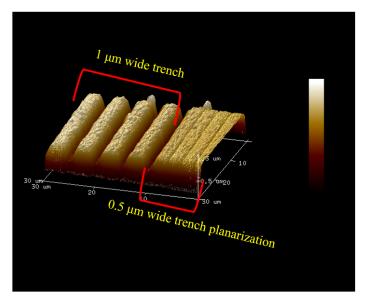

| 4.46 | AFM and SEM images of polysilicon deposited over trench features in a test sample.                                                                                           | 153 |

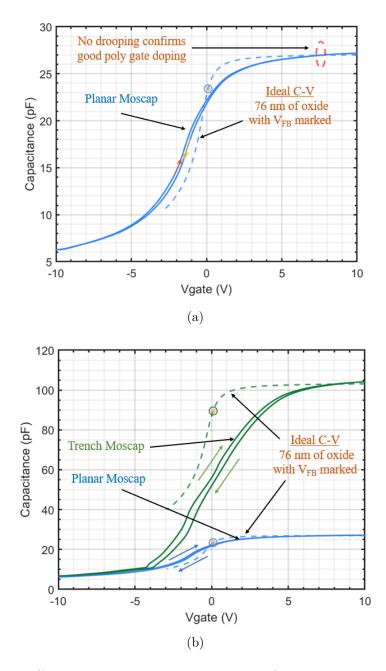

| 4.47 | C-V measurements on a test sample from the PU431D3 wafer showing no drooping in the accumulation capacitance at high gate voltages, confirming good polysilicon gate doping. | 156 |

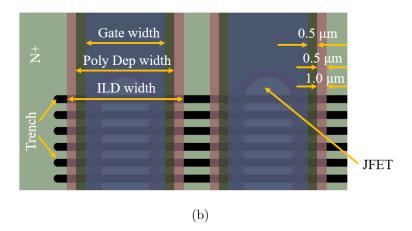

| 4.48 | Mask layout showing the dimensions of the deposited polysilicon, ILD, and final gate.                                                                                        | 158 |

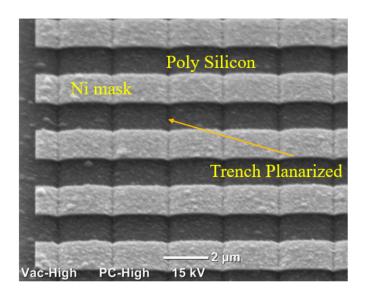

| 4.49 | SEM images on tri-gate 4Q2 sample showing the increased lateral oxidation during ILD formation.                                                                              | 159 |

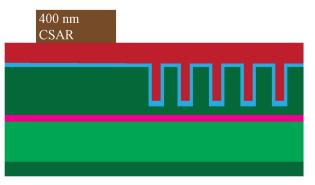

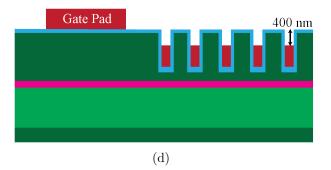

| 4.50 | The process flows illustrated in Fig. 4.51 and 4.52 are shown along the A-A' cross section                                                                                   | 161 |

| 4.51 | Polysilicon gate pattern process flow.                                                                                                                                       | 162 |

| 4.52 | Polysilicon gate pattern process flow – 2                                                                                                                                    | 163 |

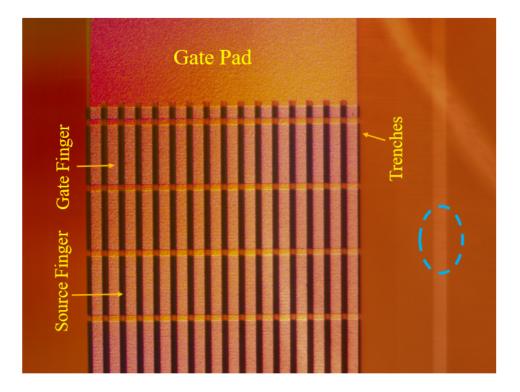

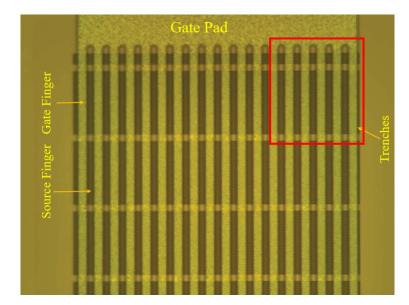

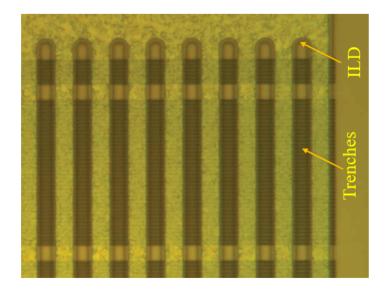

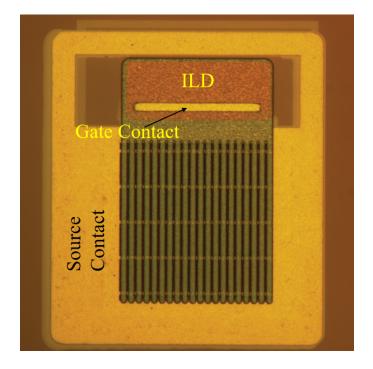

| 4.53 | Optical image after polysilicon gate patterning. Dashed blue highlighted re-<br>gion is the thinned down oxide region due to overlap between lithography<br>steps.           | 164 |

| 4.54 | Optical image after 1 µm ILD growth.                                                                                                                                         | 165 |

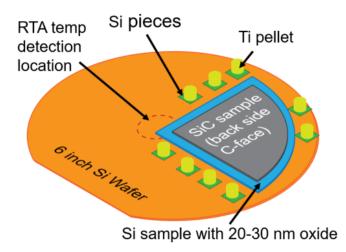

|      | Wafer arrangement in the Jipelec RTA tool during ohmic contact anneal                                                                                                        | 167 |

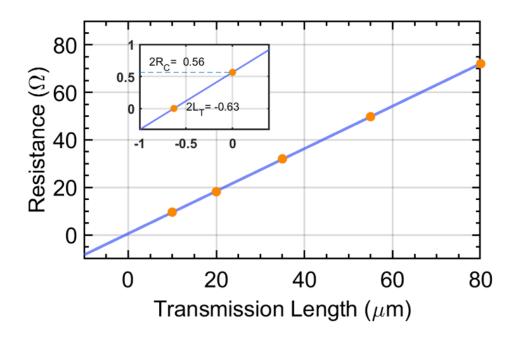

| 4.56 | N <sup>+</sup> TLM measurement on the 4Q2 sample                                                                                                                             | 169 |

| 4.57 | Optical microscopy image of the sample after ILD etch                                                                                                                        | 171 |

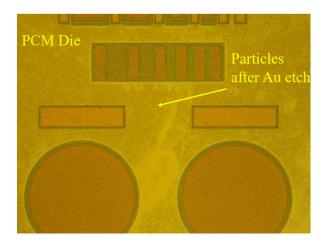

| 4.58 | Gold particles covering the surface after the Au etch. These are removed during the subsequent Ti etch                                                                       | 173 |

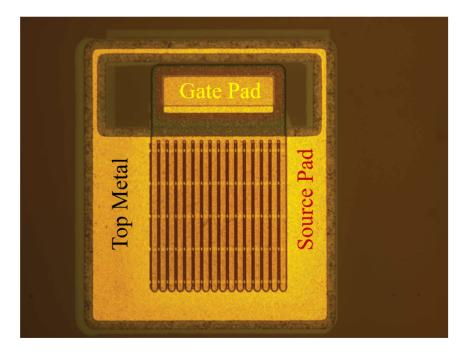

| 4.59 | Optical microscopy image of the top metal after deposition and patterning                                                                                                    | 174 |

| 5.1  | Polysilicon layer deposited at 630°C and oxidized at 1100°C in a wet ambient.                                                                                                | 176 |

| 5.2  | I-V characteristics of a tri-gate device on sample 4Q2                                                                                                                       | 178 |

| 5.3  | ILD breakdown test on sample 4Q2.                                                                                                                                            | 179 |

## Figure

| 5.4  | FIB image of a planar MOSCAP on sample 4Q2 near the ILD etch window mask. Image was taken to ensure the presence of ILD after bad wet chemical BOE etch | 179 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.5  | MOSCAP leakage on the 4Q2 tri-gate sample.                                                                                                              | 180 |

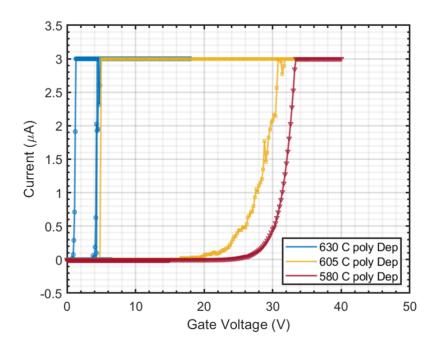

| 5.6  | Polysilicon gate oxide breakdown measurement of the devices listed in                                                                                   | 181 |

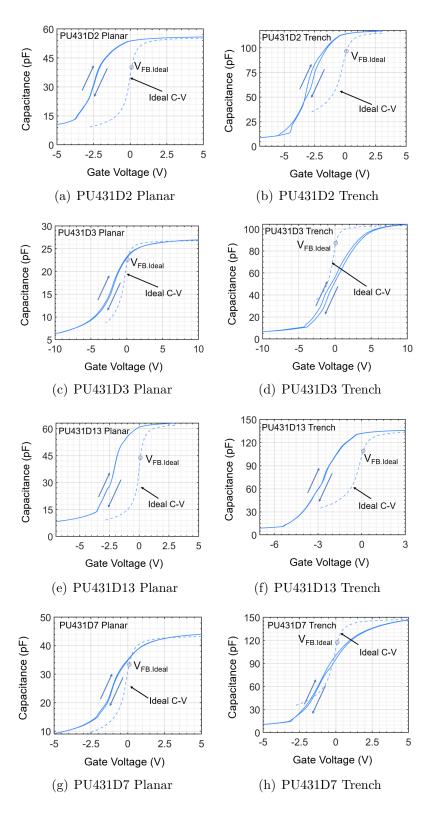

| 5.7  | C-V measurements on both planar and trench MOSCAPs from the experiment                                                                                  | 183 |

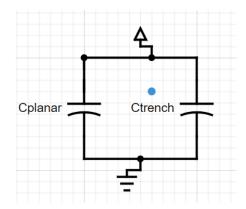

| 5.8  | Equivalent capacitance network.                                                                                                                         | 184 |

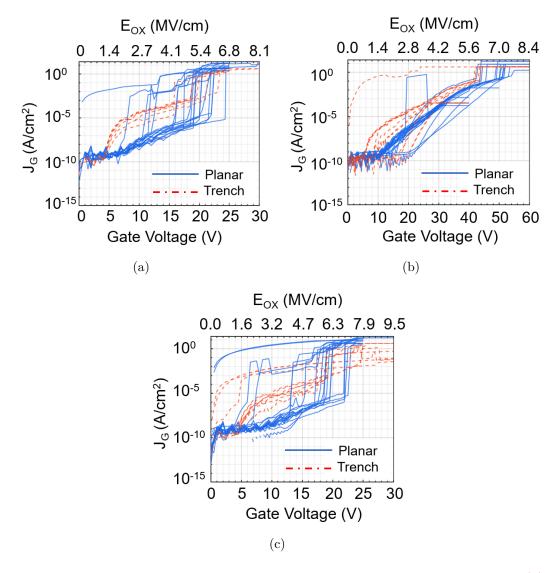

| 5.9  | Gate oxide leakage measurements on fabricated MOSCAPs                                                                                                   | 186 |

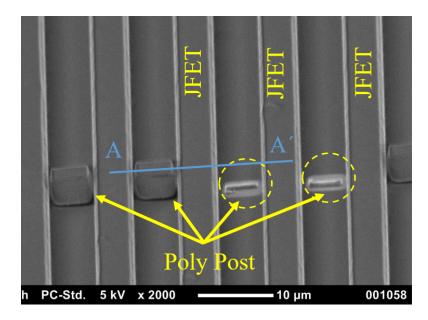

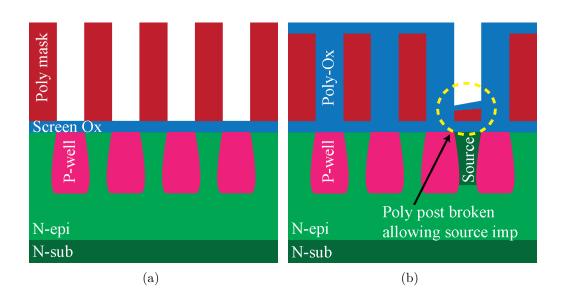

| 5.10 | Polysilicon post breakage before n-source implantation on sample 4Q2                                                                                    | 188 |

| 5.11 | Process flow showing effect of damaged polysilicon posts during implantation.                                                                           | 189 |

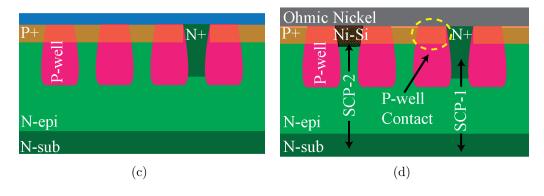

| 5.12 | Suggested alternative implantation process flow to avoid drain-to-source shorts due to damaged p-well implant mask posts.                               | 190 |

| 5.13 | Typical IV characteristics from sample 2Q4.                                                                                                             | 191 |

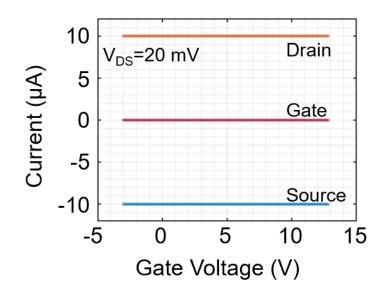

| 5.14 | Electrical testing for possible field inversion: Test connections and I-V char-<br>acteristics                                                          | 193 |

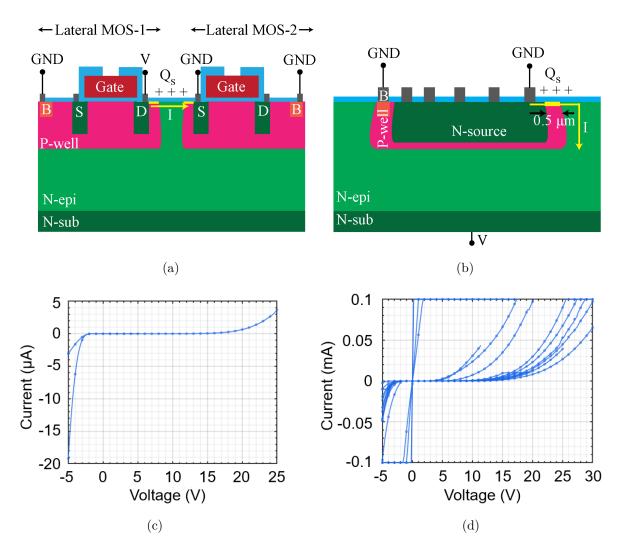

| 5.15 | Polysilicon masked implantation Monte-Carlo process simulation with various implant tilt angles.                                                        | 195 |

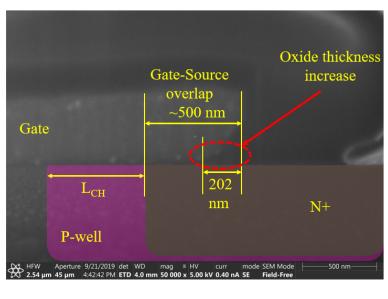

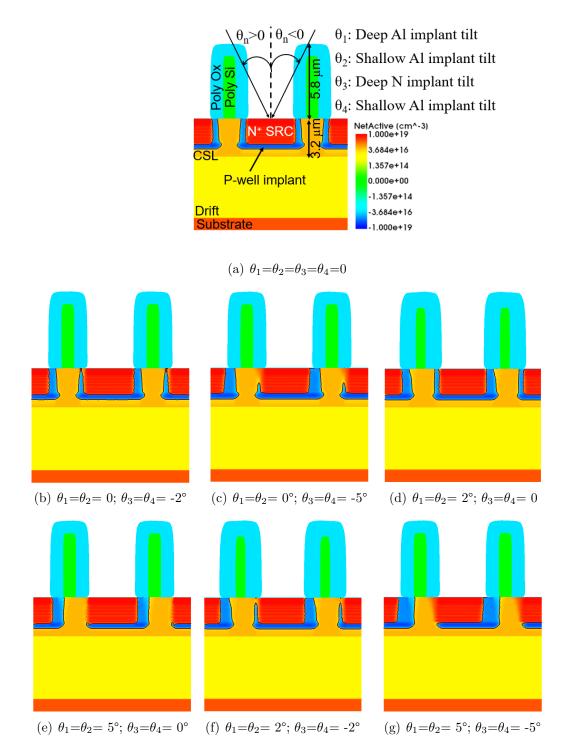

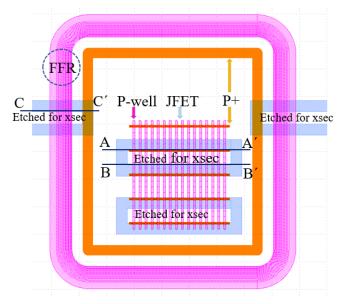

| 5.16 | Top SEM image of channel after anneal and shallow surface etch.                                                                                         | 197 |

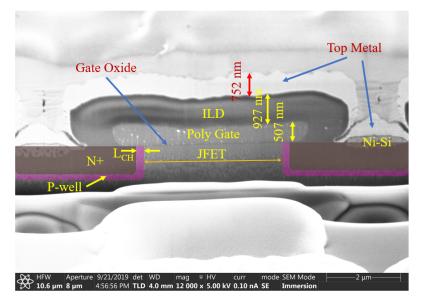

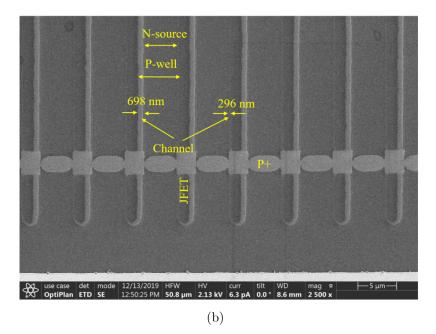

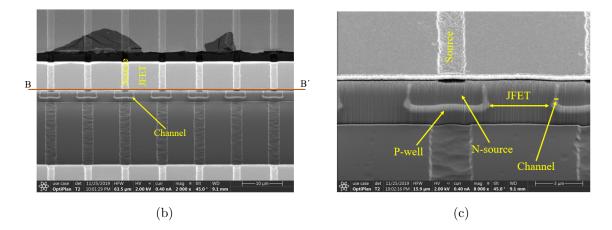

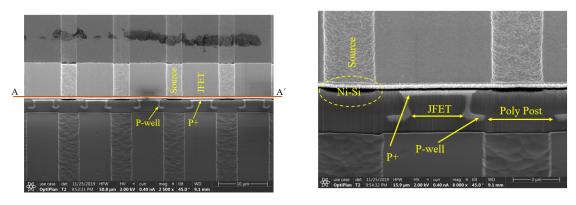

| 5.17 | Cross-section SEM images of the channel region in sample 4Q2.                                                                                           | 199 |

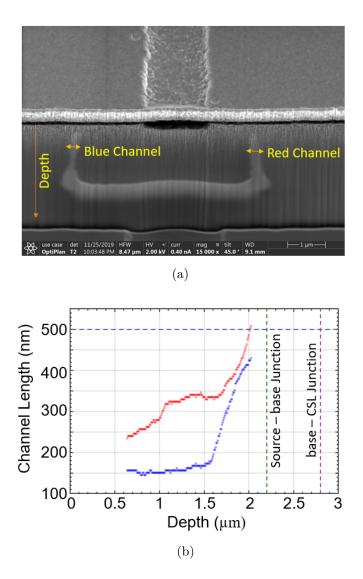

| 5.18 | Cross-section SEM image of channel in 4Q2 tri-gate sample                                                                                               | 200 |

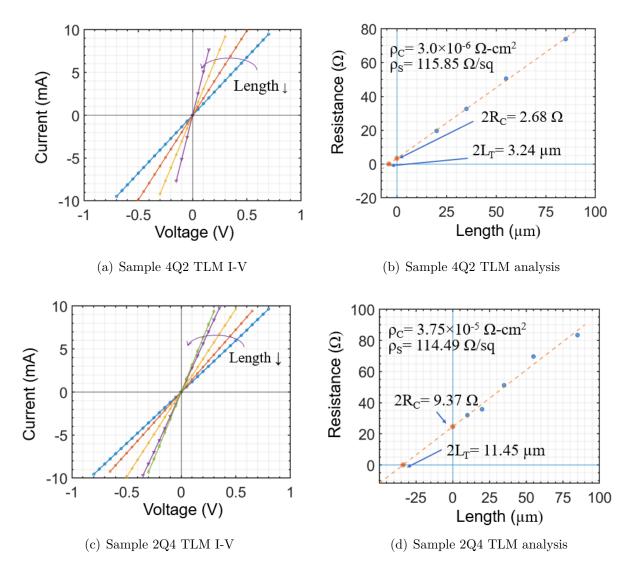

| 5.19 | TLM measurements on samples 4Q2 and 2Q4                                                                                                                 | 202 |

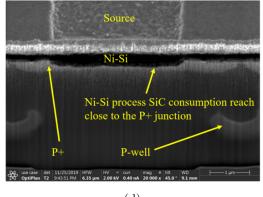

| 5.20 | Cross-section SEM image of the P+ contact stripes on sample 4Q2                                                                                         | 204 |

| 5.21 | I-V characteristics of the P+ to n-CSL diode showing the source of the short circuit path                                                               | 205 |

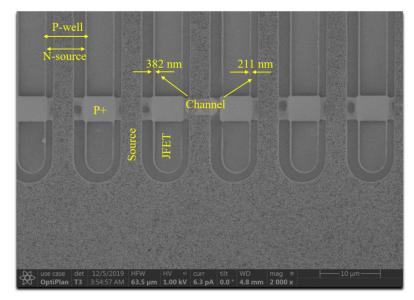

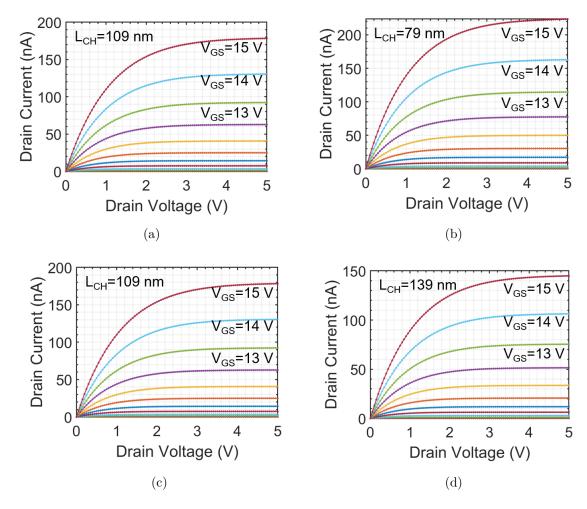

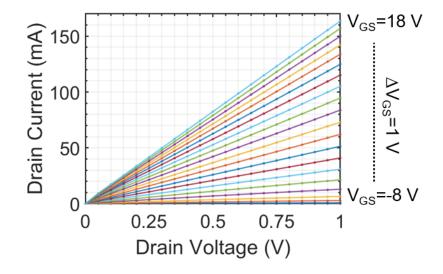

| 5.22 | Output characteristics of lateral planar MOSFETs in sample 2Q4                                                                                          | 206 |

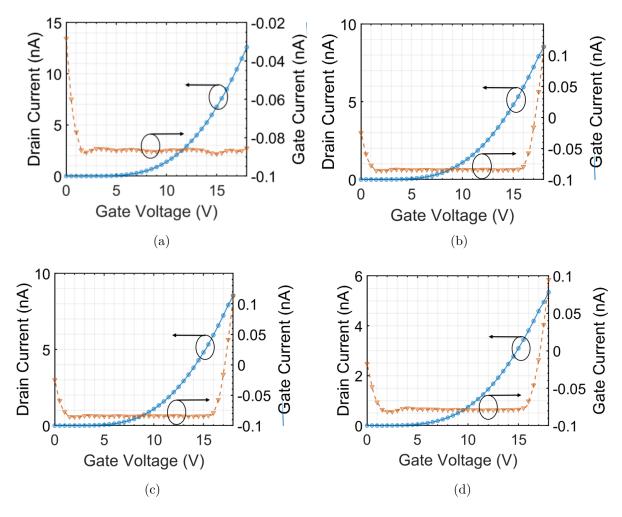

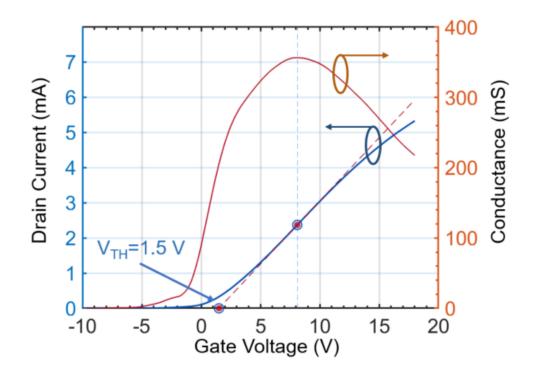

| 5.23 | Transfer characteristics of lateral planar MOSFETs in sample 2Q4                                                                                        | 207 |

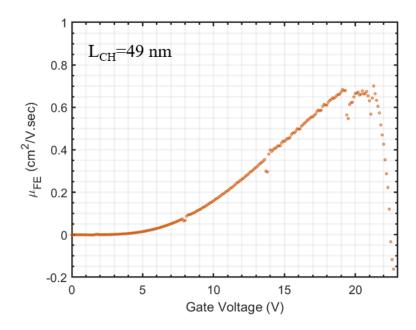

| 5.24 | Field effect mobility of lateral planar MOSFETs in the PCM region of sample 2Q4.                                                                        | 208 |

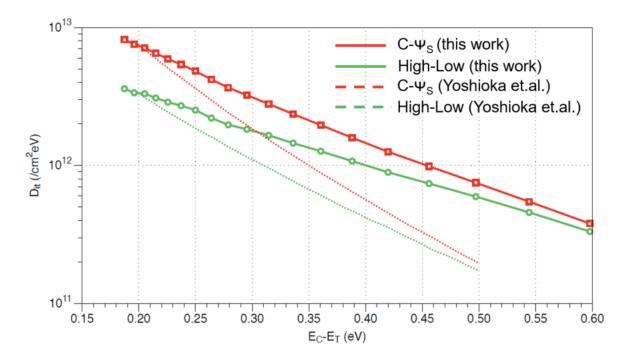

| 5.25 | Interface trap density measurement on MOSCAP fabrication on the CSL layer in sample 2Q4 which is compared with the data reported in [49]                | 209 |

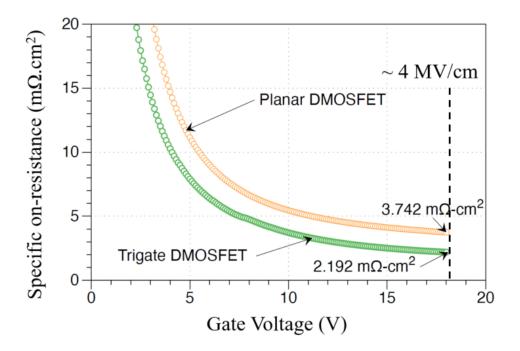

| 6.1  | Output characteristics of a Gen-2 400Q1 tri-gate device.                                                                                                | 212 |

| 6.2  | Transfer characteristics of a Gen-2 400Q1 tri-gate device                                                                                               | 213 |

| Figu | re                                                                         | Page |

|------|----------------------------------------------------------------------------|------|

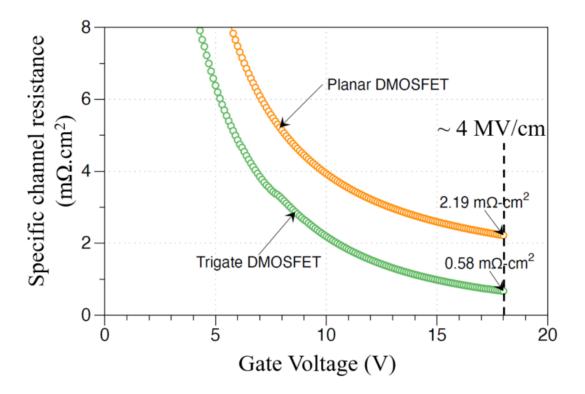

| 6.3  | Specific on-resistance of Gen-2 400Q1 sample.                              | 213  |

| 6.4  | Specific on-resistance of Gen-2 400Q1 sample.                              | 214  |

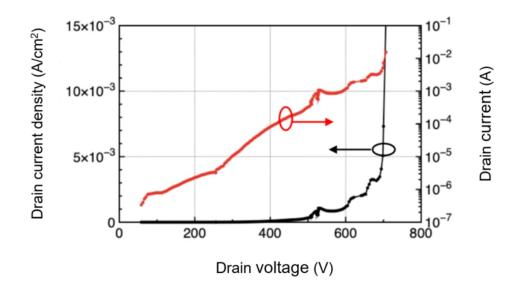

| 6.5  | Off-state leakage and breakdown voltage of a Gen-2 device on sample 400Q1. | 215  |

| B.1  | Gen-2 tri-gate implant design.                                             | 246  |

| B.2  | Gen-2 tri-gate: Sidewall direction variation.                              | 247  |

| B.3  | Gen-2 tri-gate: Die map                                                    | 248  |

### ABSTRACT

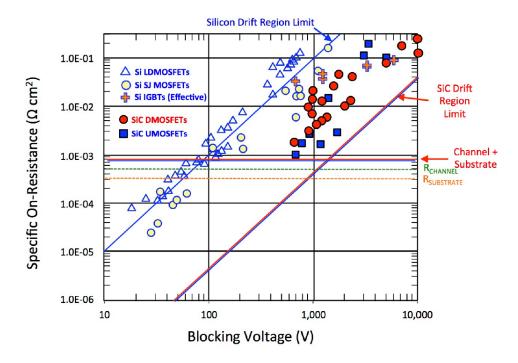

Advances in power electronic systems, especially those in hybrid and electric automobiles and renewable power generation systems, demand high blocking voltage, fast switching performance and low thermal budget from power semiconductor devices. State-of-the-art, silicon based power semiconductor devices are limited by material properties in meeting these demands. Due to the relatively low critical electric field, the on-resistance of the devices is high, and increases significantly with blocking voltage. As a result, current silicon (Si) power MOSFETs rated at above 600 V suffer from unacceptably high conduction losses. Innovative designs, such as the insulated gate bipolar transistor (IGBT), have been developed which use conductivity modulation through the injection of minority carriers to reduce on-resistance. But the involvement of minority carriers gives rise to stored charge and a turn-off delay, dramatically increasing switching losses compared to unipolar devices. Silicon carbide (SiC), a wide band gap semiconductor provides an alternative to Si, and offers a 7x higher electric field strength, 2x higher saturation velocity, and 3x higher thermal conductivity. A thinner, more heavily doped drift region is required for a SiC power device for a particular voltage, which reduces on-resistance and power consumption. However, the channel resistance of SiC metal oxide semiconductor field effect transistors (MOSFETs) is high due to the poor quality of the dielectric-semiconductor interface. Thus the SiC MOSFET fails to live up to the full promise of the material. Minimization of the channel resistance is essential, especially for applications requiring blocking voltages under 1 kV, where this component dominates others. In this work, a novel tri-gate SiC MOSFET is proposed to address this issue. This new structure utilizes both the conventional horizontal surface as well as the sidewalls of a trench to increase the effective width of the channel without increasing the device area. With proper optimization, it should be possible to achieve 3x lower specific on-resistance compared to current SiC unipolar power devices.

### 1. INTRODUCTION

Silicon – the element which has had perhaps the most widespread impact on the human race in the last century – when combined with the ubiquitous element carbon, gives rise to an intriguing compound material, silicon carbide (SiC). It is a wide band gap semiconductor, and offers the potential of high performance, high efficiency power electronic devices with robust thermal stability. While state-of-the-art silicon power devices are reaching their theoretical limits of performance [1], SiC has its own material and technological constraints which will be addressed, and a proposal will be made to meet these challenges.

This thesis has been organized into six chapters. A brief introduction to power electronics and the motivation to use SiC in fabricating power devices will be presented in this chapter. Progress and challenges in SiC power semiconductor devices, along with a proposal for improving device performance will be provided in chapter 2. The mask layout and design architecture of the proposed novel device is described in chapter 3, and in chapter 4, the detailed fabrication and processing steps to build the device are discussed. The device characterization is discussed in chapter 5, and finally in chapter 6, the future work will be suggested and conclusions will be drawn.

#### 1.1 Power Semiconductor Devices

In general, power electronics is a field which involves electrical energy flow regulation and conversion using power semiconductor devices. The concept is so integrated in our day-today life, from comfort to necessity, that it is often taken for granted. Imagine the cell phone – almost everyone carries one in his pocket. It is operated by a battery where electrical energy is added and managed by chargers and regulators. The omnipresence of power electronics is reflected from the data presented by International Energy Agency (IEA) in 2014, where it says that electricity comprises 20% of the total energy consumed on this planet, and is the second highest after oil related power consumption at 40% [2].

The building block of such electronics is the power semiconductor device. The continuous progress and development of these devices is not just a luxury, but a requirement for ever growing technology. Since the early days, after discovering the semiconductor p-n junction operating principle in 1940, silicon has been the material of choice in the fabrication of these devices, based on its performance, availability and cost. It opened the door for the electronic revolution which we are still harnessing. Even now, power semiconductor devices are dominated by silicon. But unfortunately, nothing is indestructible, and so neither is the element - silicon. The demand in technology is pushing to a regime where the material is reaching its theoretical limits. The need of high blocking voltage applications, superior switching performance, and robustness in operation make wide band gap semiconductors a viable alternative to silicon. Among the wide band gap semiconductors, the most popular for power devices are – silicon carbide (SiC), gallium nitride (GaN), diamond (a crystalline form of carbon), and gallium oxide (GaO). Silicon carbide currently presents the best opportunity due to recent advances in high quality wafer growth and process technology [3].

### 1.2 Silicon Carbide

Silicon carbide (SiC) process technology is by far the most mature among the other wide band gap alternatives, and is now beginning to dislodge Si as the preferred semiconductor for power electronics, with the inevitable increase in demand for higher blocking voltages, superior switching performance, better efficiency and reliability. This compound semiconductor, formed in a stoichiometry of equal Si and C, holds many virtues to be the perfect candidate for future power electronics. Some of these inherent physical properties are discussed below, followed by a review of the SiC crystal structure.

SiC is well known for polytypism, the ability to grow the material in different crystallographic configurations, without changing the chemical composition. Polytypes are generally subdivided into two broad groups based on the arrangement of the constituent atoms in the unit cell:  $\beta$ -SiC and  $\alpha$ -SiC.  $\beta$ -SiC is cubic in atomic arrangement while any other arrangements belong to  $\alpha$ -SiC group. One of the most popular polytypes of SiC is 4H-SiC, which is a hexagonal close-packed system in which four Si-C bilayers form the a unit cell along the c-axis. SiC is normally grown by sublimation in a physical vapor transport (PVT) technique at 2000-2800°C [4].

**Figure 1.1.** Hexagonal unit cell in 4H-SiC with important faces highlighted. Typical SiC wafer orientation is also shown

Growth of 4H-SiC during sublimation is controlled by creating a C rich environment with the necessary dopant impurity at 2280°C and 10 Pa pressure [5]. The important faces of the 4H-SiC hexagonal structure is shown in Fig. 1.1. The usual wafer orientation of [0001] Si face is also shown in the figure.

The bandgap of SiC is in the range of 2.36–3.8 eV, depending on the polytype. The most common polytype of SiC for electronic purposes is 4H, mainly because of its high electron and hole bulk mobility, and less mobility anisotropy in different crystallographic directions [4]. This polytype of SiC exhibits a bandgap of 3.26 eV, and the saturation velocity of 4H-SiC at room temperature is  $2 \times 10^7$  cm/s [6], which is almost twice than in Si material. This property is very attractive for high frequency electronic applications. However, for power electronics, the two most important properties this compound material offers is high critical electric field and high thermal conductivity. These useful properties are discussed separately in the following subsections.

### 1.2.1 Critical Electric Field

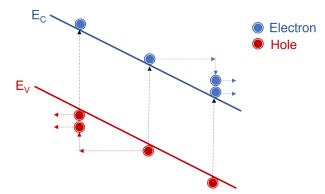

In power semiconductors, the off-state voltage supported by the device is ultimately limited by avalanche breakdown. Mobile carriers, accelerated by the high electric field generated by the applied voltage, can collide with atoms while passing through the drift region. Such collisions may promote electrons from the valence band to the conduction band, generating new electron-hole pairs. These new carriers are again accelerated by the field, and can further collide with other atoms and ionize them as well, in a cascade of such events. Generation of electron-hole pairs in this way is called impact ionization. Under this condition, significant current flows through the device, and catastrophic damage may occur if allowed to continue indefinitely. This avalanche process is described by the impact ionization coefficients for electrons and holes, represented as  $\alpha_n$  and  $\alpha_p$ , respectively. These basic material properties are strong functions of the local electric field, and represent the number of electron-hole pairs generated by a carrier as it traverses a unit distance. If electron-hole pairs are generated at certain distance x from the edge of the depletion region in an abrupt  $P^+$ -N junction, the electron will be swept through the depletion region to the N side, while the hole will traverse to the  $P^+$  side, as shown in Fig. 1.2.

Figure 1.2. Impact ionization at a high electric field showing an energetic electron creating a electron-hole pair

A generated electron or hole will generate  $\alpha_n$  or  $\alpha_p$  additional electron-hole pairs, respectively, while traversing a unit distance. So the total number of electron-hole pairs that will be generated by a specific electron traversing dx distance would be  $\alpha_n dx$  and the total electron-hole pairs that will be generated by a specific hole traversing dx distance would be  $\alpha_p dx$ . Additionally generated electron-hole pairs will participate in further impact ionization events, and the total number of electron-hole pairs due to the generation of one electron-hole pair at distance x from the junction can thus be expressed as

$$M(x) = 1 + \int_{0}^{x} \alpha_n M(x') dx' + \int_{x}^{W} \alpha_p M(x') dx'$$

(1.1)

The solution of this expression can be written as -  $M(x) = M(0) \exp \left[ \int_{0}^{x} (\alpha_n - \alpha_p) dx' \right]$

Where M(0) is the total number of electron-hole pair generated at the edge of the depletion region (x=0).

$$M(0) = \frac{1}{1 - \int_{0}^{W} \alpha_p \exp\left[\int_{0}^{x} (\alpha_n - \alpha_p) dx'\right] dx'}$$

(1.2)

Substituting the expression for M(0) into the solution gives the following expression for M(x)-

$$M(x) = \frac{\exp\left[\int_{0}^{x} (\alpha_n - \alpha_p) dx'\right]}{1 - \int_{0}^{W} \alpha_p \exp\left[\int_{0}^{x} (\alpha_n - \alpha_p) dx'\right] dx'}$$

(1.3)

At avalanche breakdown, defined as the generation of an infinite number of electron-hole pairs, the denominator of the Equation 1.3 becomes 0, which occurs when the following integral is equal to 1.

$$\int_{0}^{W} \alpha_{p} \exp\left[\int_{0}^{x} (\alpha_{n} - \alpha_{p}) dx'\right] dx' = 1$$

(1.4)

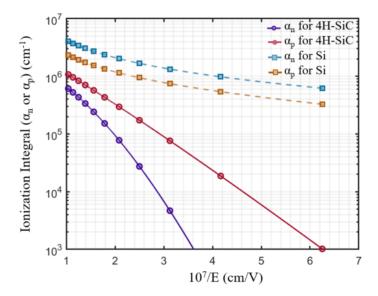

This integral is called the ionization integral for holes, and when combined with a proper impact ionization model for a particular material, it is used in a device simulation to numerically find the critical electric field which results in avalanche breakdown. In general, for a particular electric field, the  $\alpha_n$  and  $\alpha_p$  for SiC are very small compared to Si. These coefficients can be expressed as [7]

$$\alpha_{n.SiC} = 1.69 \times 10^6 \exp\left(\frac{-9.69 \times 10^6}{E}\right)$$

(1.5)

$$\alpha_{p.SiC} = 3.32 \times 10^6 \exp\left(\frac{-1.07 \times 10^7}{E}\right)$$

(1.6)

On the other hand same parameters for Si at room temperature can be expressed as [8]

$$\alpha_{n.Si} = 0.426 \ E \exp\left(\frac{-4.81 \times 10^5}{E}\right)^2 \tag{1.7}$$

$$\alpha_{p.Si} = 0.243 \ E \ e \left(\frac{-6.53 \times 10^5}{E}\right)^2 \tag{1.8}$$

Here the unit of E is in V/cm and the unit of coefficients are in 1/cm.

The impact ionization coefficients for both SiC and Si are plotted in Fig. 1.3.

Figure 1.3. Comparison of the impact ionization coefficients for SiC and Si as a function of inverse electric field, based on equations 1.5 - 1.8

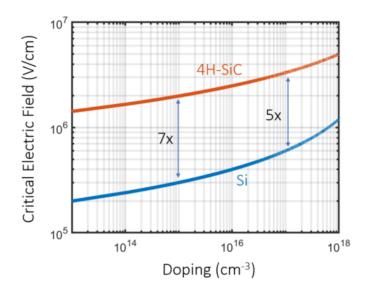

At a certain electric field, known as the critical electric field, the value of theses coefficients are such that the ionization integral approaches 1 (see Equation 1.4). At the onset of this situation, a huge number of electron-hole pairs are generated and material breaks down. Strictly speaking, the critical electric field should be calculated numerically for each specific device structure. However, the critical electric field of SiC and Si at room temperature can be approximated by the following expressions [7]–

$$E_{CR.SiC} = \frac{2.49 \times 10^6}{1 - \frac{1}{4} \log_{10}(N/10^{16})}$$

(1.9)

$$E_{CR.Si} = \frac{4 \times 10^5}{1 - \frac{1}{3} \log_{10}(N/10^{16})}$$

(1.10)

These equations, plotted in Fig. 1.4, are valid for a simple planar, constant doping structure, but are reasonable approximations for other more complex structures as well. It can be easily seen from this figure that the critical electric field of SiC is up to 7x more than Si.

Figure 1.4. Critical electric field of SiC and Si as a function of doping

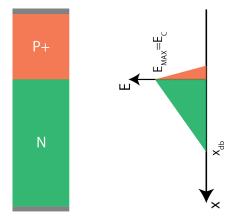

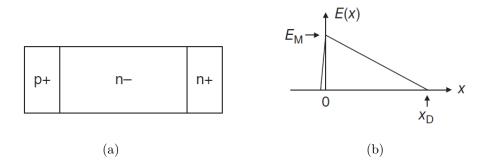

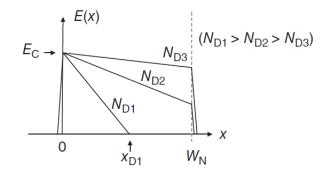

The higher dielectric strength of SiC directly provides an advantage in achieving high blocking voltages. As shown in Fig. 1.5 for a non-punch-through case, the electric field profile is a triangle. At the blocking voltage, the maximum field will be equal to critical electric field,  $E_C$ , and the voltage can be expressed as the area under the triangle (neglecting the voltage drop in the heavily doped P+ region) –

$$V_B = \frac{1}{2} E_C x_{db} \tag{1.11}$$

**Figure 1.5.** Abrupt P<sup>+</sup>-N diode and the electric field profile at blocking voltage in non punch through case

The depletion depth in the N region of permittivity  $\epsilon_S$  and doping  $N_D$ , under blocking voltage  $V_B$ , can be written as –

$$x_{db} = \sqrt{\frac{2\epsilon_s V_B}{qN_D}} \tag{1.12}$$

where q is the charge on an electron. Substituting this expression for  $x_{db}$  in Equation 1.11, the blocking voltage becomes –

$$V_B = \frac{\epsilon_S E_C^2}{2qN_D} \tag{1.13}$$

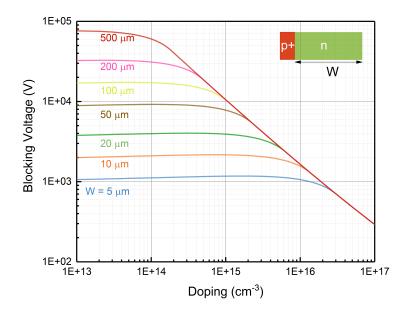

As shown in Equation 1.13, blocking voltage is proportional to the square of the critical electric field. Therefore, since the critical field is  $\approx 7 \times$  higher in SiC than in Si, 50× higher blocking voltage is achievable for a given doping level. Alternatively, to obtaining a certain blocking voltage, SiC can be doped much more heavily than Si, and the drift region can be made much thinner, resulting in significantly reduced on-resistance.

The specific on resistance (defined as the product of resistance and area) of a uniformly doped block of material, can be written as -

$$R_{ON.SP} = \rho x_{db} = \frac{x_{db}}{q\mu_N N_D} \tag{1.14}$$

where  $\mu_N$  is the electron mobility, and full dopant ionization has been assumed. Substituting (1.11) for  $x_{db}$ , and  $N_D$  from (1.13) into (1.14), we arrive at an expression for specific on-resistance–

$$R_{ON.SP} = \frac{4V_B^2}{\mu_N \epsilon_S E_C^3} \tag{1.15}$$

The specific on-resistance of a device is therefore a strong function of critical electric field. This fact gives SiC a clear advantage over Si: Due to the  $7 \times$  higher critical electric field, it offers about  $300 \times$  less resistance for the same blocking voltage.

#### **1.2.2** High Temperature Operation and Thermal Conductivity

The intrinsic carrier concentration is a very sensitive function of temperature. In the case of Si, at about 300°C, this becomes comparable to the semiconductor doping. In this intrinsic state, the device looses its ability to function as intended, imposing a fundamental limit to the temperature of a device while in use. For example, in modern automobile exhaust sensing and control, the ambient temperature exceeds 600 °C. Silicon devices are thus prevented from use in this type of application, due to fundamental material properties.

On the other hand, 4H-SiC, having 3x higher bandgap than Si, offers very low intrinsic carrier concentration. At room temperature this parameter is around  $5 \times 10^{-9}$  cm<sup>-3</sup> [4], which is  $10^{19}$  times lower than Si. As a result, SiC based devices are functional at high temperatures —like 600 °C or even above.

High density power operation and internal power losses cause heat dissipation in the device. For maintaining reliable operation, a complex air or water based cooling system is needed to control the junction temperature. This carries an extra weight to the system and becomes an overhead which may affect the system cost and reliability. Therefore a material like SiC is very attractive, offering high thermal conductivity and thus low thermal resistance, which ensures efficient heat dissipation and reduces—or in some cases eliminates completely—the size and weight of complex cooling system. However, due to gate oxide reliability concerns, MOS-based devices are normally limited to temperatures below 200°C. On the other hand, JFET-based structures which do not rely on gate oxides are able to sustain extended operation above 400 °C [9].

A comparison chart of different power semiconductor materials is shown below -

Figure 1.6. Radar graph of selected material parameters of Si, SiC and GaN

# 2. A NOVEL APPROACH TO SIC POWER SWITCHING DEVICES - THE TRI-GATE MOSFET

#### 2.1 Silicon Carbide MOSFET Applications

Silicon Carbide (SiC) power devices, which have evolved gradually over last 20 years, are now at a stage to shape the power semiconductor industry. The exhibition of high electric field operation, low on-resistance and better thermal transport holds significant promise for the next generation of power semiconductor devices - the second revolution after silicon (Si) [10]. The first SiC power device, a Schottky diode rated at 600 V and 6 A, was introduced to the market by Infineon in 2001, and targeted the automobile industry and power factor correction (PFC) circuitry [11]. Today Wolfspeed fabricates 6 inch diameter SiC wafers with no micropipes (a formerly common yield limiting defect) per square centimeter.

Rohm offers a  $2^{nd}$  generation 650 V and 1200 V planar SiC DMOSFETs, and a  $3^{rd}$  generation trench UMOSFET with similar voltage ratings. The potential applications of such devices are widespread, from the high voltage smart grid to home appliances. SiC devices are now gaining popularity as an alternative to Si counterparts. Due to the higher critical electric field, SiC MOSFETs offer  $5-7\times$  lower specific on-resistance compared to Si MOSFETs. However, the Si IGBT, which uses conductivity modulation, can achieve significantly reduced on-resistance in this voltage range. However, the Si IGBT is a bipolar device, while the MOSFET is a unipolar device, which means it does not exhibit the slow minority carrier recombination process during transitions to the off state, and thus has lower switching losses compared to the IGBT. Thus, the unipolar SiC MOSFET enables higher switching frequencies and lower dynamic losses than Si-IGBTs.

A recent trend in power technology is the move toward to greener options, meaning more environmentally friendly technologies and reduced  $CO_2$  emissions. One example is the development of electric or hybrid vehicles in the automobile industry. Toyota manufactures around two million hybrid or electric vehicles a year, promoting the stand against the greenhouse effect and global warming. These vehicles operate at a drive voltage of 600 V, which requires switching transistors rated at 1200 V where SiC MOSFET devices are superior to state-of-the-art Si devices. Better thermal transport, in addition to superior efficiency and performance, is inherent in SiC devices, which can operate efficiently at as high as 200°C, while Si devices fail below 150°C [12]. This helps to eliminate or reduce cooling mechanisms needed for power devices in harsh environments. This is one of the key features taken into account while using these devices in large data centers with a 380 V distribution scheme, rated at 1200 V [13].

SiC MOSFET devices can also be utilized to design inverters or converters for industrial motor applications and renewable energy generation systems. For example, inverters can be used to convert the DC voltage produced by a photovoltaic array to match the requirements of the synchronous AC grid system. A recent trend in the solar industry is to move toward the higher power ratings and higher system voltages to minimize the cost of inverters and wiring. This then requires power devices with increased voltage ratings. SiC power devices used in the inverter of a photovoltaic system increase the efficiency of the inverter to 97.5%, and reduce inverter losses by 22% compared to Si based devices [12].

The faster switching frequency of SiC MOSFETs can be exploited in the implementation of the smart grid system[14]. This vision of a next generation power grid includes distributed generation sources, and provides for communication between sources to build a resilient and flexible power network [15]. The communication must be done digitally with high bandwidth bidirectional power converters where the associated circuit breakers should act rapidly as per the information - the criteria that can be easily and efficiently met with SiC devices. SiC MOSFET devices, rated at 10 kV, provide the compactness and speed that the smart power grid system demands.

There are many other areas where SiC-based MOSFET devices could be beneficial, including military applications such as electric ships and aircraft, and electric or hybrid combat vehicles [12]. Other possibilities include AC motor controls [16], servo controls, and uninterrupted power supplies, etc. In summary, SiC devices have widespread potential applications, driven by the demand of low power consumption and high voltage operation. Realizing this potential requires significant investment in research and development in both academic and industrial segments.

#### 2.2 SiC MOSFET Status and Prospects

Despite the promise of the SiC MOSFET, it has yet to meet its full potential. For an instance, the poor quality dielectric interface degrades the electron mobility an order of magnitude in the channel compared to the bulk, resulting in higher static loss than desirable. Despite this, the SiC MOSFET already surpasses the performance and efficiency of existing Si power devices for many applications, especially in high voltage applications where device performance is mainly limited by the bulk material resistance, and where the interfacial mobility plays little role. This provides strong motivation to further improve SiC MOSFETs at low to moderate voltage (600-1200 V) applications. In order to do so, it is imperative to address the limitations and current challenges. These key challenges are discussed in the next subsections, followed by a description of the approach adopted in this thesis for device improvement.

#### 2.2.1 Dielectric Interface

One major advantage of SiC over other wide band gap semiconductors is that it can be oxidized to grow a dielectric at the surface. Thermal oxidation at  $1100^{\circ}$ C to  $1300^{\circ}$ C, produces a high quality silicon dioxide (SiO<sub>2</sub>) thin film, when combined with an appropriate passivation technique [4]. The basic reaction which takes place during thermal oxidation can be expressed as-

$$\mathrm{SiC} + \frac{3}{2}\mathrm{O}_2 \to \mathrm{SiO}_2 + \mathrm{CO}$$

Under the proper conditions, SiC is consumed to grow SiO<sub>2</sub>, with carbon (C) diffusing from the structure mainly in the form of carbon monoxide (CO). Of the resulting oxide thickness, 46% is below the original surface, while 54% is above. While the oxidation reaction appears simple at the macroscopic level, at the atomic level the interfacial reaction is far more rich and complex. The process is not yet fully understood, and remains an active area of research. The best mobility recorded in SiC devices, as of today is around 100 cm<sup>2</sup>/(V · s) in the channel [17], which is a factor of 10 less than in the bulk (around 1000 cm<sup>2</sup>/(V · s)). One theory is that some carbon remains in the near interface region, potentially degrading the oxide-semiconductor interface quality. Experimental work has been done to prove this theory by intentionally inducing conditions which result in reduced out gassing of carbon from the interface, resulting in higher trap density [18]. Another theory suggests higher surface density of atoms in SiC, is the source of high density dangling bonds at the interface[19]. In yet another example, oxidation of the compound semiconductor may lead additional phases. One or more of these factors, none fully proven, might contribute to a poor quality SiC/SiO<sub>2</sub> interface. Dangling bonds and excess C at the interface has been illustrated in the Fig. 2.1(a).

**Figure 2.1.** (a) Dangling bonds and abruptness at  $SiC/SiO_2$  interface and (b) The low conduction band offset between SiC and  $SiO_2$  leads to Fowler-Nordheim tunneling

Oxide reliability is also challenging, since SiC, as a wide bandgap semiconductor, exhibits a lower electron affinity than Si, resulting in a smaller conduction band offset between SiO<sub>2</sub> and SiC as shown in the Fig. 2.1(b). The smaller barrier height results in Fowler-Nordheim tunneling at lower oxide fields than in Si, and may lead to undesirable oxide leakage which can cause long term reliability issues like threshold voltage drift instability. Constant research and study are ongoing to better understand the SiC/SiO<sub>2</sub> interface, and hence to develop processes to improve quality. One promising process is post-oxidation annealing in the nitrogen environment, especially in nitric oxide (NO) or nitrous oxide (N<sub>2</sub>O) at up to 1,300°C. The annealing process passivates the surface to create  $4 \times$  lower interface trap density compared with non-annealed thermal oxide, which improves the mobility of the channel interface [20].

Further improvement can be availed in phosphoryl chloride (POCl<sub>3</sub>) annealing at 1000°C for 10 min, which helps to reduce interface state density and thus increases the mobility in the channel [21]. The mobility in the channel at the NO annealed interface is reported as high as 45 cm<sup>2</sup>/(V · s) while annealing in POCl<sub>3</sub> is reported to produce a mobility around 100 cm<sup>2</sup>/(V · s). Despite having higher interfacial mobilities, POCl<sub>3</sub> annealed devices show threshold voltage instabilities which are a major reliability concern. Therefore the NO anneal technique is still the most widely accepted method of improving oxide interface quality in SiC technology.

#### 2.2.2 Design Innovation

Structural innovation and design development is important to optimize the performance and maximize the reliability of devices.

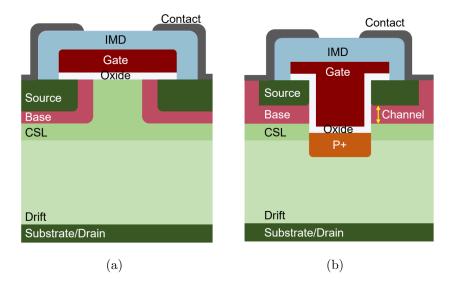

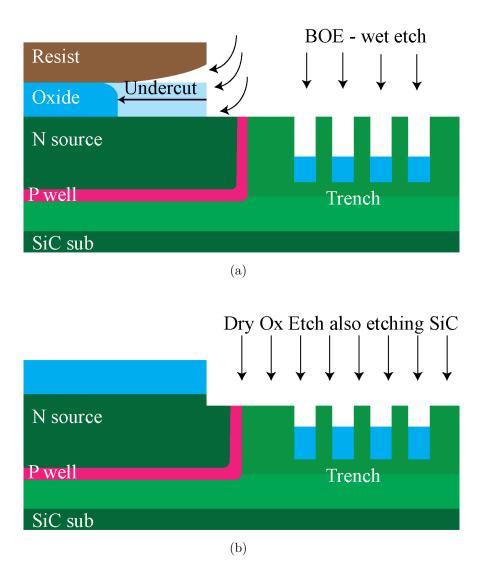

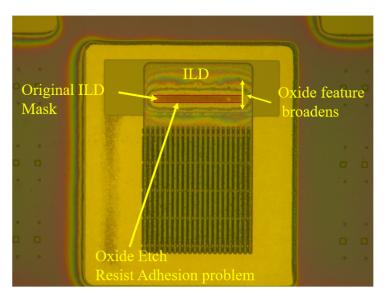

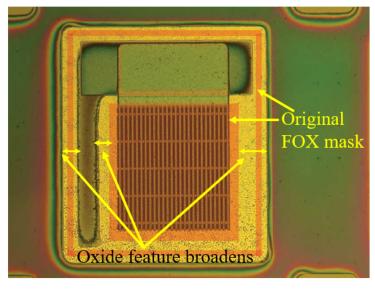

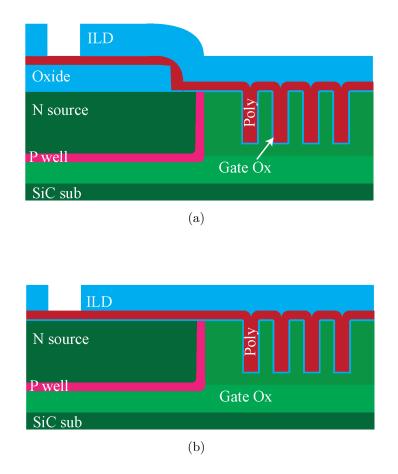

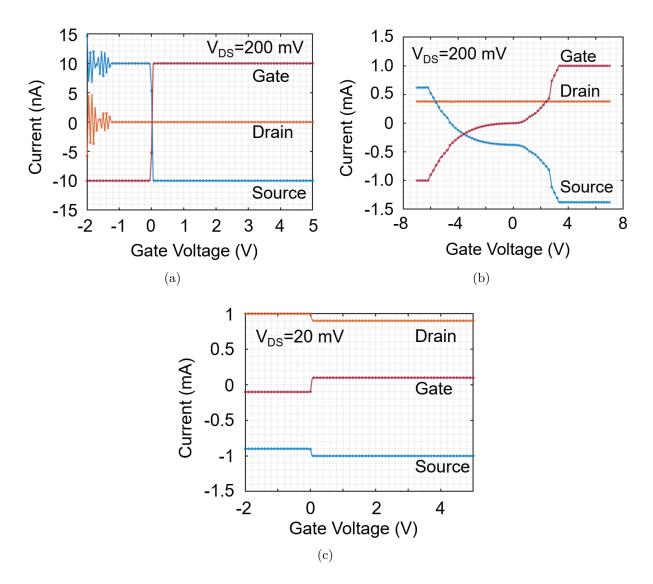

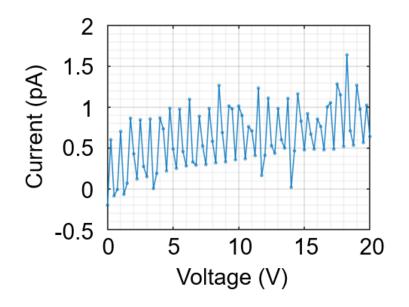

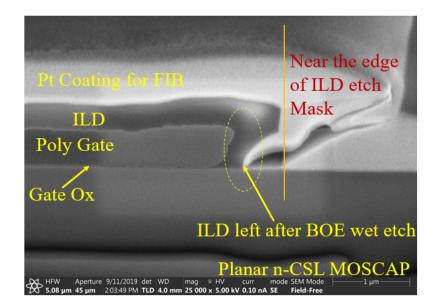

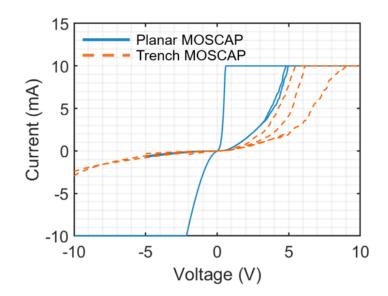

Figure 2.2. Two primary types of SiC MOSFETs: (a) DMOSFET, and (b) UMOSFET.